引言

本篇博客将介绍keil下载程序的过程中,镜像文件将经过哪些硬件,以及简单的介绍他们之间的协议。

一、硬件连接

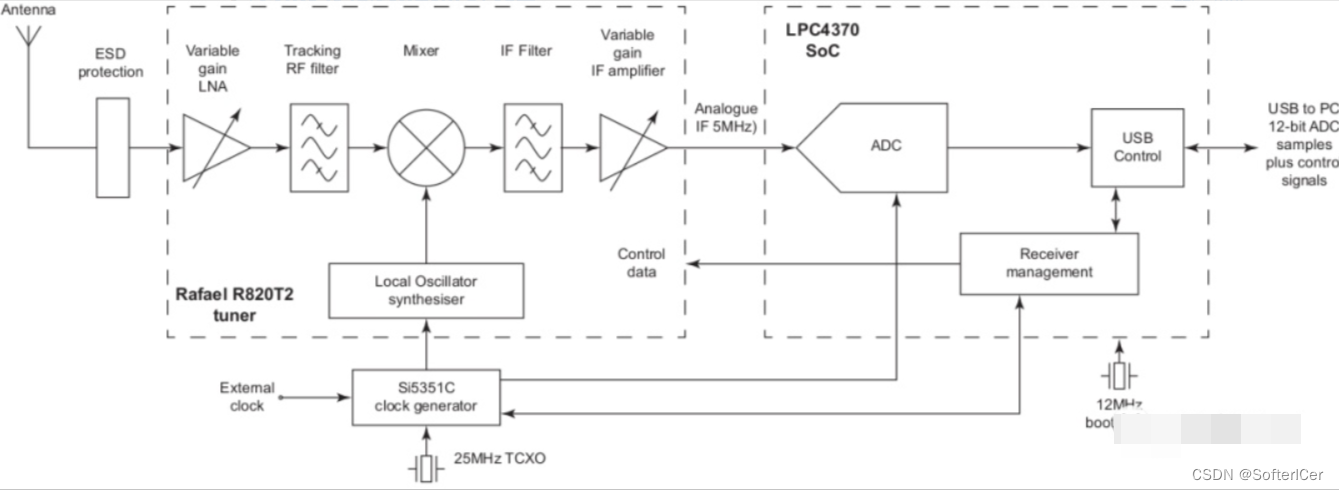

图1 硬件连接

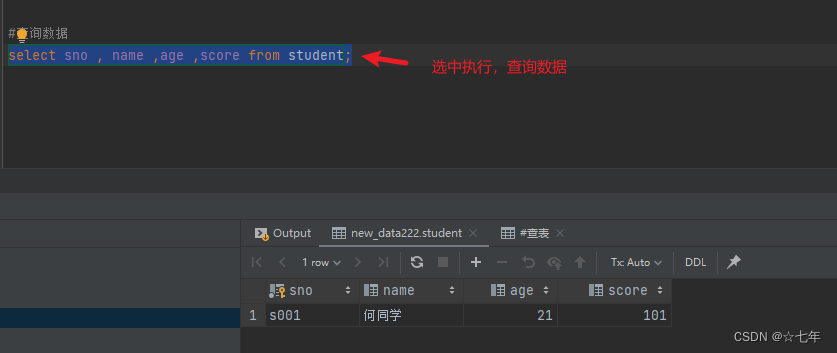

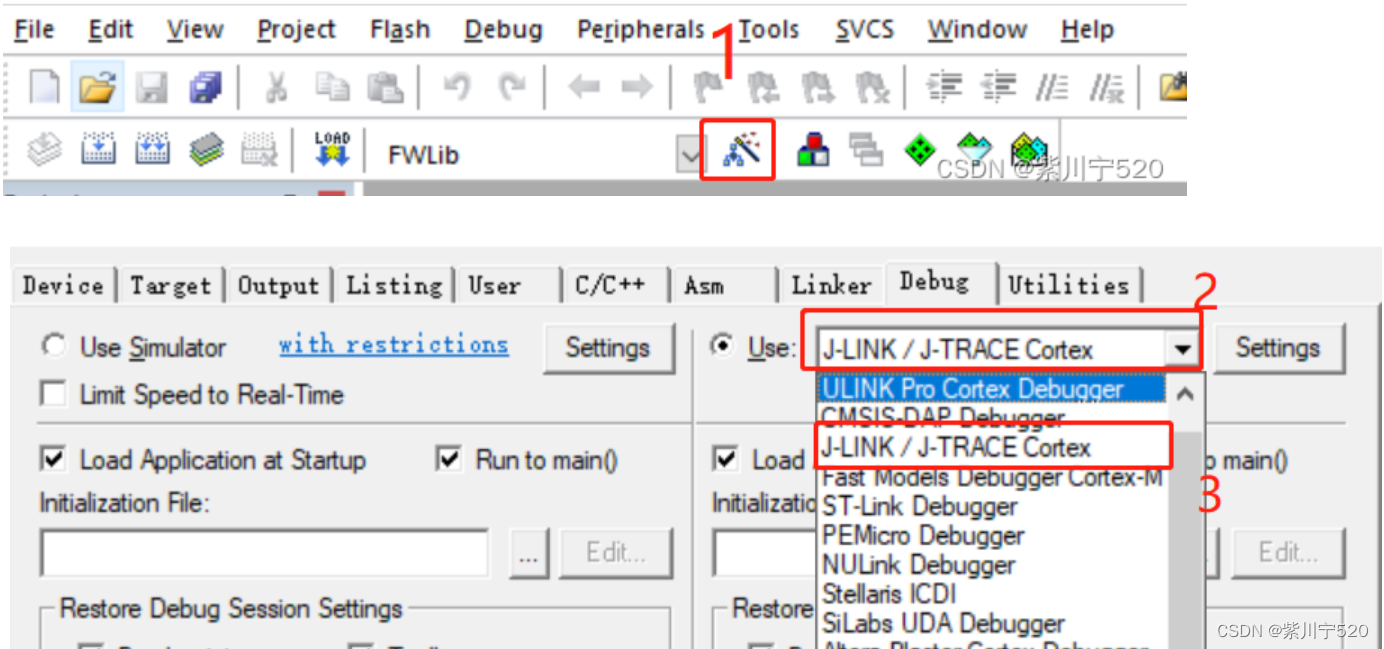

将PC、jlink、芯片使用ubs线、swd线连接好之后,在PC上的keil软件中,我们选择对应的仿真器,并选择下载协议。

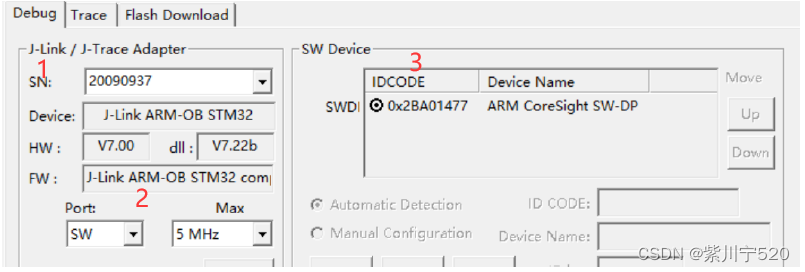

图2 选择仿真器

图3 配置仿真器

在图2中我们选择jlink下载器,在图3中可以看到,jlink的SN为20090937(图2中1)、下载接口是SW接口(图2中2)、芯片端ID为(图2中3)

在图2中3的部分,我们可以看到0x2BA01477,这个是芯片内部SWJ-DP的ID,Device Name下的ARM CoreSight SW-DP是我们用的调试组件名字。CoreSight是ARM公司为了应对SOC中复杂的debug和trace而提出的调试架构,其包含多个组件,我们在keil中进行debug的时候,在keil的各个窗口中看到的数据、断点、单步运行等操作都是由这个架构进行支持。

二、DAP

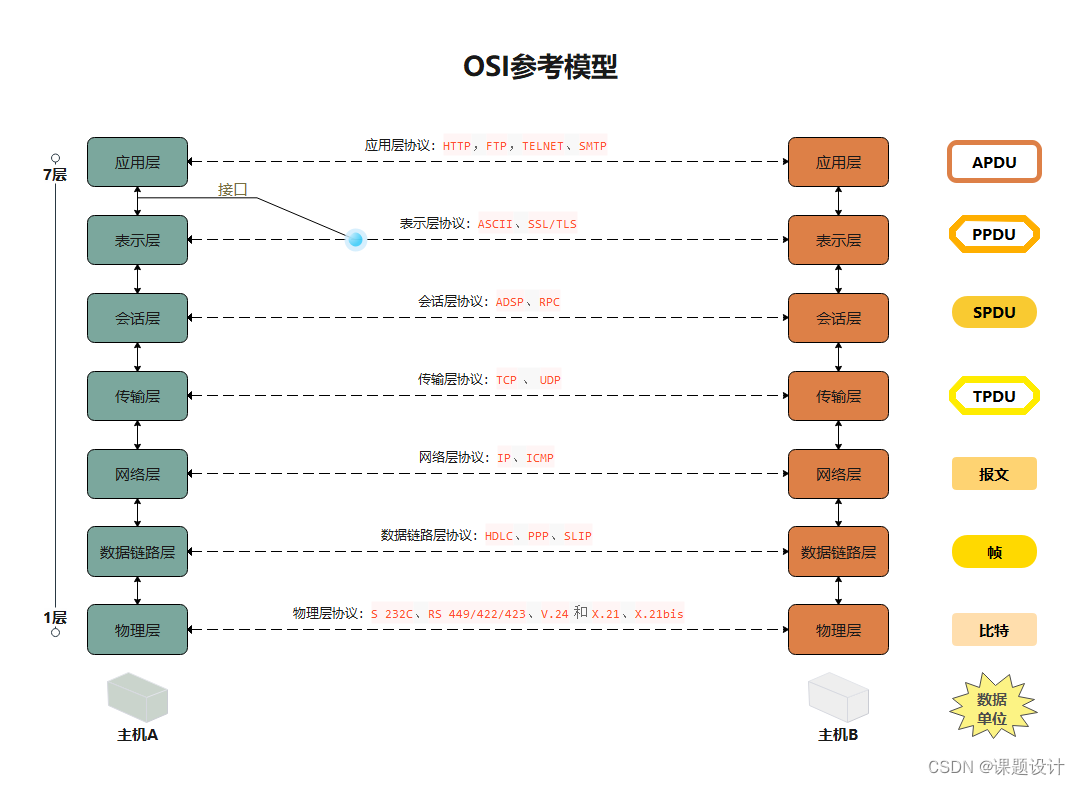

1、SWD协议

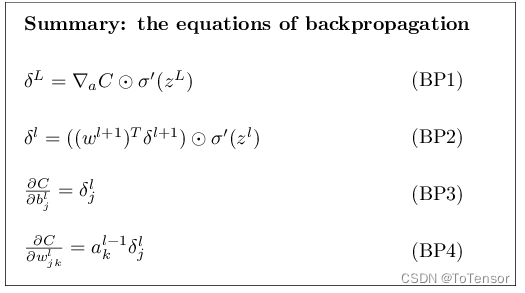

jlink和芯片通过SWD(Serial Wire Debug)接口连接,使用SWD协议。准确的说,SW-DP只支持SW协议,SWJ-DP支持jtag和sw协议,博主用的是sw-dp,所以下文以及后面的文章中如不特殊说明均指的是SW-DP接口。SWD可以通过传输数据包来读写芯片的寄存器。SWD是用于访问ARM调试接口的双线协议。它是ARM调试接口规范(ARM Debug Interface Architecture Specification)的一部分,是JTAG的替代品。SWD的物理层由两条线组成:

SWDIO: 双向数据线

SWCLK: host驱动的时钟线

在图1中我们可以看到,SW-DP通过DAP总线连接AHB-DP。

图4

这一部分就是SWD接口牵扯到的硬件。 通过连接到SWDIO/SWCLK,可以直接访问串行线调试端口(SW-DP)。SW-DP可以访问一个或多个接入端口(AP),通过AP可以访问系统的其余部分寄存器。 Cortex M系列CPU的一个重要AP是AHB-AP,它是内部AHB总线上的主机。换句话说,AHB-AP可以访问内部核心的内存映射。由于内部闪存、SRAM、调试组件和外围设备都是内存映射,因此AHB-AP可以控制整个设备,包括对其进行编程。整个SWD操作过程是分级进行的,时钟信号由SWCLK 管脚输入,数据信号从SWDIO管脚输入输出。首先Debugger对SW-DP进行操作,确定AP寄存器的参数,达到对Cortex Memory Map进行操作。

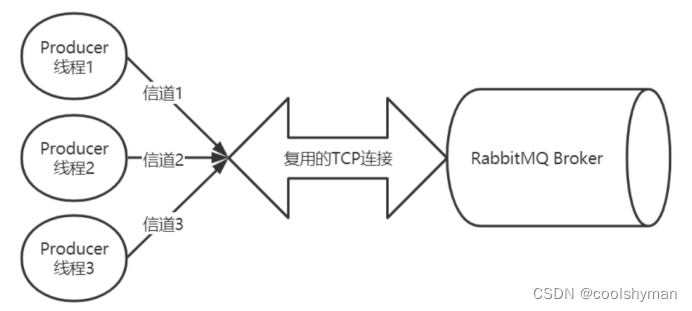

2、AHB-AP

SW-DP与AHB-AP之间通过DAP总线进行通信,DAP总线上的地址是32位的,其中高8位用于选择访问哪一个设备,由此可见,最多可以在DAP总线上面挂256个设备。在M3处理器的内部,只用掉了一个设备的地址,还剩下的255个都可以用于连接访问端口(AP)到DAP总线上。当数据传到DAP接口后,下一步就连接到了一个称为“AHB-AP”的AP设备上,它相当于一个总线桥,用于把DAP总线的命令转换为AHB总线上的数据传送,再插入到M3内部的总线网络中。这么一来,M3的整个寻址空间就都在覆盖范围之内了,连NVIC中的调试控制寄存器组也包括在内。在CoreSight系列产品中,AP设备可以有好几种类型,包括APB-AP和JTAG-AP。APB-AP顾名思义,是用于产生APB总线数据传送动作的,而JTAG-AP则用于控制传统的、基于JTAG的测试接口。

AHB-AP位于CM3的存储器系统和调试接口模块(SWJ-DP/SW_DP)之间,充当一个总线桥的角色。对于大多数基本的在调试主机和CM3系统之间的数据传输,只需要使用AHB-AP中的3个寄存器,它们是:控制及状态字(CSW)、传输地址寄存器(TAR)、数据读/写(DRW)。

CSW寄存器可以控制传送方向(读/写)、传送大小以及传送类型等。TAR寄存器则指令传送地址,而DRW寄存器则容纳了被传送的数据(在访问该寄存器时就启动了传送)。DRW中的数据与总线上实际显示的是一致的,所以对于半字和字节传送,必须由调试硬件把得到的数据适当移位,以对齐到LSB。例如,若欲在地址0x1002上执行一次半字传送,则需要把数据放到DRW的[31:16]上。AHB-AP可以产生非对齐传送,但是它不会根据地址偏移来自动对目标数据做圆圈移位,必须由调试软件堵上这个窟窿:要么手工圆圈移位,要么把未对齐访问分解为若干个对齐的访问。

在AHB-AP中还有其它的寄存器,它们提供附加的功能。例如,AHB-AP中提供了4个bannked寄存器和地址自动增量的功能,用于加快在小范围连续地址中数据访问的速度。在CSW寄存器中,还有一个名为MasterType的位。通常需要把它置1,以此告知参与AHB-AP数据传送的硬件:该数据传送是调试器发起的。但是,调试器也可以清零此位来伪装成处理器内核。这样,在AHB上接收数据的硬件就会以为是内核发起的数据传送,从而正常地动作。这个功能可以用于测试目的,尤其是对于带有FIFO的外设,用于获知当它被调试器访问时,行为有什么不同。

3、ROM表

说到这里,有一个问题还没有说明,JLink通过SW线连接SW-DP模块,那有如何得知AHB-AP在哪里呢?这里就引出了ROM表。

ROM表是M3内核包含的调试系统的一个部分,用于自动检测在某CM3芯片中包含了哪些调试组件。

CM3拥有一个预定义的存储器映射并且包含了标准的调试组件,但是新的Cortex-M器件可以包含不同的调试组件,并且芯片厂商在实现CM3时也可以对调试组件加以修改。为使调试工具能检测到调试系统中具体包含的组件,就提供了这张ROM表,它记录了NVIC和各个调试功能块的地址。

ROM表位于0xE00F_F000。通过分析ROM表中的内容,可以计算出系统和调试组件在存储器系统中的位置。在检测到了调试组件后,调试器可以接下来查看它们的ID寄存器,从而判定系统中哪些组件是可用的。

在CM3的ROM表中,第一条目的内容应当是:NVIC的入口地址相对于ROM表入口地址的偏移量。ROM表首条目的缺省值是0xFFF0F003,其中位段[1:0]的作用比较特殊:它指示本条目对应的设备是存在的,并且在本条目的后面还有后续的条目(也就是说本条目不是最后一个条目)。这样,通过第一个条目,我们就知道系统中有NVIC,并且还有第2个条目,而且还能计算出NVIC的地址为0xE00F_F000+0xFFF0_F000=0xE000_E000。

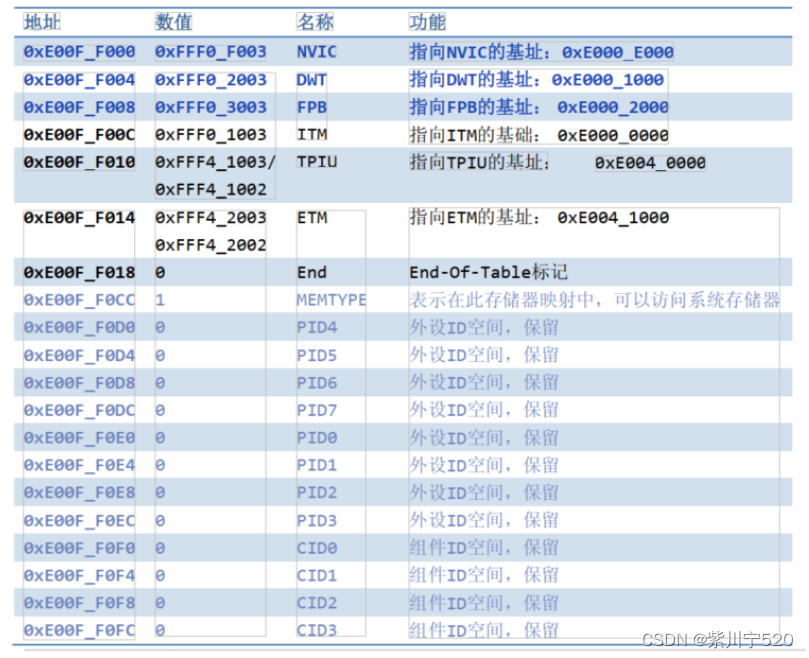

缺省的ROM表如图所示。但是因为芯片厂商可以添加、移除以及把某些可选的组件替换成其它的CoreSigth调试组件,这时该芯片的ROM表就会与缺省的有所不同,以反映出相应的变化。

Cortex-M3缺省的ROM表。

数值的最低两个位用于指示该设备是否存在(bit[1])以及后面还有没有其它的表项(bit[0])。在正常情况下,NVIC, DWT和FPB总是必须存在的,因此最后两位永远是1。然而,TPIU和ETM则可以被裁掉,并且可能被CoreSight家庭中其它的调试组件所取代。

数值的高位部分用给出对应组件的入口地址相对于ROM表入口地址的偏移量。例如,NVIC入口地址= 0xE00F_F000 + 0xFFF0_F000 = 0xE000_E000(进位位被忽略)

在开发调试工具时,有必要从ROM表中一一查兑各调试组件,因为难免会有些另类的CM3芯片会自定义调试组件,并且修改ROM表,而通过计算ROM表得到的地址是可以拿去拍板的。

到这里,可以知道,keil点击Download按钮之后,JLink会通过SW线连接芯片的SW-DP接口,和内部的AHB-AP接口进行通信,AHB-AP和总线进行通信,进而访问整个4G地址空间(芯片的所有地址都可以访问)。

三、flash

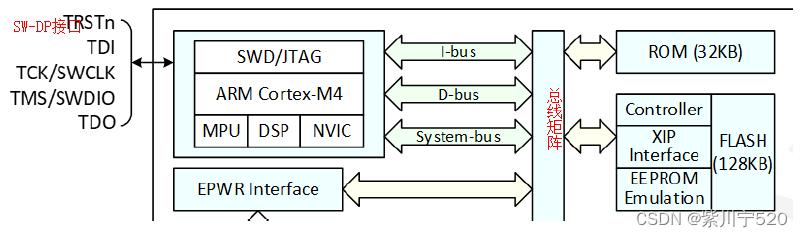

数据传输到AHB总线上之后(AHB总线、APB总线,二者通过总线桥连接),就可以传输到M3内核上整个4G地址空间了,可以访问M3内核上的所有资源,flash就是挂载到AHB总线上。一般储存程序的flash都是挂载到AHB总线上,因为AHB总线比APB总线快很多,低速外设如uart、timer等会挂载到APB上,但镜像文件(前面一直说的都是镜像文件,后面会对这个词进行说明)中包含程序的代码,自然访问速度越快越好,挂载到AHB总线上。flash连接总线以及与M4内核(M3、M4内核差距并不是很大,本文中也不牵扯二者差异的地方,读者可以在本系列文章中认为二者一样)连接图如图所示。

M3内核有3条总线:指令总线(I-BUS)、数据总线(D-BUS)、系统总线(System-BUS)。三条总线都有自己的地址总线、数据总线、控制总线。M3内核是哈弗结构,因此有指令总线和数据总线,二者并行取值。指令总线通过总线矩阵连接的XIP接口,从FLASH中取数据(指令)、数据总线通过XIP从flash取数据和从RAM中读写数据,系统总线访问其他的资源。这里请记者上图中的ROM,后面的文章会介绍它的作用。

到这里,我们用到的硬件以及其使用的协议都介绍了一下,博主本人为SWD、DAP等协议并没用进行深入的研究,其和本文主旨相关性并不是很强,更多的介绍的是数据的流通过程。