没有硬件,过几天上板测试。

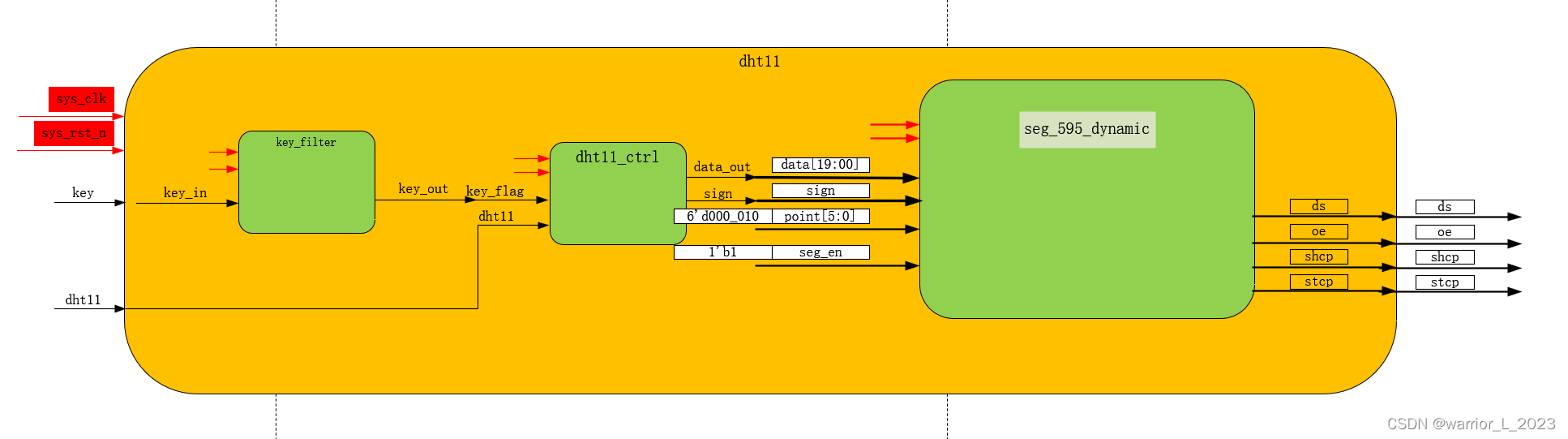

module dht11(input wire sys_clk ,input wire sys_rst_n ,input wire key ,inout wire dht11 ,output wire ds ,output wire oe ,output wire shcp ,output wire stcp

);// 例化连线wire key_out_w ;wire [19:00] data_w ;wire sign_w ;wire [ 5: 0] point_w ;wire en_w ;

key_filter key_filter_insert(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key ) ,.key_out ( key_out_w )

);dht11_ctrl dht11_ctrl_insert(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_flag ( key_out_w ) ,.dht11 ( dht11 ) ,.data_out ( data_w ) ,.sign ( sign_w )

);seg_595_dynamic seg_595_dynamic_insert(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.data ( data_w ) , .point ( point_w ) ,.sign ( sign_w ) , .seg_en ( en_w ) ,.ds ( ds ) ,.oe ( oe ) ,.shcp ( shcp ) ,.stcp ( stcp )

);endmodulemodule dht11_ctrl (input wire sys_clk ,input wire sys_rst_n ,input wire key_flag ,inout wire dht11 ,output reg [19:0] data_out ,output reg sign

);// reg signal define// 产生us时钟reg clk_us ;reg [4:0] cnt_clk_us ;// 内部信号(用于产生状态转移条件与输出信号)reg [19:0] cnt_us ;reg [ 6:0] cnt_low ;reg dht11_reg1 ;reg dht11_reg2 ;wire dht11_fall ;wire dht11_rise ;reg [ 5:0] bit_cnt ;reg [39:0] data_temp ;reg [31:0] data ;reg data_flag ;// 三态输出reg dht11_en ;wire dht11_out ;// [4:0] cnt_clk_us ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begincnt_clk_us <= 5'd0 ;end else beginif(cnt_clk_us == 5'd24) begincnt_clk_us <= 5'd0 ;end else begincnt_clk_us <= cnt_clk_us + 1'b1 ;endendend// clk_us ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginclk_us <= 1'b0 ;end else beginif(cnt_clk_us == 5'd24) beginclk_us <= ~clk_us ;end else beginclk_us <= clk_us ;endendend// reg signal define// 在clk_us时钟域下// 状态机 三段式写法(现态与次态描述)(状态转移条件描述)(输出信号描述)localparam WAIT_1S = 6'b000_001 ,START = 6'b000_010 ,DELAY_1 = 6'b000_100 ,REPLAY = 6'b001_000 ,DELAY_2 = 6'b010_000 ,RD_DATA = 6'b100_000 ;reg [5:0] state_c ;reg [5:0] state_n ;wire WAIT_1StoSTART ;wire STARTtoDELAY_1 ;wire DELAY_1toREPLAY ;wire REPLAYtoDELAY_2 ;wire REPLAYtoSTART ;wire DELAY_2toRD_DATA ;wire DELAY_2toSTART ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) beginstate_c <= 6'd0 ;end else beginstate_c <= state_n ;endendalways @(*) begincase (state_c)WAIT_1S:beginif(WAIT_1StoSTART) begin state_n <= START ;end else beginstate_n <= WAIT_1S ;endendSTART :beginif(STARTtoDELAY_1) beginstate_n <= DELAY_1 ;end else beginstate_n <= START ;endendDELAY_1:beginif(DELAY_1toREPLAY) beginstate_n <= REPLAY ;end else beginstate_n <= DELAY_1 ;endendREPLAY :beginif(REPLAYtoDELAY_2) begin state_n <= DELAY_2 ;end else beginif(REPLAYtoSTART) beginstate_n <= START ;end else beginstate_n <= REPLAY ;endendendDELAY_2:beginif(DELAY_2toRD_DATA) begin state_n <= RD_DATA ;end else beginstate_n <= DELAY_2 ;endendRD_DATA:beginif(DELAY_2toSTART) beginstate_n <= START ;end else beginstate_n <= RD_DATA ;endenddefault: state_n <= START ;endcaseend// 状态机第二段描述assign WAIT_1StoSTART = (state_c == WAIT_1S && cnt_us == 20'd999_999) ? 1'b1 : 1'b0 ;assign STARTtoDELAY_1 = (state_c == START && cnt_us == 20'd17_999) ? 1'b1 : 1'b0 ;assign DELAY_1toREPLAY = (state_c == DELAY_1 && cnt_us == 20'd10) ? 1'b1 : 1'b0 ;assign REPLAYtoDELAY_2 = (state_c == REPLAY && dht11_rise == 1'b1 && cnt_low <= 7'd85 && cnt_low >= 7'd81) ? 1'b1 : 1'b0;assign REPLAYtoSTART = (state_c == REPLAY && dht11_rise == 1'b1 && (cnt_us >= 20'd100 || cnt_us <= 20'd70)) ? 1'b1 : 1'b0 ;assign DELAY_2toRD_DATA= (state_c == DELAY_2 && dht11_fall == 1'b1 && cnt_us >= 20'd85 && cnt_us <= 20'd88) ? 1'b1 : 1'b0 ;assign DELAY_2toSTART = (state_c == RD_DATA && bit_cnt == 6'd40 && dht11_rise == 1'b1) ? 1'b1 : 1'b0 ;// // 内部信号(用于产生状态转移条件与输出信号)// reg [19:0] cnt_us ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begincnt_us <= 20'd0 ;end else beginif((state_c == WAIT_1S && cnt_us == 20'd999_999) || (state_c == START && cnt_us == 20'd17_999) || (state_c == DELAY_1 && cnt_us == 20'd10) || (state_c == REPLAY && dht11_rise == 1'b1)|| (state_c == DELAY_2 && dht11_fall == 1'b1)|| (state_c == RD_DATA && (dht11_fall || dht11_rise)))begin // 记得最后加大括号cnt_us <= 20'd0 ;end else begincnt_us <= cnt_us + 1'b1 ;endendend// reg [ 6:0] cnt_low ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begincnt_low <= 7'd0 ;end else beginif(state_c == REPLAY && dht11_reg1 == 1'b0) begincnt_low <= cnt_low + 1'b1 ;end else begincnt_low <= 7'd0 ;endendend// reg dht11_reg1 ;// reg dht11_reg2 ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begindht11_reg1 <= 1'b1 ;dht11_reg2 <= 1'b1 ;end else begindht11_reg1 <= dht11 ;dht11_reg2 <= dht11_reg1 ;endend// wire dht11_fall ;// wire dht11_rise ;assign dht11_fall = ~dht11_reg1 && dht11_reg2 ;assign dht11_rise = dht11_reg1 && ~dht11_reg2 ;// reg [ 5:0] bit_cnt ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) beginbit_cnt <= 6'd0 ;end else beginif(dht11_rise && bit_cnt == 6'd40 ) beginbit_cnt <= 6'd0 ;end else beginif(state_c == RD_DATA && dht11_fall) beginbit_cnt <= bit_cnt + 1'b1 ;end else beginbit_cnt <= bit_cnt ;endendendend// reg [39:0] data_temp ;always @(posedge clk_us or negedge sys_rst_n) begin if(~sys_rst_n) begindata_temp <= 40'd0 ;end else beginif(state_c == RD_DATA && dht11_fall && bit_cnt <= 39) beginif(cnt_us >= 20'd50) begin // 也可以是68data_temp[39 - bit_cnt] <= 1'b1 ;end else begindata_temp[39 - bit_cnt] <= 1'b0 ;endend else begindata_temp <= data_temp ;endendend// reg [31:0] data ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begindata <= 32'd0 ;end else beginif(data_temp[7:0] == (data_temp[15:8] + data_temp[23:16] + data_temp[31:24] + data_temp[39:32])) begindata <= data_temp[39:8] ;end else begindata <= data ;endendend// reg data_flag ; sys_clk时钟域下always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begindata_flag <= 1'b0 ;end else beginif(key_flag) begindata_flag <= ~data_flag ;end else begindata_flag <= data_flag ;endendend// // 三态输出// wire dht11_out ;assign dht11 = (dht11_en == 1'b1) ? dht11_out : 1'bz ;assign dht11_out = 1'b0 ;// reg dht11_en ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begindht11_en <= 1'd0 ;end else beginif(state_c == START) begindht11_en <= 1'b1 ;end else begindht11_en <= 1'b0 ;endendend// output signal// reg [19:0] data_out ,always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begindata_out <= 20'd0 ;end else beginif(data_flag == 1'b0) begin // 显示湿度data_out <= data[31:24] * 16'd10 ;end else begindata_out <= data[15:8] * 16'd10 + data[3:0] ;endendend // reg sign always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginsign <= 1'b0 ;end else beginif(key_flag == 1'b1 && data[7] == 1'b1) beginsign <= 1'b1 ;end else beginsign <= 1'b0 ;endendend

endmodule其他模块都是之前的,就不发了。