目录

一、分类方法汇总

二、指令流和数据流的关系分类

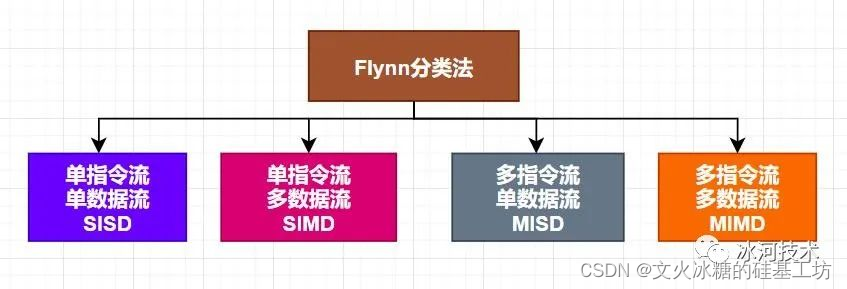

三、Flynn 分类:指令并行处理

四、根据指令集架构(ISA)分类

4.1 分类

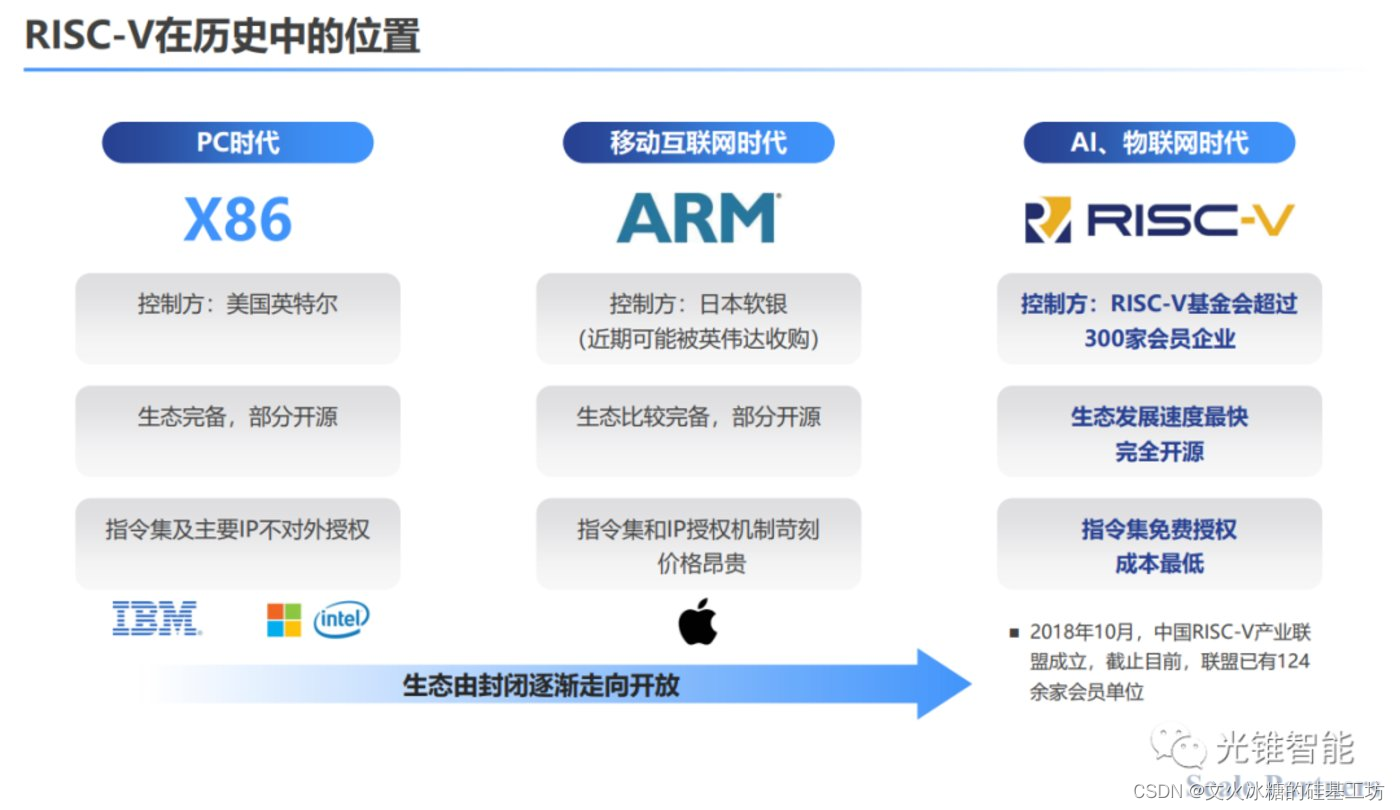

4.2 开源的RISC-V与封闭的RISC指令集架构比较

4.3 RISC-V的演进路径

4.4 RISC-V与中国芯片自研

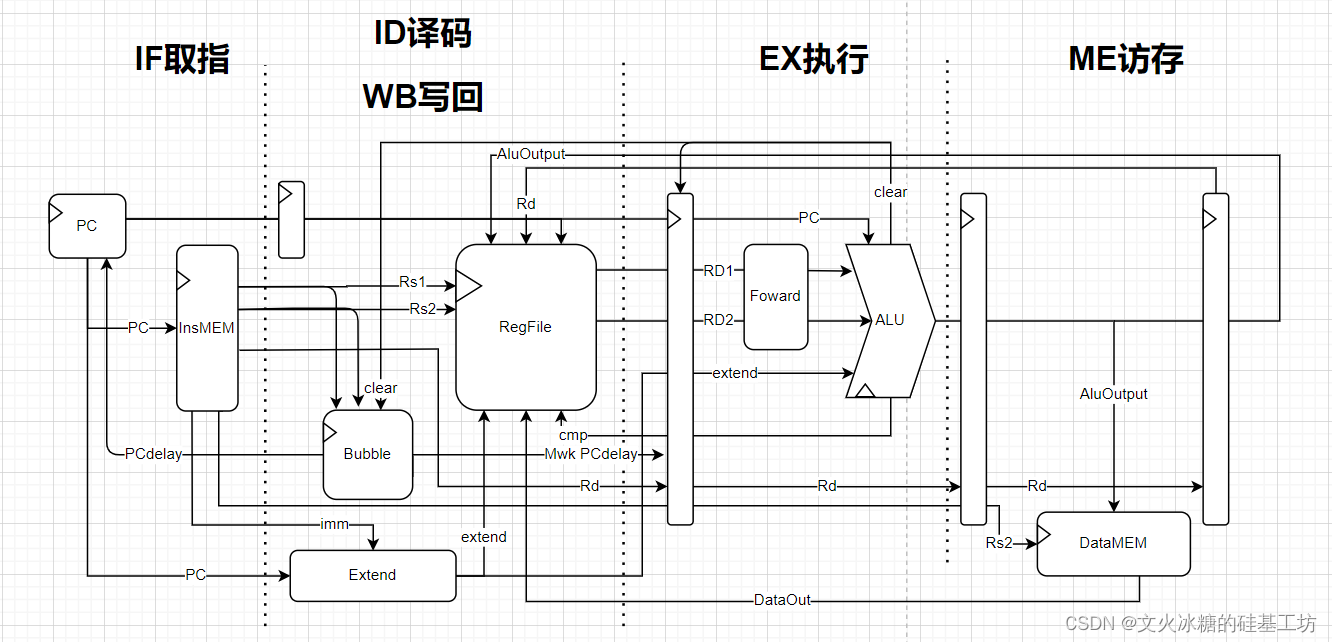

4.4 五阶流水线设计

五、RISC和CISC内部实现

5.1 RISC

5.2 CISC与微指令

一、分类方法汇总

计算机体系结构可以根据不同的分类方法进行分类。

以下是几种常见的分类方法:

-

根据指令流和数据流的关系:

- 冯·诺依曼体系结构:程序和数据存储在同一个存储器中,指令按照顺序执行。

- 哈佛体系结构:程序存储在一个存储器中,数据存储在另一个存储器中,指令和数据并行处理。

-

根据指令集架构(ISA):

- RISC(精简指令集计算机)体系结构:使用较为简单的指令集,执行速度较快,例如ARM和MIPS。

- CISC(复杂指令集计算机)体系结构:使用较为复杂的指令集,可以执行复杂的操作,例如x86。

-

根据并行性:

- SIMD(单指令流多数据流)体系结构:通过单条指令同时处理多个数据元素,例如GPU。

- 、单指令流多数据流 (SIMD):这种架构下,多个处理器同时执行相同的指令,但是每个处理器操作不同的数据流。常见的示例包括图形处理器 (GPU),GPU 可以同时对大量数据进行相同的操作,用于图形渲染、数字信号处理等领域。

- MIMD(多指令流多数据流)体系结构:有多个处理单元,每个处理单元可以执行不同的指令和数据,例如多核处理器和计算机集群。

-

根据处理器的数量:

- 单核处理器体系结构:只有一个处理核心,一次只能执行一个线程。

- 多核处理器体系结构:有多个处理核心,可以同时执行多个线程。

-

根据功能和应用场景:

- 通用计算机体系结构:面向通用计算任务,适用于日常办公、互联网浏览等应用。

- 嵌入式计算机体系结构:用于嵌入式系统,具有较低的功耗和小型化特点。

- 高性能计算机体系结构:用于科学计算、大规模数据处理等高性能应用。

这些是常见的计算机体系结构分类方法,每种分类方法都可以帮助我们理解不同类型的计算机架构及其特点。

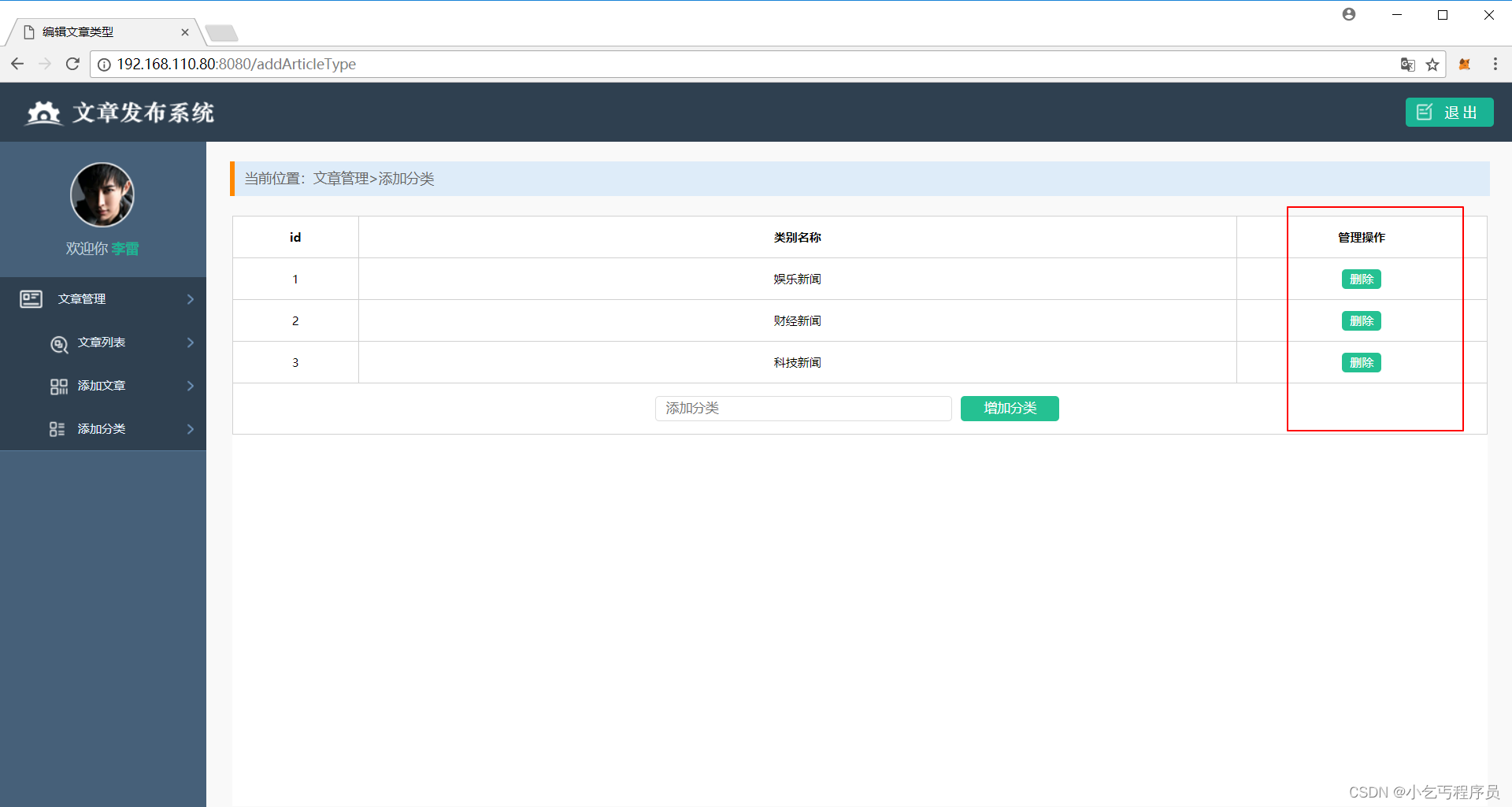

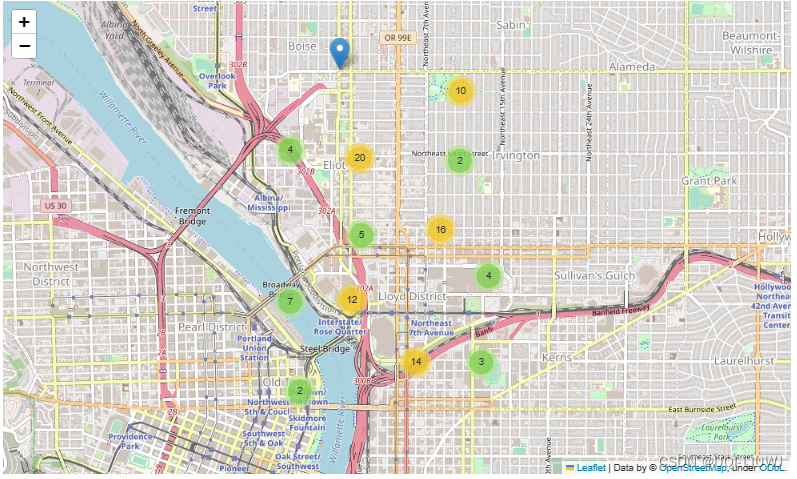

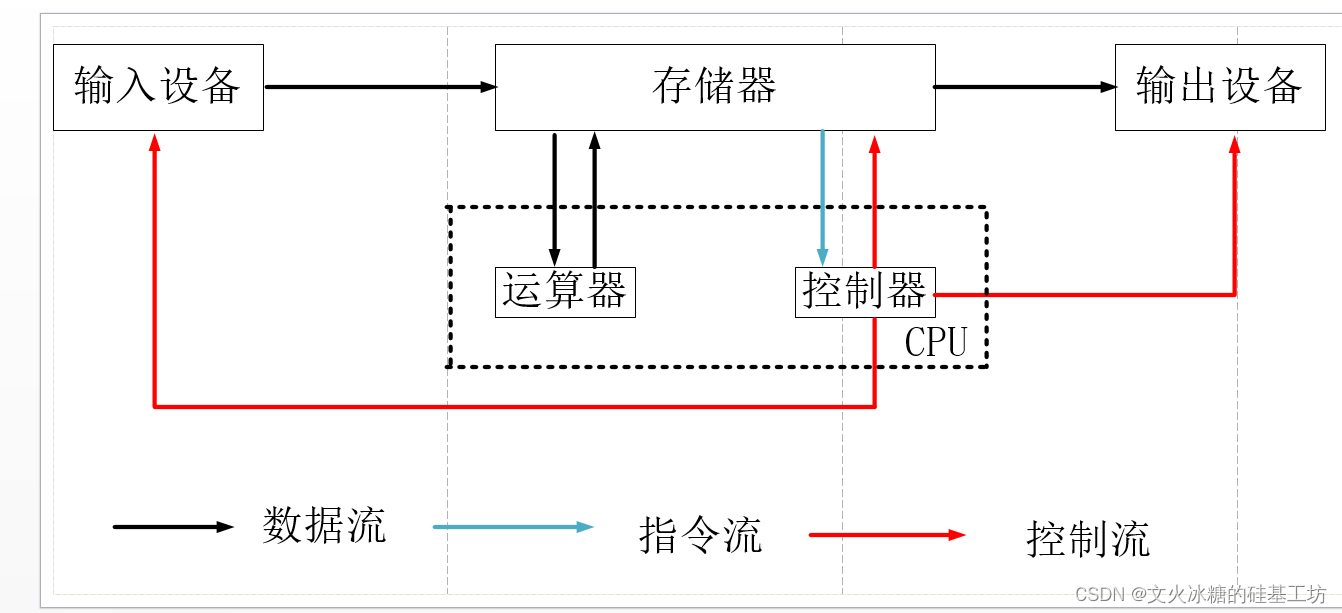

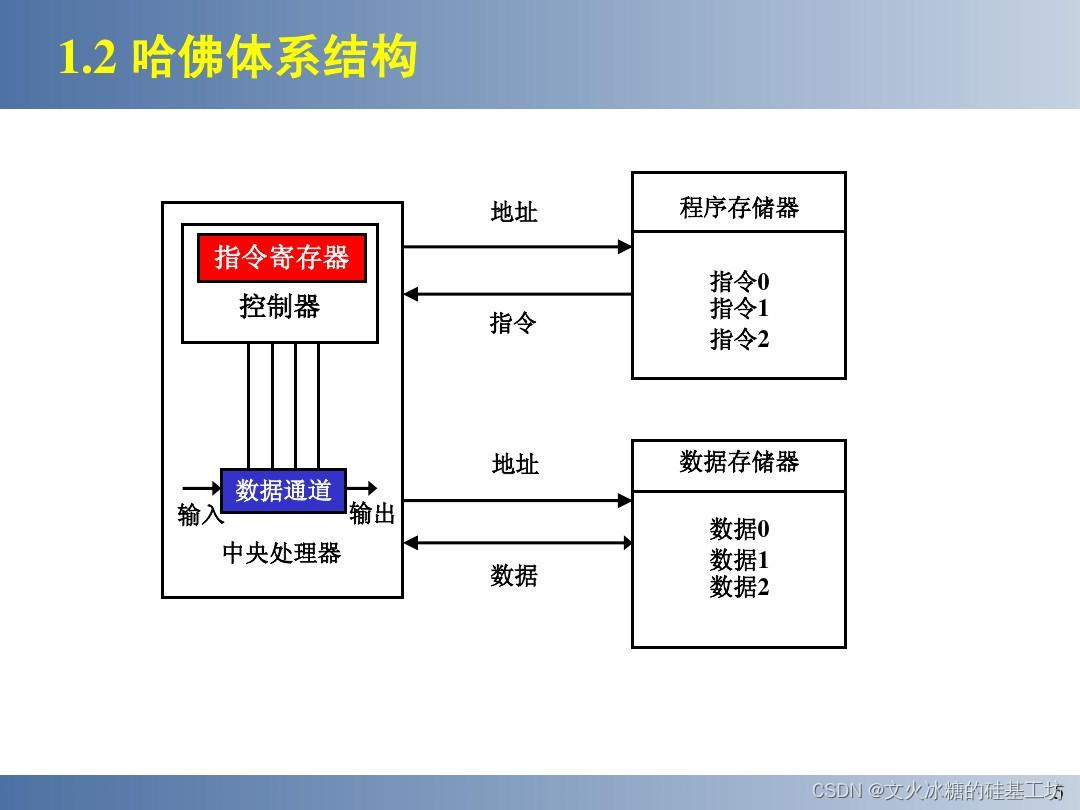

二、指令流和数据流的关系分类

冯·诺依曼体系结构和哈佛体系结构是两种常见的计算机体系结构,它们在存储器组织方式和指令处理上有一些不同之处。

下面是它们的比较:

-

存储器组织:

- 冯·诺依曼体系结构:程序和数据共享同一个存储器,被称为存储器统一。即指令和数据都存储在同一块内存中,通过地址来区分。

- 哈佛体系结构:程序和数据分别存储在两个独立的存储器中,被称为存储器分离。分开存储指令和数据可以同步读取,提高了并行性。

-

指令执行方式:

- 冯·诺依曼体系结构:指令按顺序执行,逐条从存储器中取出执行。

- 哈佛体系结构:指令和数据可以同时获取和执行,提高了指令的并行性和效率。

-

程序和数据的处理:

- 冯·诺依曼体系结构:程序和数据都存储在存储器中,通过指令和数据的地址进行访问。因此,指令和数据在存储器中的位置是相对固定的。

- 哈佛体系结构:程序和数据分别存储在独立的存储器中,它们之间的访问和处理方式有所不同。这使得哈佛体系结构可以实现更高效的并行处理和指令流。

-

应用领域:

- 冯·诺依曼体系结构:广泛应用于通用计算机、服务器、个人电脑等多种计算设备。它简单、灵活且易于实现。

- 哈佛体系结构:主要应用于嵌入式系统、DSP(数字信号处理器)、图形处理器(GPU)等需要高效并行处理的领域。

总体而言,冯·诺依曼体系结构和哈佛体系结构都是计算机体系结构中的经典代表。冯·诺依曼体系结构适用于大多数通用计算任务,而哈佛体系结构则更适合于需要高效的并行处理和实时应用的领域。选择哪种体系结构要根据实际应用需求和性能要求来决定。

三、Flynn 分类:指令并行处理

Flynn 分类是一种指令并行处理的分类方法,它将计算机处理器的设计按照指令流和数据流的并行性进行划分。

事先说明:

以下是 Flynn 分类的四种类型及其可能的示例:

-

单指令流单数据流 (SISD):

这是传统的顺序处理架构,其中一条指令流按顺序操作一个数据流。常见的示例包括传统的个人电脑 CPU,比如 Intel 的 x86 架构或 AMD 的 Ryzen 架构,包括现在主流的单核的单片机。 -

单指令流多数据流 (SIMD):

这种架构下,多个处理器同时执行相同的指令,但是每个处理器操作不同的数据流。常见的示例包括图形处理器 (GPU),GPU 可以同时对大量数据进行相同的操作,用于图形渲染、数字信号处理等领域。 -

多指令流单数据流 (MISD):

这类架构中,多个处理器同时执行不同的指令流,但是操作相同的数据流。实际上,MISD 在实践中很少使用,因为大多数应用场景不需要这种处理方式。 -

多指令流多数据流 (MIMD):

这是一种最常见的多核并行处理架构,其中多个处理器独立执行不同的指令流和数据流。常见的示例包括分布式计算系统,如超级计算机集群或云计算架构,每个处理器可以独立地执行任务并处理不同的数据。

需要说明的是,具体的处理器设计可能会结合多种 Flynn 分类的特性,以满足不同的应用需求。

四、根据指令集架构(ISA)分类

4.1 分类

根据指令集架构(ISA)的不同,计算机体系结构可以分为以下几类:

-

CISC(复杂指令集计算机)体系结构:

- CISC体系结构使用较复杂的指令集,指令可以执行较为复杂的操作。

- 它具有丰富的指令集和灵活的地址模式,可以处理复杂的任务。

- 常见的CISC体系结构包括x86架构(如Intel的x86和AMD的x86-64)。

-

RISC(精简指令集计算机)体系结构:

- RISC体系结构使用较简单的指令集,指令执行速度快。

- 它的指令集非常精简,每条指令执行的操作非常简单。

- RISC体系结构更加注重指令和数据处理的效率,提供更高的性能。

- 常见的RISC体系结构包括ARM、MIPS、PowerPC等。

-

VLIW(超长指令字)体系结构:

- VLIW体系结构通过在一个指令中打包多个操作,实现指令级并行。

- 它需要由编译器对指令进行静态调度,利用硬件实现并行执行。

- VLIW处理器的性能高度依赖于编译器的优化能力。

- 常见的VLIW体系结构包括IA-64(如Intel的Itanium)。

-

EPIC(显式并行指令计算机)体系结构:

- EPIC体系结构引入了更多的硬件资源来支持指令级并行。

- 它通过利用编译器静态分析和硬件支持,实现指令级并行性和动态调度。

- EPIC体系结构可以在运行时并行执行多条指令流,提高性能。

- 常见的EPIC体系结构包括IA-64(如Intel的Itanium)。

这些是常见的根据指令集架构分类的计算机体系结构。每种体系结构都有其优点和适用场景,选择适合的体系结构需要考虑到应用需求、性能要求和开发成本等因素。

4.2 开源的RISC-V与封闭的RISC指令集架构比较

开源的RISC-V指令集架构与封闭的RISC指令集架构(如ARM)相比,有以下一些实例比较:

-

可定制性:开源的RISC-V架构使开发者能够根据自己的需求进行定制和优化。他们可以添加自己的指令集扩展,优化特定应用程序的性能,根据目标市场需求进行定制。而封闭的RISC架构则限制了开发者对指令集的定制能力。

-

透明度和可审查性:开源的RISC-V架构使开发者能够查看和分析架构的设计、实现和优化方法。这种透明度可以提高架构的可审查性,帮助开发者更好地理解和调试处理器设计。而封闭的RISC架构不允许开发者查看其内部设计和实现细节。

-

社区和生态系统支持:RISC-V拥有庞大的开源社区,其中有许多贡献者和开发者为其提供支持和扩展。开发者可以利用社区基础设施,如工具链、仿真器和开发板等,从而更容易地开发和测试基于RISC-V的系统。而封闭的RISC架构可能依赖于特定的供应商和他们的开发工具。

-

价格和许可:作为开源项目,RISC-V可以免费使用,不需要支付版权费用。这使得RISC-V在一些应用场景中更具有成本竞争力,尤其是对于初创公司和项目来说。而封闭的RISC架构则需要支付相关的许可费用,这可能增加了初始投资和开发成本。

需要注意的是,封闭的RISC架构通常具有更成熟和广泛的生态系统支持,以及更多的商业支持和投资。一些特定的行业或领域,如高性能计算、移动设备等,可能更倾向于使用封闭的RISC架构。开发者在选择架构时需要综合考虑项目需求、成本、生态系统支持和技术能力等因素。

4.3 RISC-V的演进路径

RISC-V是一种开源指令集架构(Instruction Set Architecture,ISA),它是基于精简指令集计算机(RISC)原则设计的。与传统的商业指令集架构不同,RISC-V采用了开放的设计哲学,提供了一个公开的标准,任何人都可以免费使用、定制和实现该架构。

RISC-V的设计目标是简洁、灵活和可扩展,旨在满足各种应用领域的需求,从嵌入式系统到高性能计算。它的指令集设计简单,但覆盖了大多数常见的计算操作,并支持各种扩展,如浮点计算、向量计算等。这使得RISC-V在不同领域的应用具有广泛的适用性。

由于RISC-V是开源的,它具有许多优势,例如透明度高、可定制性强、节约成本等。这使得RISC-V在学术界、工业界和社区中受到了广泛的关注和采用。许多公司和组织都开始使用RISC-V作为他们的处理器平台,开发出自己的产品和解决方案。

总而言之,RISC-V是一个开源的指令集架构,具有简洁、灵活和可扩展的设计原则,适用于各种应用领域,受到了广泛的关注和采用。

在RISC-V中,V代表"五"(Five),因为RISC-V是基于五阶流水线的设计。这个名称突出了RISC-V的关键设计原则之一:简洁性。RISC-V的指令集设计非常简单,只有少数几类基本指令,这使得它易于理解和实现。通过保持指令集的精简性,RISC-V旨在提供一个通用的、可扩展的指令集架构,适用于广泛的应用领域。所以,RISC-V中的V代表着使用五阶流水线设计的简洁指令集架构。

RISC-V拥有一个从基础指令集到扩展指令集的演进路径,以下是RISC-V演进路径的一些关键方面:

-

基础指令集(Base ISA):RISC-V定义了几个标准的基础指令集,如RV32I和RV64I,它们包含了基本的整数操作指令。这些基础指令集构成了RISC-V的核心,并为其他扩展和变体提供了基础。

-

扩展指令集(Extension ISA):RISC-V通过扩展指令集来增加特定功能和应用的支持。例如,乘法扩展(M)提供了整数乘法和除法指令,浮点扩展(F)支持浮点数操作,向量扩展(V)提供了向量数据处理指令等。这些扩展可以根据应用需求选择和组合。

-

标准扩展(Standard Extensions):除了基础指令集和扩展指令集外,RISC-V还定义了一些标准扩展,如乘法扩展(M)、原子扩展(A)、压缩扩展(C)等。这些标准扩展提供了一组常用的功能和功能组合,使开发者能够更方便地选择和使用。

-

可选扩展(Optional Extensions):RISC-V允许开发者根据应用需求添加自定义的可选扩展。这些可选扩展包括向量扩展(V)、加密扩展(E)、多媒体扩展(N)等,开发者可以根据特定应用的需求选择和设计自己的扩展。

-

移动端扩展(Mobile Extensions):RISC-V正在开发移动端扩展,以满足移动设备领域的需求。这些扩展包括指令和功能,以支持高效能、低功耗和实时响应等移动应用场景。

总体而言,RISC-V提供了一个模块化的演进路径,允许开发者根据具体的应用需求选择和设计适合的指令集和扩展。这种灵活性和可定制性使得RISC-V能够广泛应用于各种领域和应用场景。同时,RISC-V社区还在不断演进和开发新的扩展,以满足不断变化的市场需求。

RISC-V是一种基于RISC(Reduced Instruction Set Computer)架构的开源指令集,它具有可定制性、灵活性和可扩展性,广泛应用于各种领域。

以下是RISC-V的一些常见系列和变体:

-

RV32:这是RISC-V的32位变体,其中RV表示"RISC-V",32表示数据寄存器和地址寄存器的位数。RV32系列常用于嵌入式设备和低功耗应用。

-

RV64:这是RISC-V的64位变体,与RV32相比,提供更大的地址空间和寄存器容量,适用于高性能计算、服务器和操作系统等应用。

-

RV32I:这是RV32系列中的一个标准基础指令集,包含整数操作的基本指令。

-

RV64I:这是RV64系列的标准基础指令集,与RV32I相比,支持更大的寄存器和数据宽度。

-

RV32E:这是RV32系列的嵌入式变体,以更小的指令集和寄存器集合为特点,适用于资源受限的设备和嵌入式系统。

-

RV32IM:这是RV32系列的标准指令集,包含整数操作(I),乘法扩展(M),以及某些乘法和除法指令。

-

RV32F/RV64F:这是RISC-V的浮点指令集,支持单精度浮点数操作,RV32F适用于32位系统,RV64F适用于64位系统。

-

RV32G/RV64G:这是RISC-V的通用指令集,包含整数操作(I),乘法扩展(M),以及分支扩展(B),适用于通用计算和嵌入式系统。

除以上常用的RISC-V系列之外,还有各种扩展和定制变体,如向量扩展(V),加密扩展(E),多媒体扩展(N),以及各种自定义指令集等,这些扩展和变体可以根据特定的应用需求选择和设计。

需要注意的是,RISC-V是一个模块化的指令集架构,通过选择不同的扩展和变体,可以根据应用的需求进行配置,灵活适应各种场景。

4.4 RISC-V与中国芯片自研

RISC-V是一个开源的指令集架构,与中国芯片自研有一定的联系。中国在近年来加大了芯片自研的力度,而RISC-V作为一个开放的指令集架构,提供了一个自主研发芯片的选择。

中国可以基于RISC-V的开源架构进行自主研发,而不必受限于闭源的商业指令集架构,如x86和ARM。这使得中国能够进一步加强对自主芯片设计的控制,降低对国外技术的依赖,并促进本土芯片产业的发展。

在中国,一些政府机构、高校和企业已经开始采用RISC-V架构进行芯片设计和开发。中国的一些芯片厂商也开始推出采用RISC-V架构的处理器和芯片产品。

然而,需要注意的是,RISC-V与中国芯片自研并非完全等同。芯片自研包括了整个芯片设计的过程,包括处理器架构的选择、电路设计、芯片制造等。RISC-V仅提供了一个开源的指令集架构,在芯片设计过程中,可以选择RISC-V作为处理器核心的架构。

总体而言,RISC-V为中国芯片自研提供了一个开放、灵活的选择,能够促进中国芯片产业自主创新和发展。但芯片自研的成功还需要综合考虑技术研发、制造能力、市场需求和产业生态等多个方面因素。

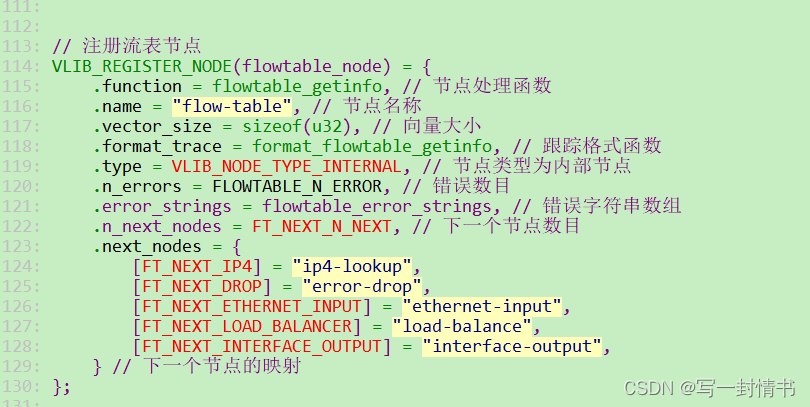

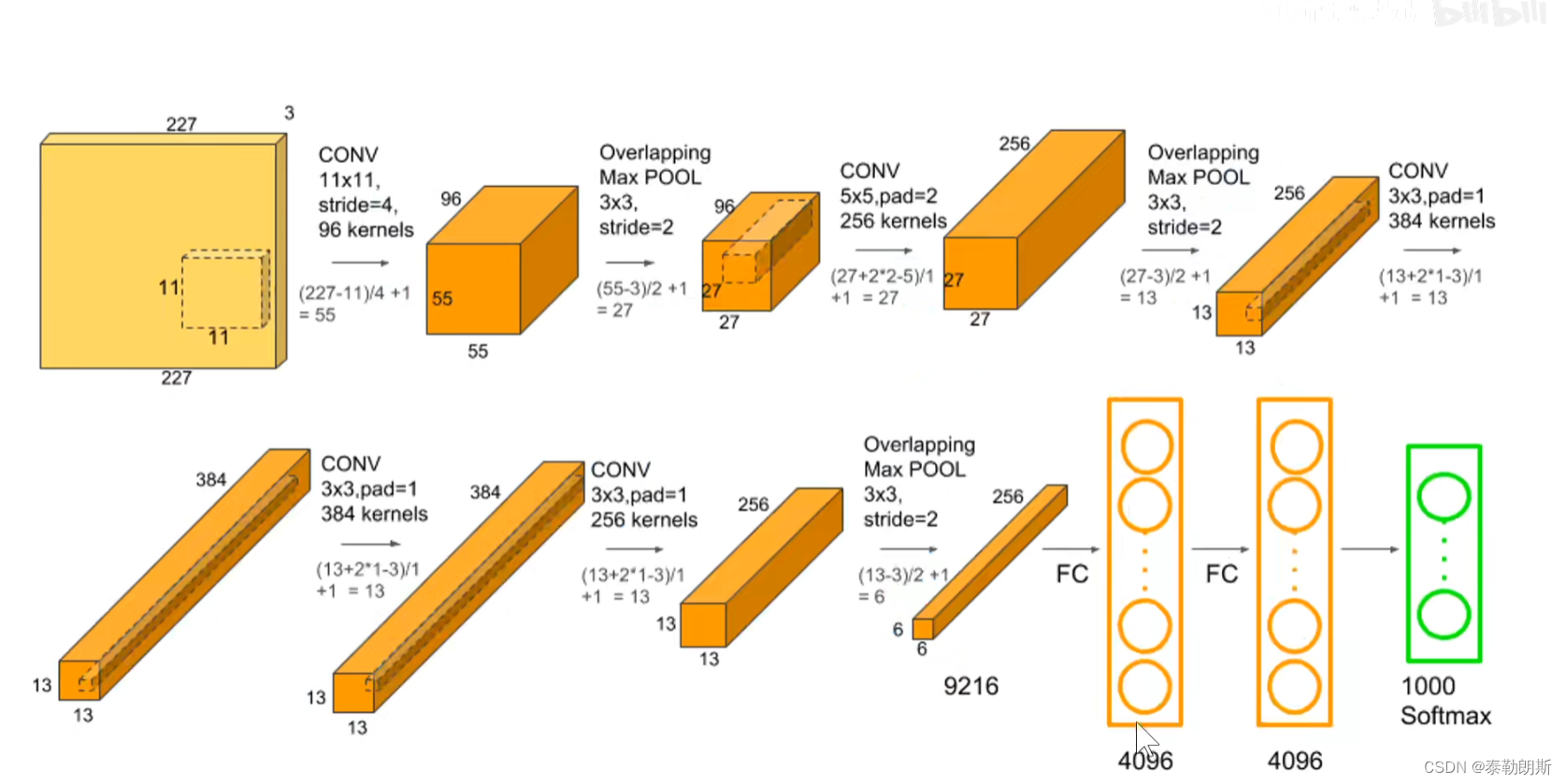

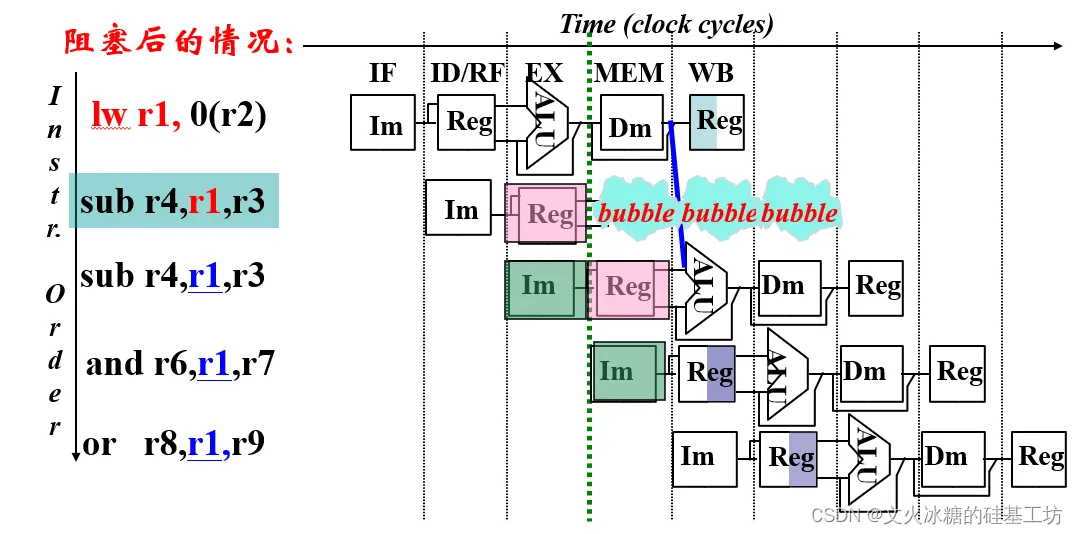

4.4 五阶流水线设计

五阶流水线设计是一种常见的计算机处理器设计方法。它将处理器的指令执行过程分为五个连续的阶段,以提高处理器的执行效率和吞吐量。

这五个阶段分别是取指令(Instruction Fetch)、指令译码(Instruction Decode)、执行(Execute)、访存(Memory Access)和写回(Write Back)。

在取指令阶段,处理器从内存中获取下一条指令。

然后,在指令译码阶段,处理器识别并解码指令,确定它要执行的操作。

在执行阶段,处理器根据指令执行相应的操作,如算术逻辑运算、跳转或加载/存储操作等。

接下来,在访存阶段,处理器根据需要访问内存,读取或写入数据。

最后,在写回阶段,处理器将执行的结果写回寄存器文件或内存中。

通过将处理器的指令执行过程分为这些独立的阶段,并使用流水线技术,处理器可以同时执行多条指令的不同阶段,从而提高整体的处理速度。这种设计方法能够充分利用处理器的硬件资源,并使指令在处理器中流经的时间减少,提高了指令的吞吐量。

需要注意的是,五阶流水线设计是一种简化的描述,实际的处理器设计可能会使用更多的流水段或有一些变化,以应对不同的设计需求和性能优化。

五、RISC和CISC内部实现

RISC(Reduced Instruction Set Computing)和CISC(Complex Instruction Set Computing)是两种不同的指令集架构。

5.1 RISC

RISC指令集架构致力于简化指令集,使指令集的数量和复杂度较少。RISC处理器采用固定长度的指令格式,指令的操作码和操作数的位置固定,执行速度相对较快。

其内部实现通常采用流水线技术,即将指令的执行划分为多个阶段,各阶段并行执行以提高效率。RISC处理器的设计追求简单和高效,注重快速执行简单指令的能力。

在RISC处理器的内部实现中,指令执行往往采用流水线技术,其中包括取指令、译码、执行、取数据和写回数据等阶段。流水线的优势在于可以并行地执行多条指令,提高整体执行效率。此外,RISC处理器通常采用基于寄存器的数据传输方式,将数据存储在寄存器文件中,并使用寄存器之间的数据传输来完成计算操作。

在RISC处理器的硬件布线逻辑中,由于其指令集相对简单,通常采用流水线技术来提高指令的执行效率。流水线将指令执行划分为多个阶段,每个阶段专注于特定的指令执行任务,以并行方式处理多条指令。硬件布线逻辑需要确保每个阶段的数据传输和控制信号的正确传递,并保持流水线的进度不被阻塞。

5.2 CISC与微指令

相反,CISC指令集架构具有丰富的指令集和复杂的指令格式,每个指令包含多个操作数和复杂的操作。

CISC处理器的内部实现通常包含了多个微指令,这些微指令被组合成一条高级指令来执行。CISC处理器的设计旨在提供更高层次的抽象和功能,以方便程序员编写复杂的指令序列。

在CISC处理器的内部实现中,通常包含了一系列的微指令,这些微指令由控制单元根据高级指令解析生成。这些微指令被执行单元逐条执行,完成复杂的操作。CISC处理器的内部实现一般较为复杂,包含了更多的电路和逻辑单元。

需要注意的是,RISC和CISC的内部实现方式可能因不同的处理器架构、厂商和设计目标而有所不同。此外,近年来,由于技术进步和设计思想的交融,RISC和CISC的差异逐渐模糊,许多处理器结合了两者的特点,采用了混合的指令集架构。

RISC处理器的硬件布线逻辑还包括寄存器文件的设计。RISC处理器倾向于使用寄存器来存储和处理数据,因此需要设计适当的寄存器文件来存储和访问寄存器中的数据。

在CISC处理器的硬件布线逻辑中,由于其指令集较为复杂,通常需要更复杂的控制逻辑和微指令的执行单元。硬件布线逻辑需要处理复杂指令的解码和执行,包括多个操作数的选择和操作的执行步骤。此外,CISC处理器通常还会包括一些特殊的硬件模块,如浮点运算单元(FPU)等,以支持复杂的运算操作。

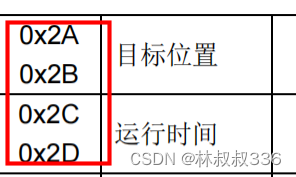

在CISC(Complex Instruction Set Computing)处理器中,微指令是实现高级指令的基本操作单元。微指令是一种较低级别的指令,由控制单元生成并用于操作处理器的内部组件执行复杂的操作。

CISC处理器的高级指令(汇编程序员使用的指令)由多个微指令(芯片设计人员使用的指令)组成,这些微指令执行处理器内部的具体操作,例如数据传输、算术逻辑操作、存储器访问和控制转移等。这些操作都被分解为一系列微指令,每个微指令执行处理器内部的具体动作。

微指令包含了微操作字段,用于控制和配置处理器内部的电路和寄存器。微指令字段通常包括操作码、操作数、寄存器选择、数据传输、开关控制等。这些字段会根据高级指令的要求配置,并由控制单元生成相应的微指令序列。

控制单元根据高级指令解析生成微指令的过程称为微指令控制。微指令控制的主要任务是解析高级指令,并将其转化为一系列的微操作和微指令,以便处理器能够按照预定的步骤执行相应的操作。

在CISC处理器的内部,微指令通过控制总线或指令总线传输到执行单元,执行相应的操作。执行单元根据微指令的指示执行相应的微操作。

需要注意的是,CISC处理器的微指令实现是处理器设计的一部分,不同的CISC处理器可能采用不同的微指令格式和控制方式,以适应不同的设计要求和性能需求。因此,具体的微指令设计和实现因处理器而异。