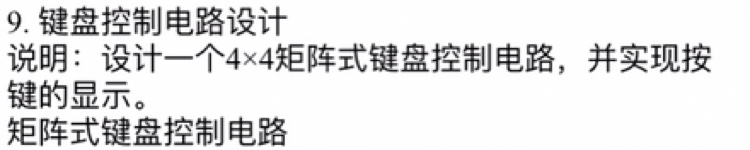

名称:4x4矩阵键盘设计Verilog矩阵式键盘控制

软件:Quartus

语言:Verilog

代码功能:

键盘控制电路设计,设计一个4x4矩阵式键盘控制电路,并实现按键的显示。

演示视频:4x4矩阵键盘设计Verilog矩阵式键盘控制_Verilog/VHDL资源下载

代码下载:

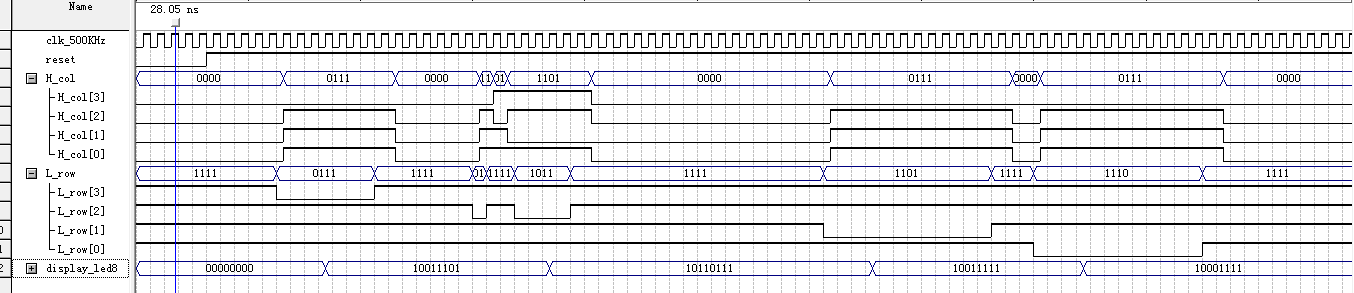

4x4矩阵键盘设计Verilog矩阵式键盘控制_Verilog/VHDL资源下载名称:4x4矩阵键盘设计Verilog矩阵式键盘控制(代码在文末付费下载)软件:Quartus语言:Verilog代码功能:键盘控制电路设计,设计一个4x4矩阵式键盘控制电路,并实现按键的显示。演示视频:部分代码展示module key_4x4 ( clk_500KHz,//500KHZ reset, //低电平复位L_row, //行 H_col, //列 display_l![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=192

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=192

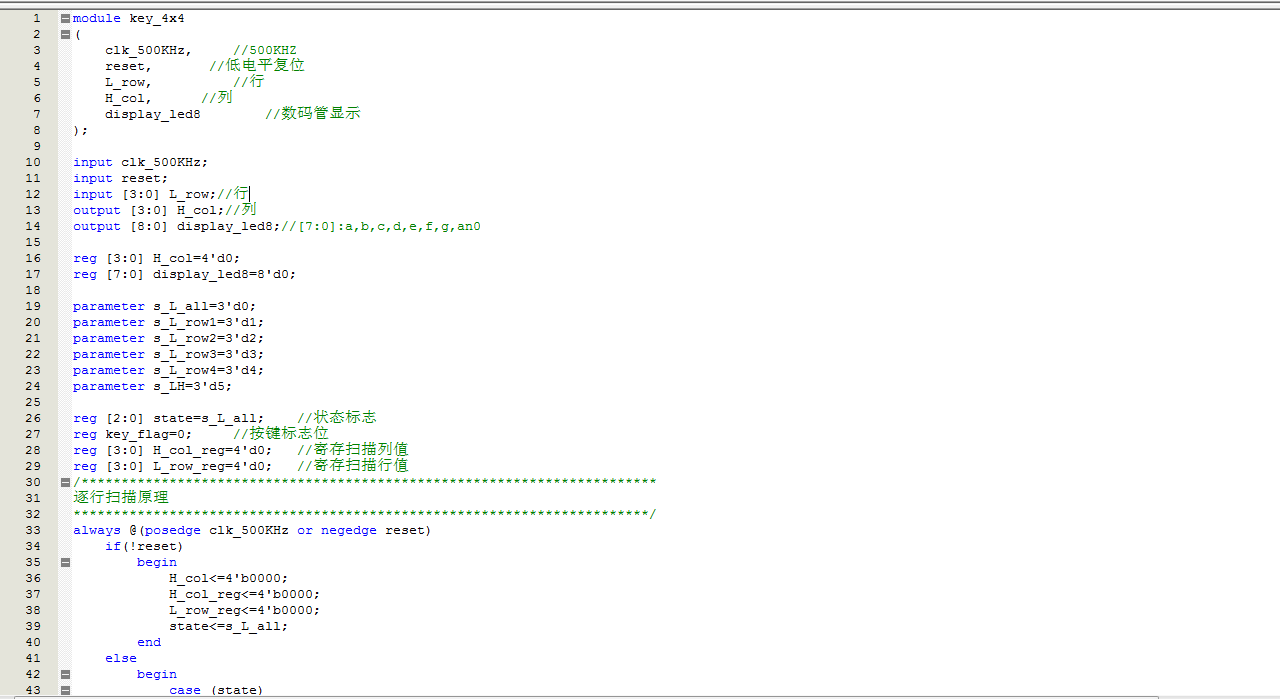

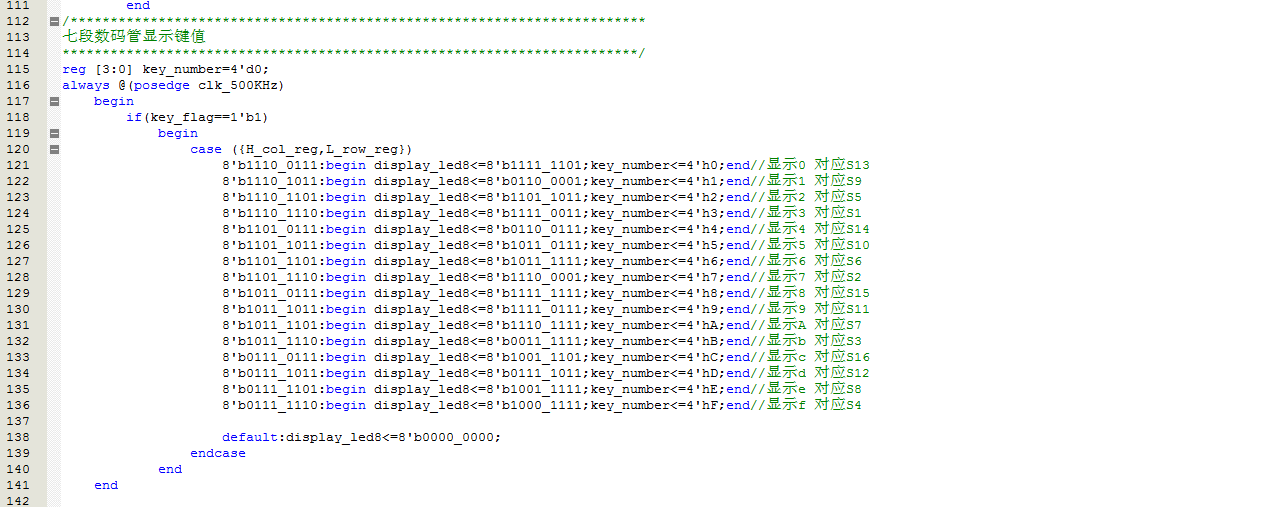

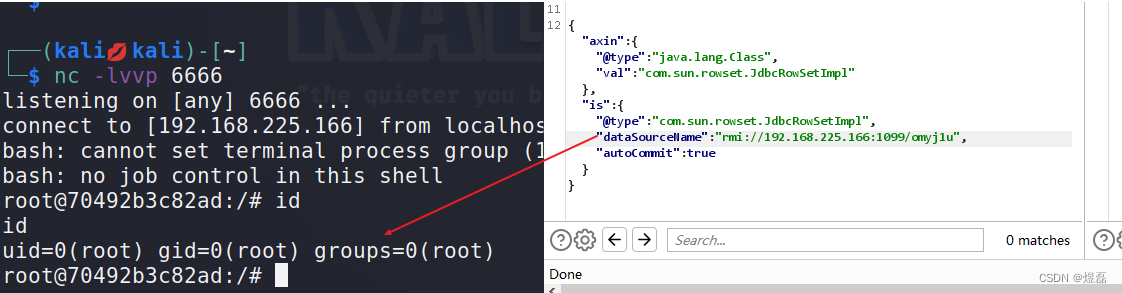

部分代码展示

module key_4x4 ( clk_500KHz,//500KHZ reset, //低电平复位 L_row, //行 H_col, //列 display_led8//数码管显示 ); input clk_500KHz; input reset; input [3:0] L_row;//行 output [3:0] H_col;//列 output [8:0] display_led8;//[7:0]:a,b,c,d,e,f,g,an0 reg [3:0] H_col=4'd0; reg [7:0] display_led8=8'd0; parameter s_L_all=3'd0; parameter s_L_row1=3'd1; parameter s_L_row2=3'd2; parameter s_L_row3=3'd3; parameter s_L_row4=3'd4; parameter s_LH=3'd5;reg [2:0] state=s_L_all; //状态标志 reg key_flag=0; //按键标志位 reg [3:0] H_col_reg=4'd0; //寄存扫描列值 reg [3:0] L_row_reg=4'd0;//寄存扫描行值 /************************************************************************ 逐行扫描原理 ************************************************************************/ always @(posedge clk_500KHz or negedge reset) if(!reset) begin H_col<=4'b0000; H_col_reg<=4'b0000; L_row_reg<=4'b0000; state<=s_L_all; end else begin case (state) s_L_all:begin H_col[3:0]<=4'b0000; key_flag<=1'b0; if(L_row[3:0]!=4'b1111) begin state<=s_L_row1; H_col[3:0]<=4'b0111;//有键按下,扫描第一行 end else state<=s_L_all; end s_L_row1:begin if(L_row[3:0]!=4'b1111) begin state<=s_LH;//判断是否是第一行 end else begin state<=s_L_row2; H_col[3:0]<=4'b1011; //扫描第二行 end end s_L_row2:begin if(L_row[3:0]!=4'b1111) begin state<=s_LH;//判断是否是第二行

设计文档:

![]()

4x4矩阵键盘设计.doc

1.要求

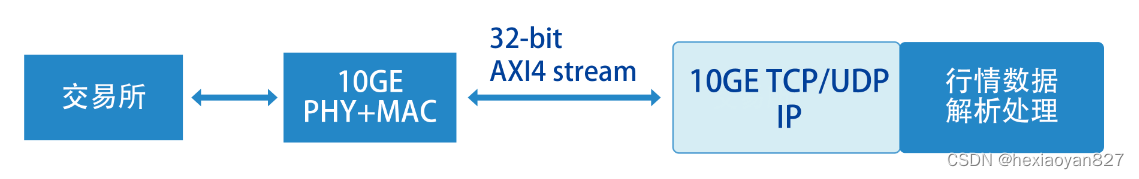

2.键盘电路

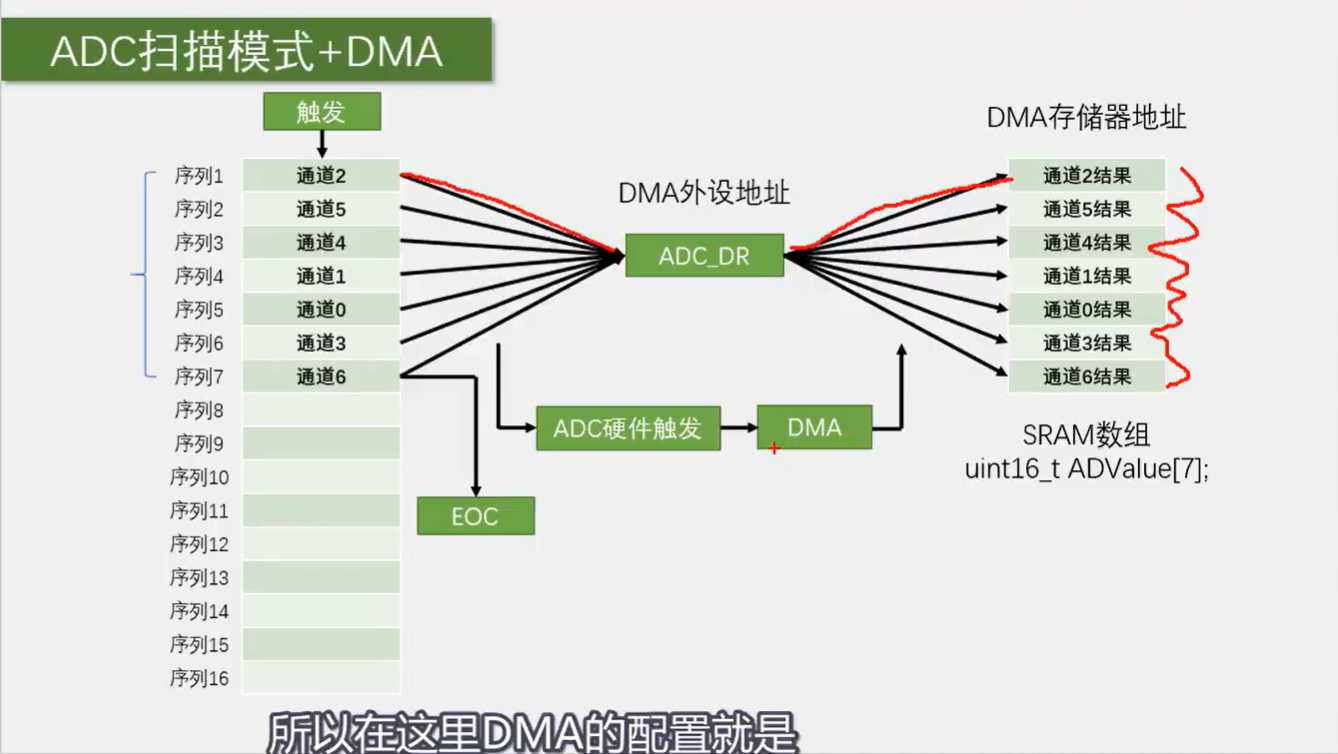

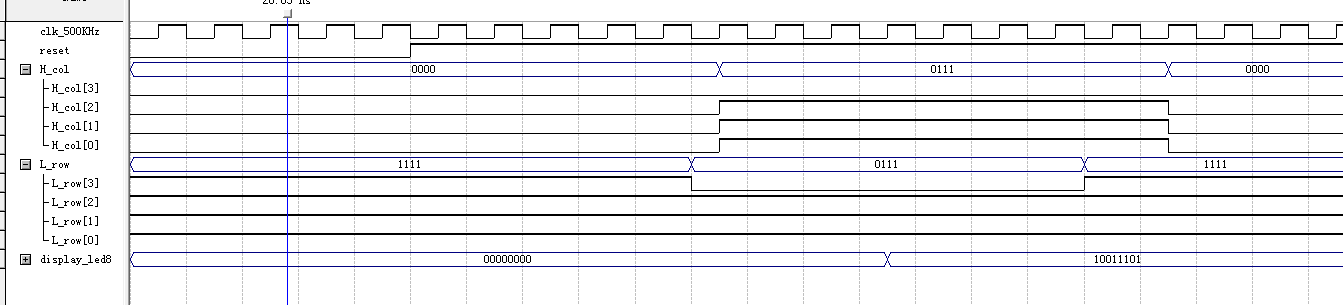

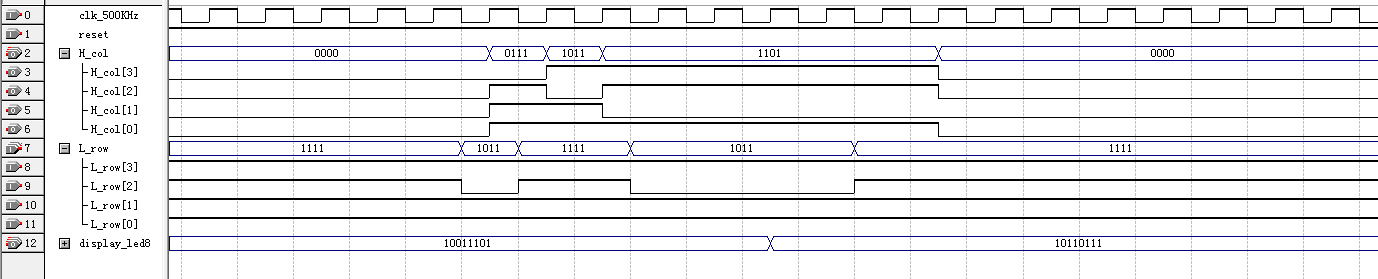

其中H0~H3为FPGA输出,L0~L3为FPGA输入,采用行扫描法。

在上电默认情况下,L[3:0] =1111,因为上拉了3.3V,而默认情况下H[3:0]为低电平;一旦有某一个按键被按下,则对应L会拉低。因此可以通过对每一行H输出的控制,来检索是哪一个按键被按下了。

3.工程文件

4.程序代码

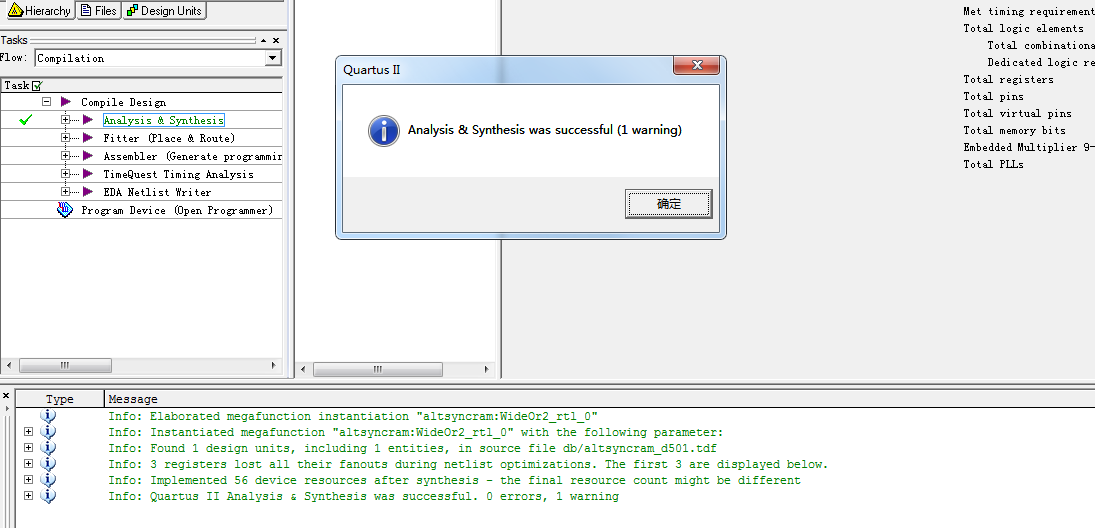

5.程序综合编译

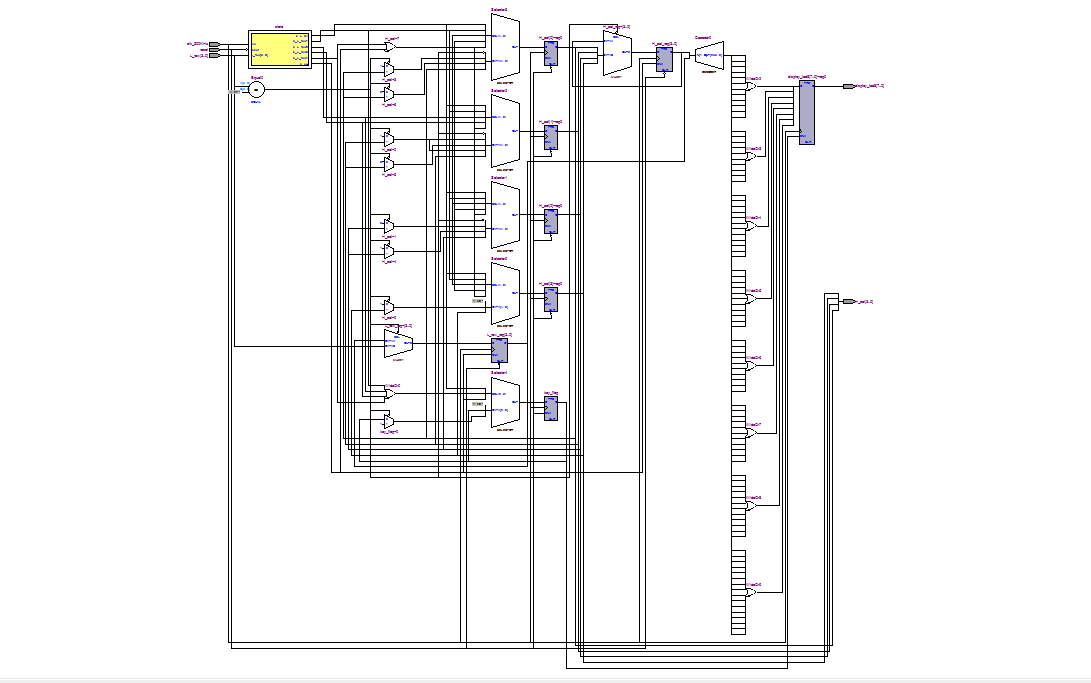

6.RTL图

7.状态机图

8.仿真

![[补题记录] Atcoder Beginner Contest 294(E)](https://img-blog.csdnimg.cn/82df4c726b2242879d6ebe6ef1ab80ea.png)