引言

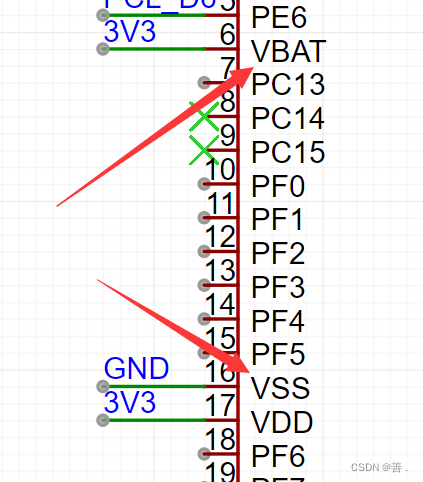

在学习设计TM32时,发现芯片除了GPIO引脚外还会引出许多引脚,以STM32F407ZGT6为例除了GPIO引脚还会有以下引脚

如VSS、VDD、VBAT、VSSA、NRST、VREF+、VDDA、VCAP_1、VCAP_2、PDR_ON这些引脚。他们有何作用,电路设计中应如何连接,学习并记录一下。

先说电路设计时这些引脚应该如何连接

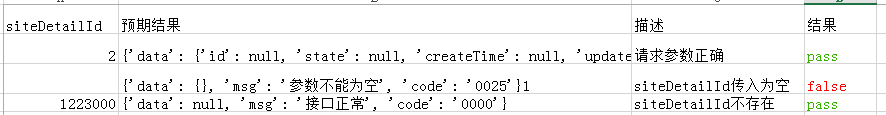

| 引脚 | 电平 | 说明 |

| VSS | GND | 表示公共连接的意思,通常指电路公共接地端电压。 |

| VDD | 3.3V | 用于I/O和内部稳压器的外部电源(启用时),通过VDD引脚从外部提供。 |

| VBAT | 3.3V | 当VDD不存在时,用于RTC、外部时钟32 kHz振荡器和备用寄存器(通过电源开关)的电源。 |

| VSSA | GND | 同VSS |

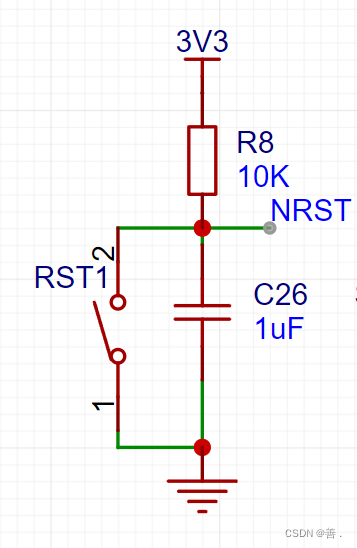

| NRST | 复位引脚 | |

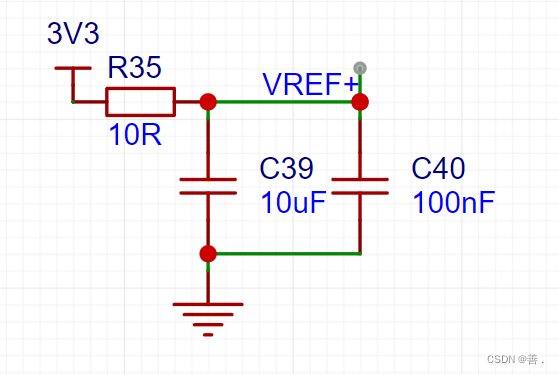

| VREF+ | 3.3V | ADC基准参考正电压 |

| VDDA | 3.3V | 同VDD |

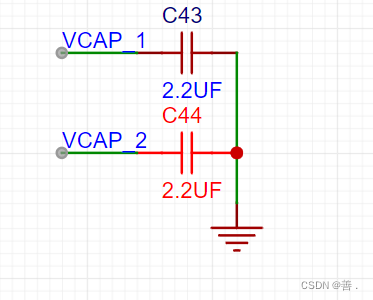

| VCAP_1 | GND | 需要串联电容在接地 |

| VCAP_2 | GND | 需要串联电容在接地 |

| PDR_ON | 3.3V | 打开内部电源管理器 |

我觉得看引脚的作用最好的办法是看官方提供的芯片手册,如何找芯片手册可以参考下面的文章

STM32芯片引脚定义_善 .的博客-CSDN博客

VSS、VDD、VBAT、VSSA、VDDA

通过查询手册我们可以找到

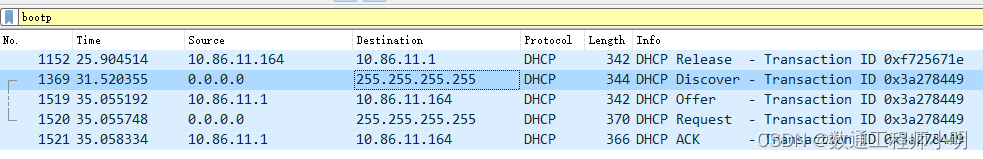

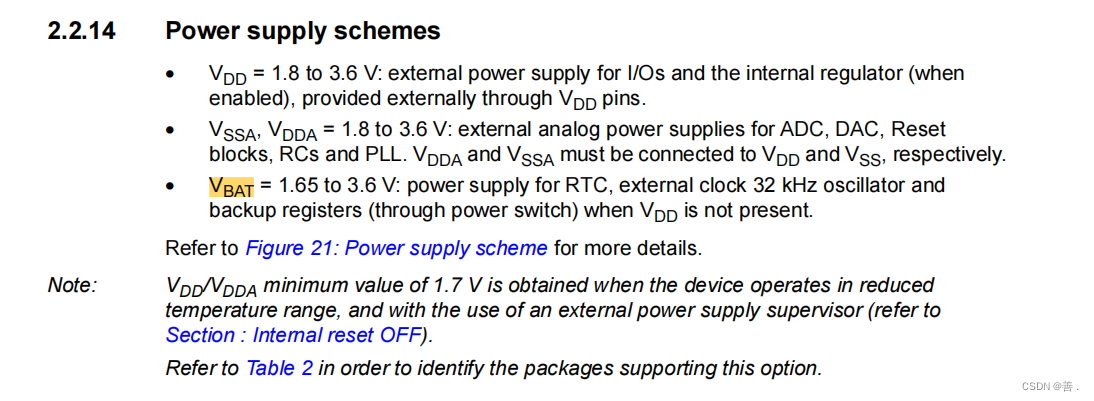

2.2.14供电方案

•VDD=1.8至3.6 V:用于I/O和内部稳压器的外部电源(启用时),通过VDD引脚从外部提供。

VSSA,VDDA=1.8至3.6伏:用于ADC、DAC、复位块、RC和PLL的外部模拟电源。VDDA和VSSA必须分别连接到VDD和VSS。(这里只是说VDDA=1.8至3.6伏,而不是说VSSA,VDDA两个的范围都在1.8至3.6伏)

VBAT=1.65至3.6 V:当VDD不存在时,用于RTC、外部时钟32 kHz振荡器和备用寄存器(通过电源开关)的电源。

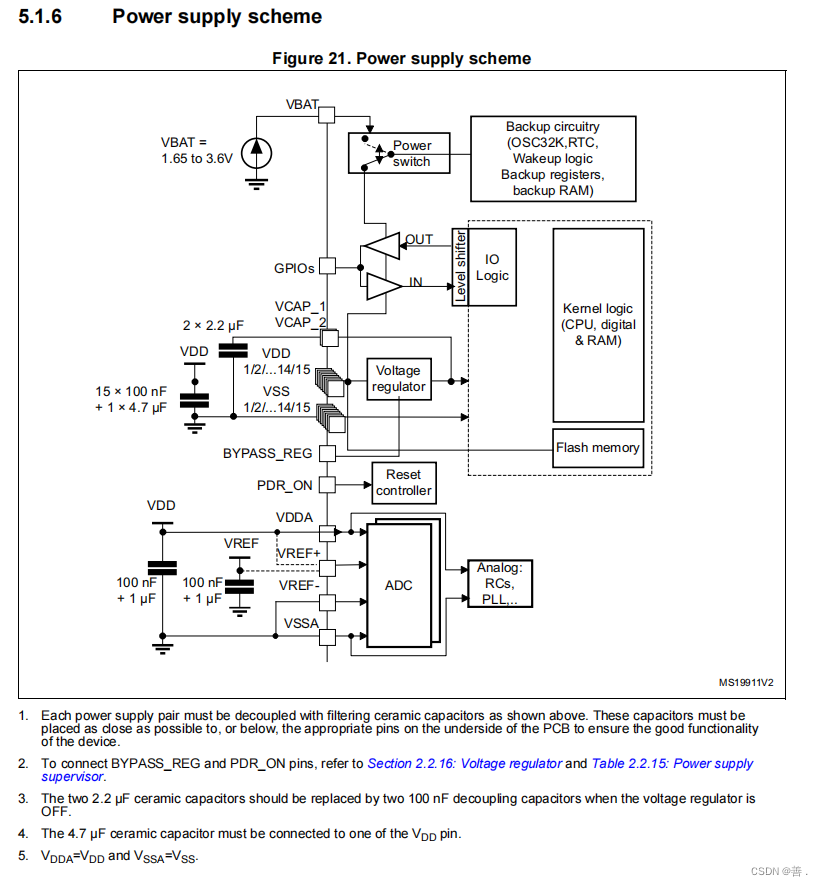

有关详细信息,请参阅图21:电源方案。

注:VDD/VDDA的最小值为1.7 V,当器件在降低的温度范围内工作时,并使用外部电源监控器(请参阅部分:内部复位关闭)。

请参阅表2以确定支持此选项的包。

接下来找一下图21:电源方案。

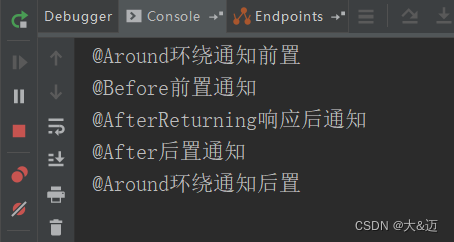

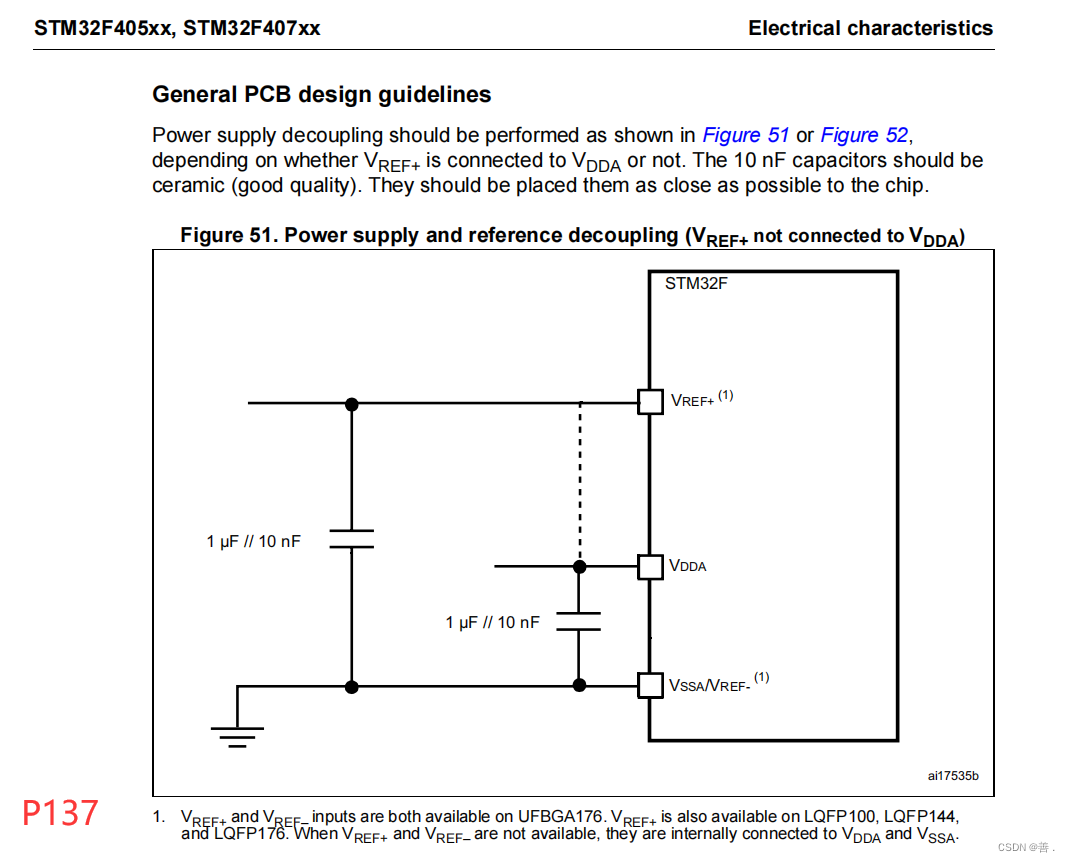

1.每个电源对必须用如上所示的过滤陶瓷电容器解耦。这些电容器必须尽可能靠近或低于PCB底部的适当引脚,以确保设备的良好功能。

2.要连接BYPASS_REG和PDR_ON引脚,请参阅第2.2.16节:电压调节器和表2.2.15:电源监控器。

3.当稳压器关断时,两个2.2µF陶瓷电容器应替换为两个100 nF去耦电容器。

4.4.7µF陶瓷电容器必须连接到VDD引脚之一。

5. VDDA=VDD和VSSA=VSS。

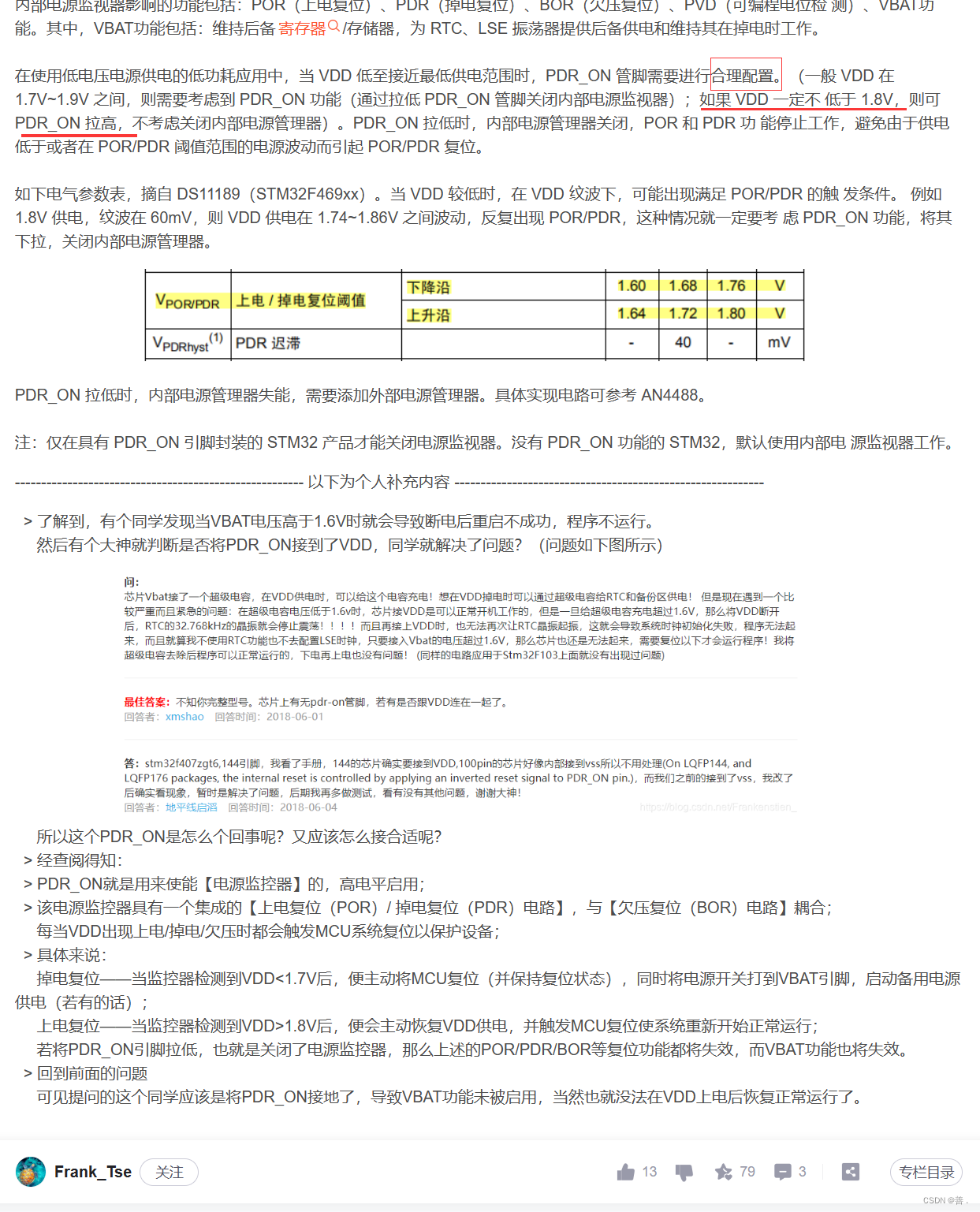

这次使用的STM32F407ZGT6没有BYPASS_REG引脚(会出现在LQFP176引脚上),所以直接看PDR_ON表2.2.15:电源监控器。

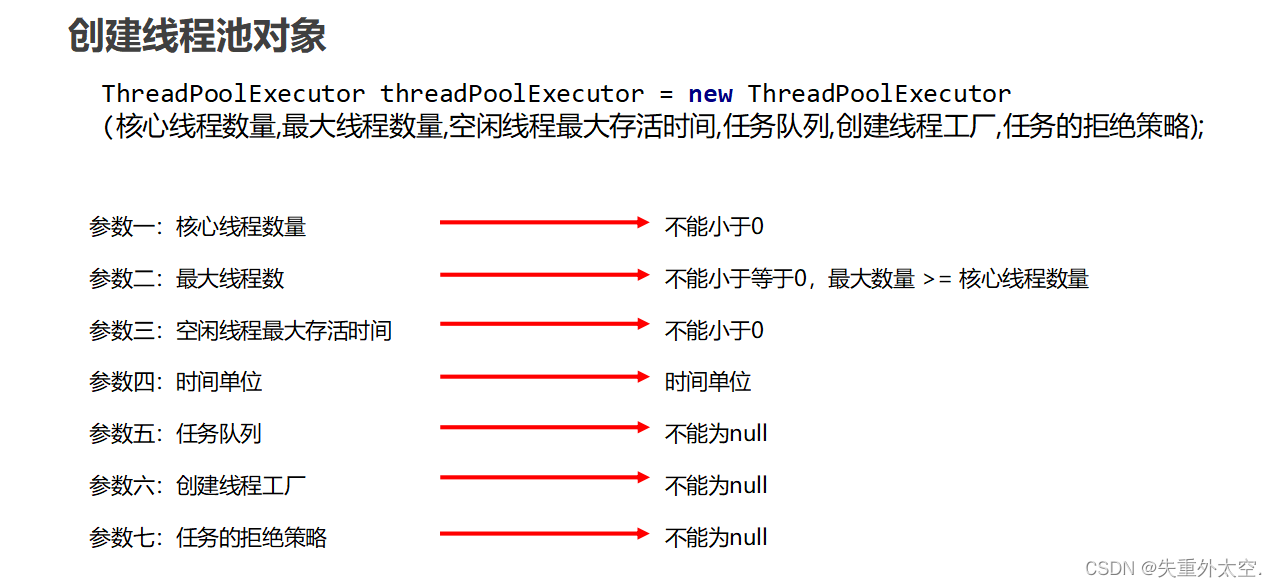

VDDA模拟电源电压

PDR_ON

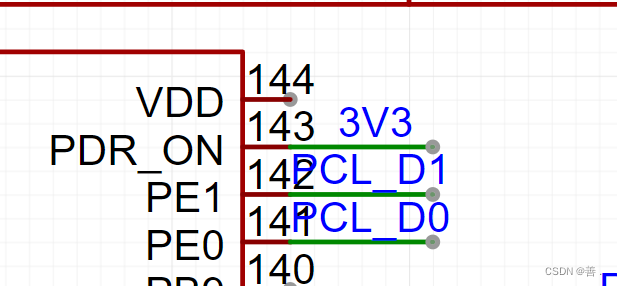

143_PDR_ON引脚手册上的解释有点难懂,可以参考下面的博主解释

STM32的PDR_ON引脚,比较好的解释(转载+补充)-CSDN博客

简而言之在设计电路时将PDR_ON引脚拉高既可。

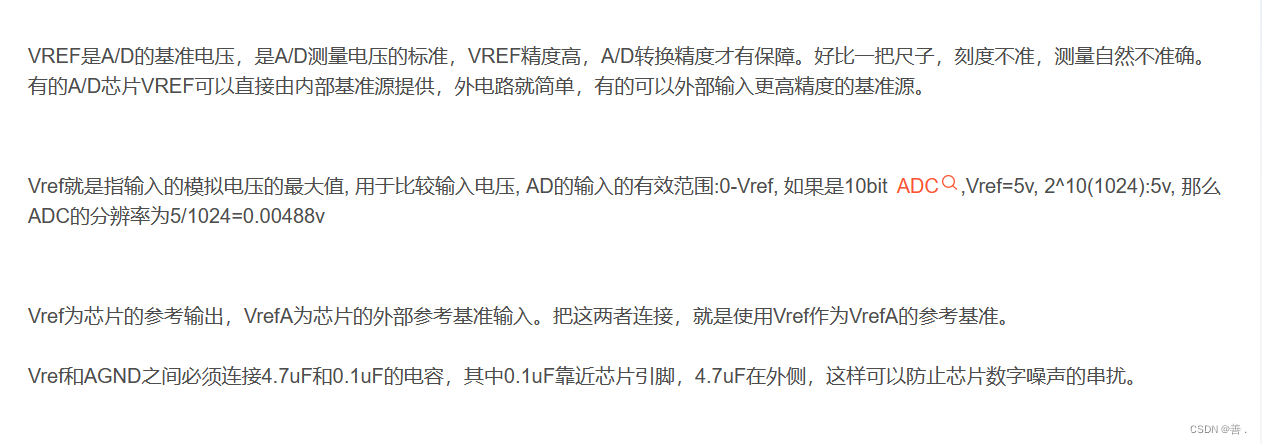

VREF+

32_VREF是ADC的参考电压

VREF_vref为什么是输入-CSDN博客

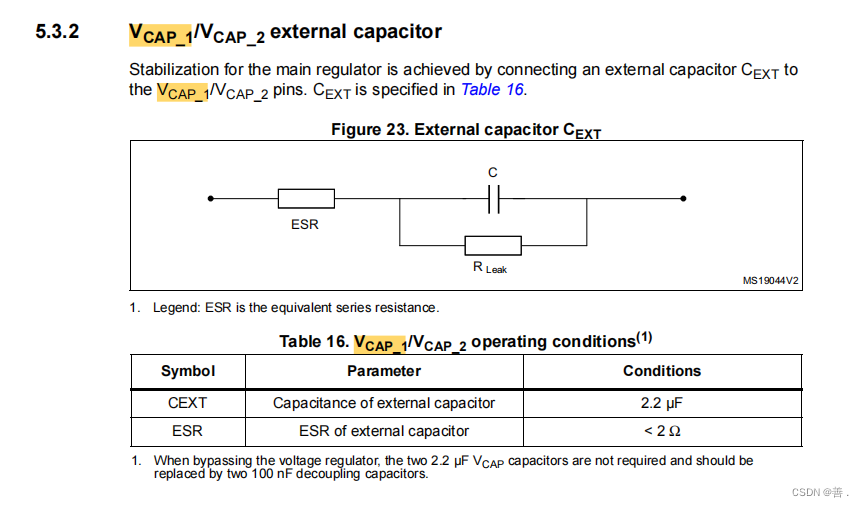

VCAP_1/VCAP_2

STM32之VCP1/VCAP2引脚的处理 - 杰瑞鼠 - 博客园 (cnblogs.com)

ST MCU芯片的VCAP管脚话题_stm32vcap不接可以吗-CSDN博客

STM32H7硬件设计时,特别注意Vcap引脚的电容要使用低ESR(等效串行电阻) - STM32H7 - 硬汉嵌入式论坛 - Powered by Discuz! (armbbs.cn)

NRST

复位引脚NRST输入低电平的时候,MCU处于复位状态,重设所有的内部寄存器,及片内几十KB的SRAM。 当NRST从低电平变高时,PC指针从0开始。

电路设计

参考资料:

GD32,在电源电路VDD VDDA VREF+/-参考设计_vdda和vdd怎么连接_学海无涯_come on的博客-CSDN博客

画板时STM32的VDDA,VREF引脚怎么处理好呢? (stmicroelectronics.cn)

去耦电容与滤波电容的本质都是用于稳压,滤波电容是对于电源而言的,而去耦电容是针对用电器(如芯片、模块)而言。

【分立元件】滤波电容和去耦电容有啥差异?作用是什么?_去耦电容和滤波电容的区别-CSDN博客

名词解释

STM32电源框图解析(VDD、VSS、VDDA、VSSA、VREF+、VREF-、VBAT等的区别)-CSDN博客