文章目录

- 前言

- 一、HDL方面

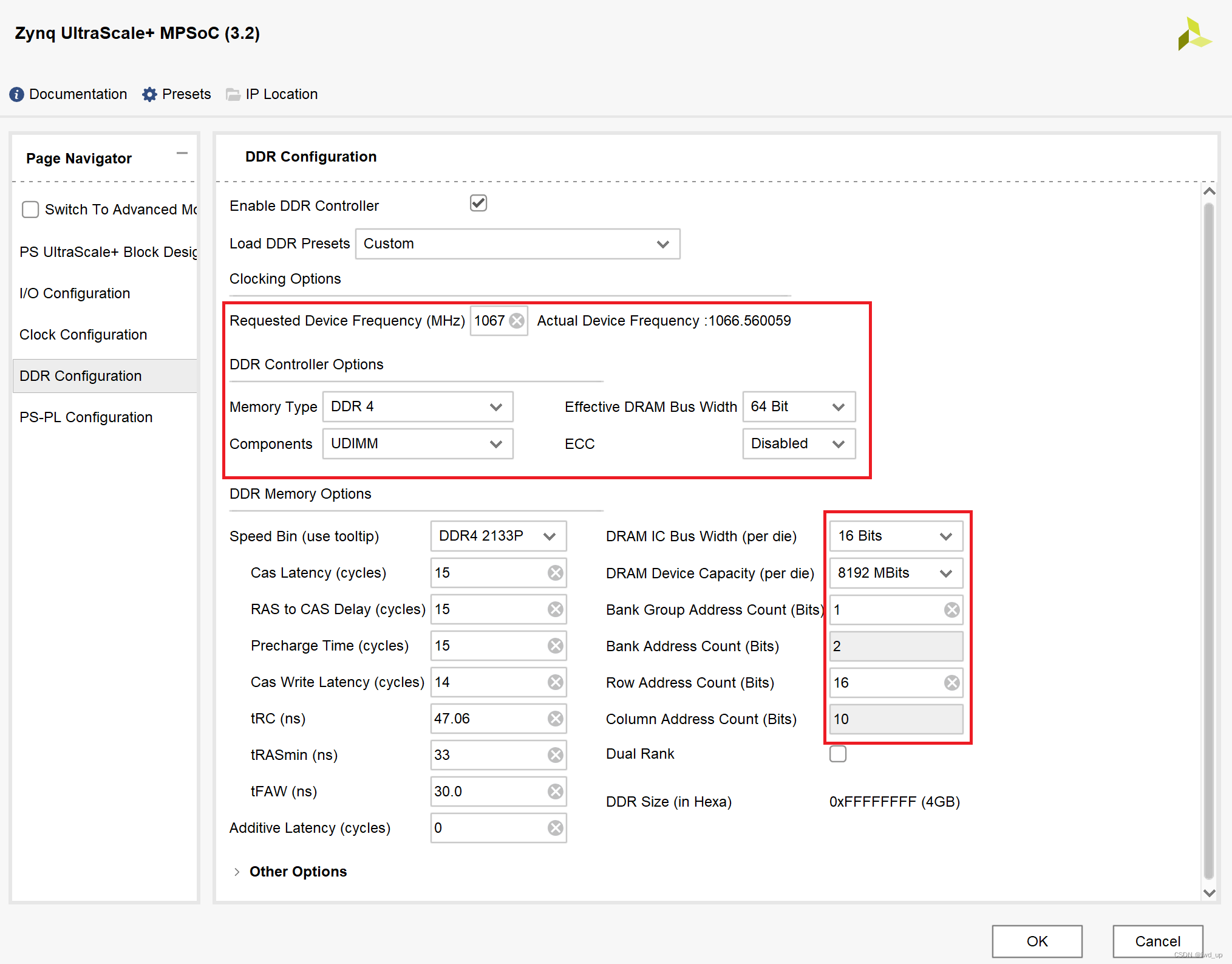

- 1. ZYNQ 核根据ZCU106平台修改(**参考UG1244 ZCU106 Evaluation Board**),尤其注意**DDR**的配置(**参考美光 MTA4ATF51264HZ**)

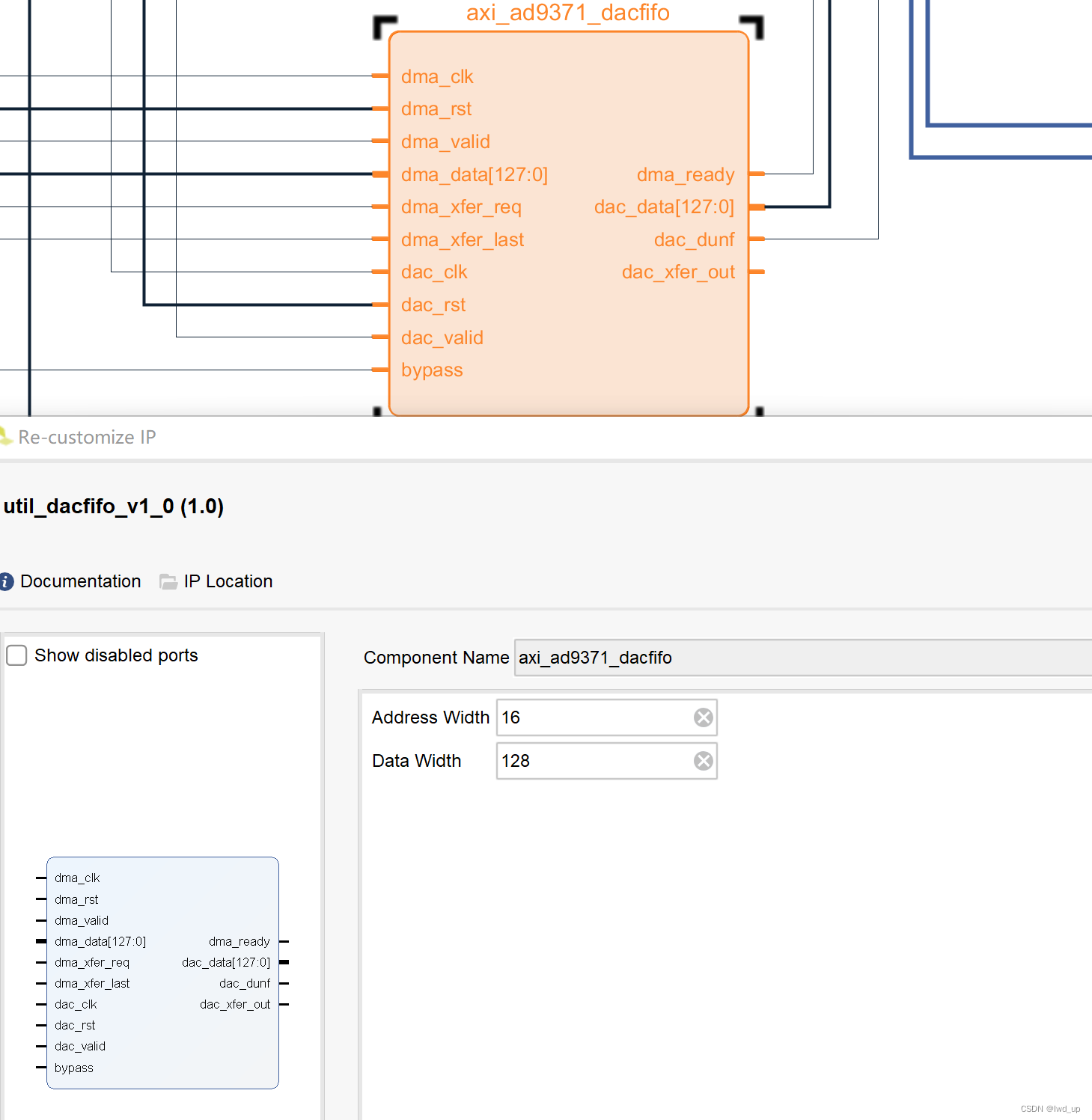

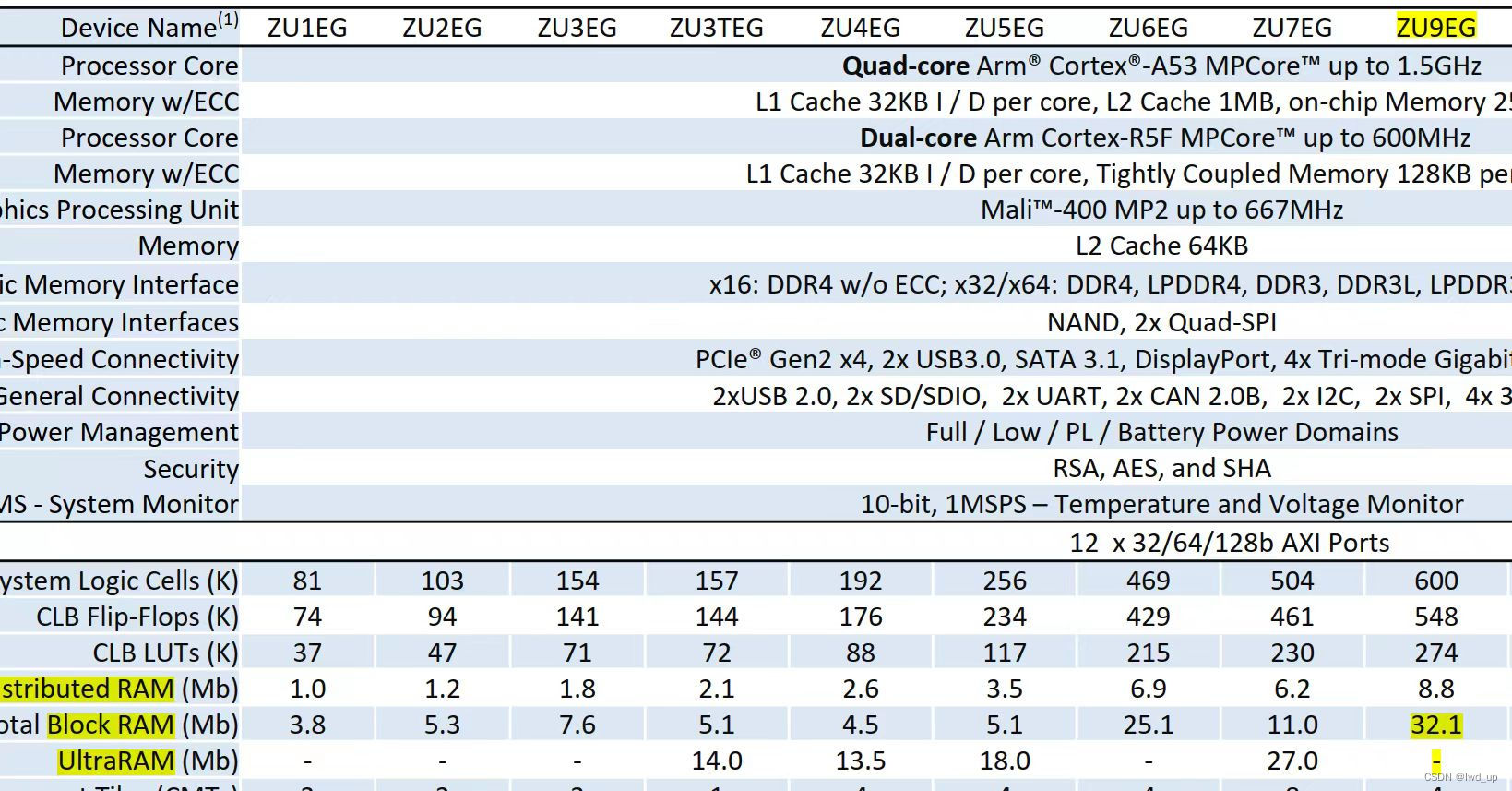

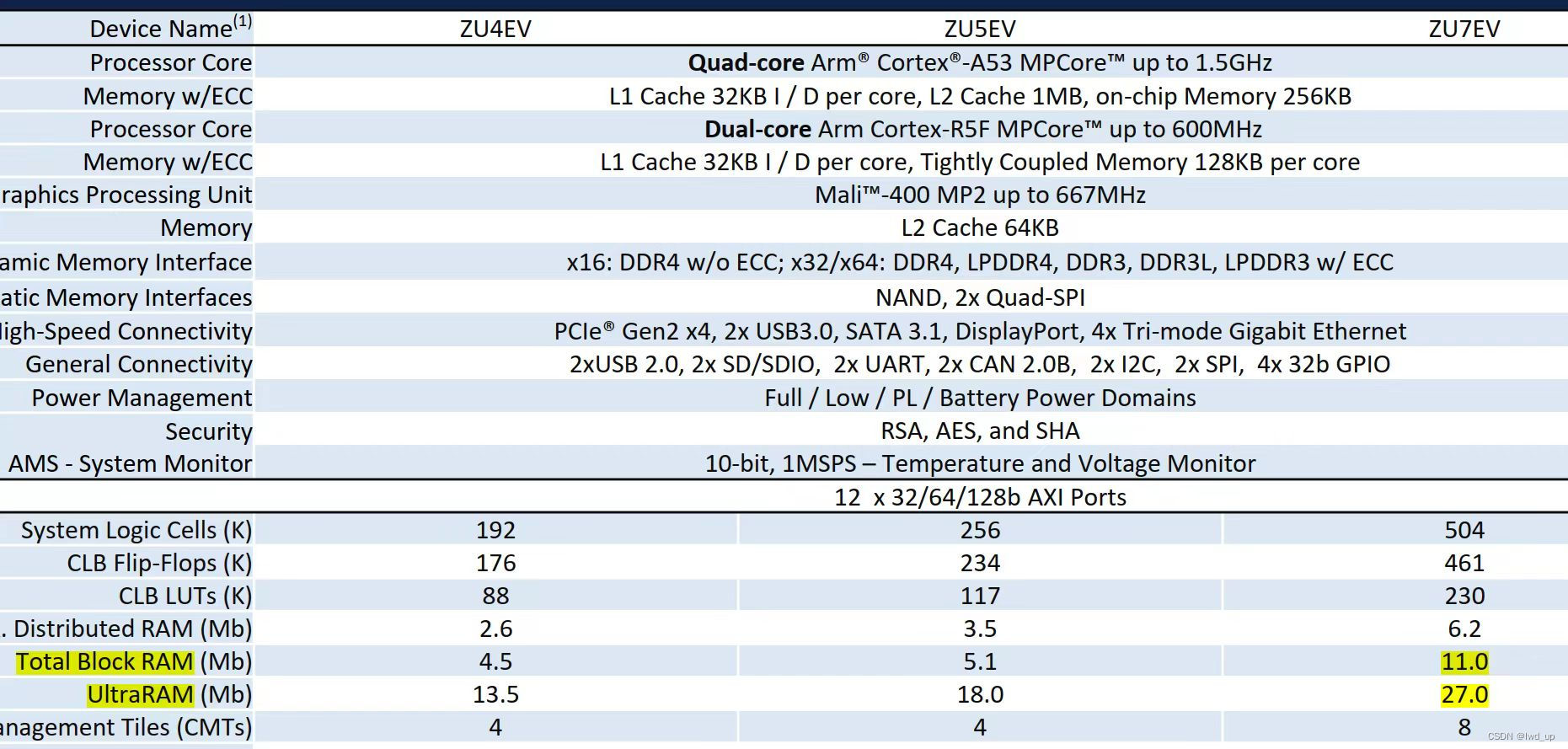

- 2.dacfifo 深度 要修改 ,地址位宽 小于等于16,zcu102中 fifo 128位数据 深度2^17 需要16.7Mb ,ZU9EG BRAM 32Mb可以满足 , zcu106 BRAM 11Mb,16.7Mb 超出了106能力 ,深度改成16就可以了

- 3. XDC引脚要修改正确

- 4. RX接收不到正弦,测试发现TX有问题,HDL侧修改方案

- 二、SW方面

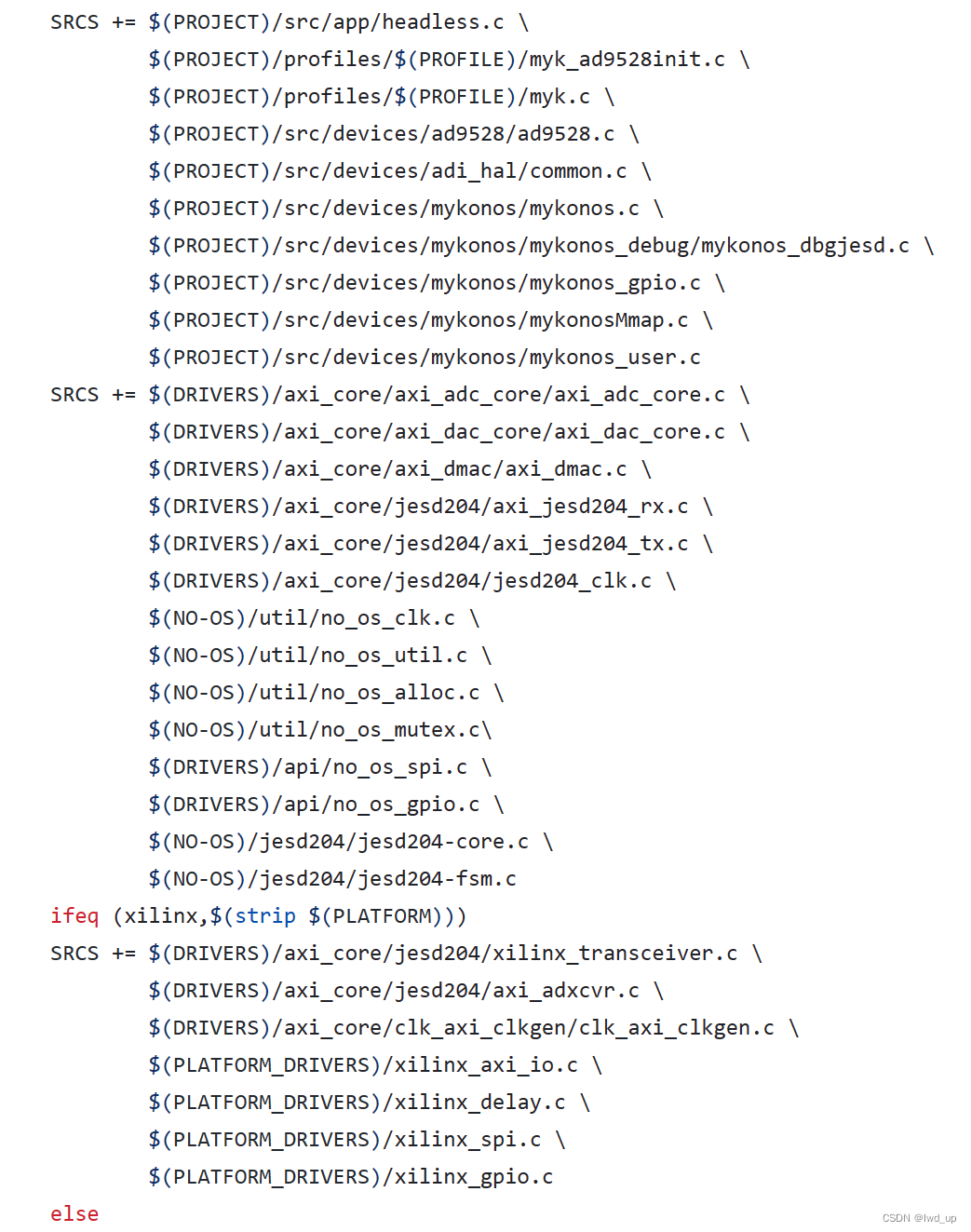

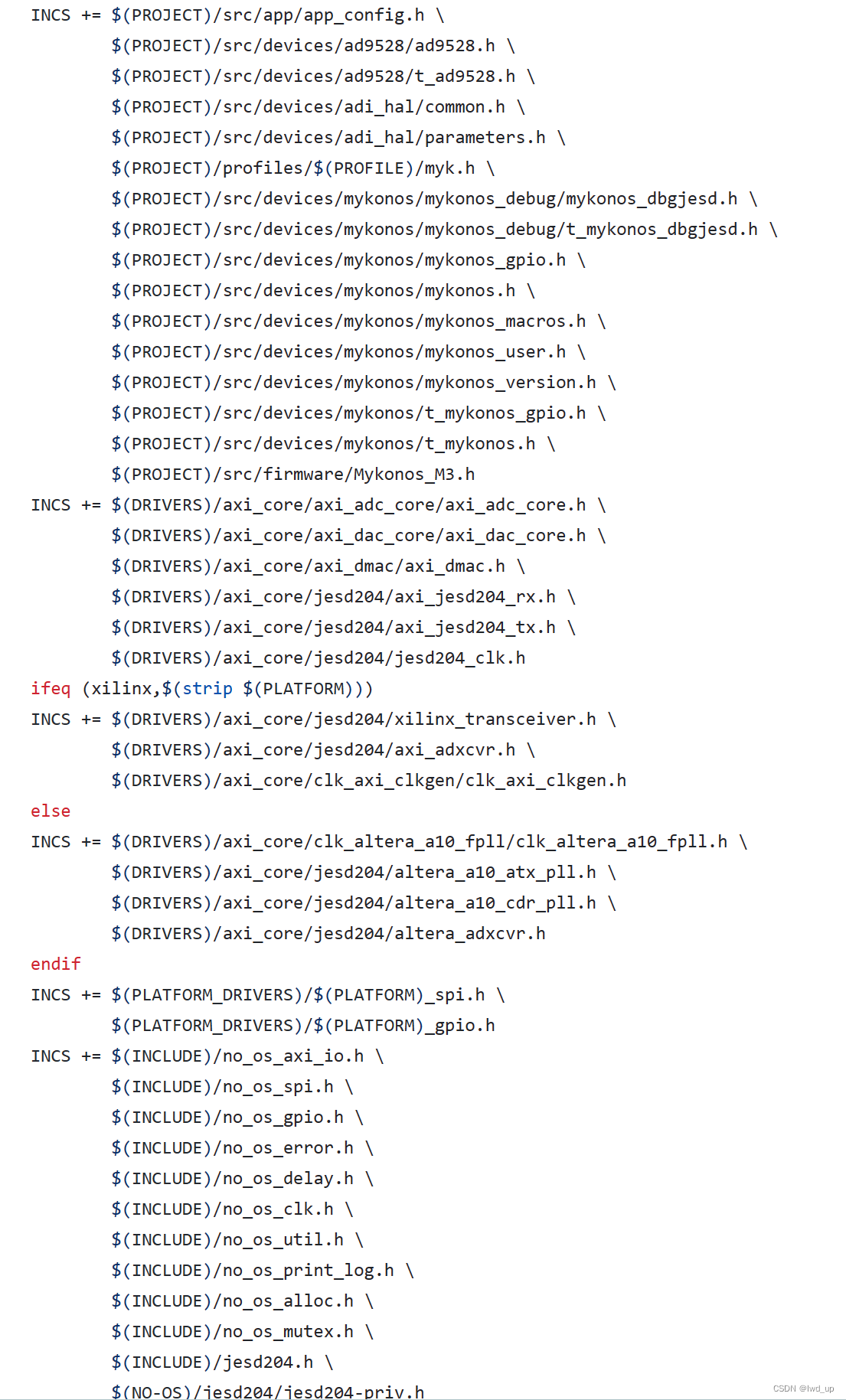

- 1. 不使用iio时,确保所有需要的 .c 和 .h文件都添加进来

- 2. 添加#define XPS_BOARD_ZCU102

- 3. app_config.h打开 #define DMA_EXAMPLE

- 4. 打印RX数据

- 5. RX接收不到正弦,测试发现TX有问题,SW侧修改方案

- 总结

前言

项目构建基本流程和AD9361差不多,由于官方使用的ZCU102,记录下移植遇到的一些问题

一、HDL方面

1. ZYNQ 核根据ZCU106平台修改(参考UG1244 ZCU106 Evaluation Board),尤其注意DDR的配置(参考美光 MTA4ATF51264HZ)

2.dacfifo 深度 要修改 ,地址位宽 小于等于16,zcu102中 fifo 128位数据 深度2^17 需要16.7Mb ,ZU9EG BRAM 32Mb可以满足 , zcu106 BRAM 11Mb,16.7Mb 超出了106能力 ,深度改成16就可以了

3. XDC引脚要修改正确

示例如下:

set_property -dict {PACKAGE_PIN U2 } [get_ports rx_data_p[0]] ; ## A02 FMC_HPC0_DP1_M2C_P

set_property -dict {PACKAGE_PIN U1 } [get_ports rx_data_n[0]] ; ## A03 FMC_HPC0_DP1_M2C_N

set_property -dict {PACKAGE_PIN P4 } [get_ports rx_data_p[1]] ; ## A06 FMC_HPC0_DP2_M2C_P

set_property -dict {PACKAGE_PIN P3 } [get_ports rx_data_n[1]] ; ## A07 FMC_HPC0_DP2_M2C_N

4. RX接收不到正弦,测试发现TX有问题,HDL侧修改方案

axi_ad9371_dacfifo 中 dac_rst_int_s 应该在dac_xfer_req 上升沿有效,代码也产生了上升沿,但是 assign dac_rst_int_s = dac_xfer_req | dac_rst;用错了信号

assign dac_xfer_posedge_s = ~dac_xfer_req_d & dac_xfer_req;// we can reset the DAC side at each positive edge of xfer_req, even if// sometimes the reset is redundantassign dac_rst_int_s = dac_xfer_req | dac_rst;

做如下修改可以正确发送接收正弦波

assign dac_rst_int_s = dac_xfer_posedge_s | dac_rst;

二、SW方面

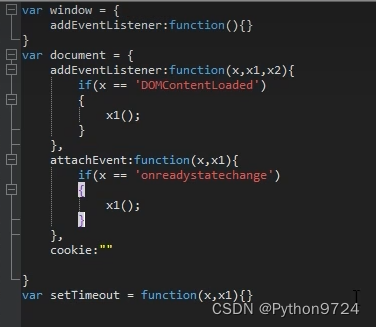

1. 不使用iio时,确保所有需要的 .c 和 .h文件都添加进来

需要的头文件如下

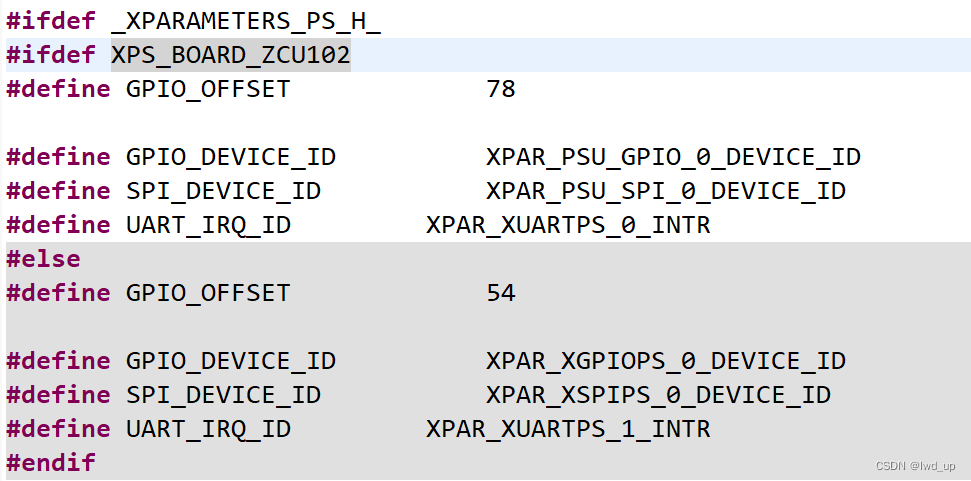

2. 添加#define XPS_BOARD_ZCU102

默认的是 zynq7000 系列,ZCU106是 Zynq UltraScale+ ,和102一样 GPIO 有78个 ,而不是7000系列的54个

3. app_config.h打开 #define DMA_EXAMPLE

通过DDR 发送 接收正弦信号

4. 打印RX数据

接收数据 存到 adc_buffer 后 ,添加下列代码 ,测试知道 I1、Q1 是 RX1 路信号 ,I2、Q2 是 RX2 路信号

uint16_t index;uint32_t data_1;uint32_t data_2;uint16_t Q1;uint16_t I1;uint16_t Q2;uint16_t I2;for(index =0; index < 8192; index += 1){// R1data_1 =Xil_In32(adc_buffer+ index*(4));// R2data_2 =Xil_In32(adc_buffer+2+ index*(4));Q1 = (data_1) & 0xFFFF;I1 = (data_1 >> 16) & 0xFFFF;Q2 = (data_2) & 0xFFFF;I2 = (data_2 >> 16) & 0xFFFF;printf("%d,%d\n",(signed short)I1,(signed short)Q1);// printf("%d,%d\n",(signed short)I2,(signed short)Q2);5. RX接收不到正弦,测试发现TX有问题,SW侧修改方案

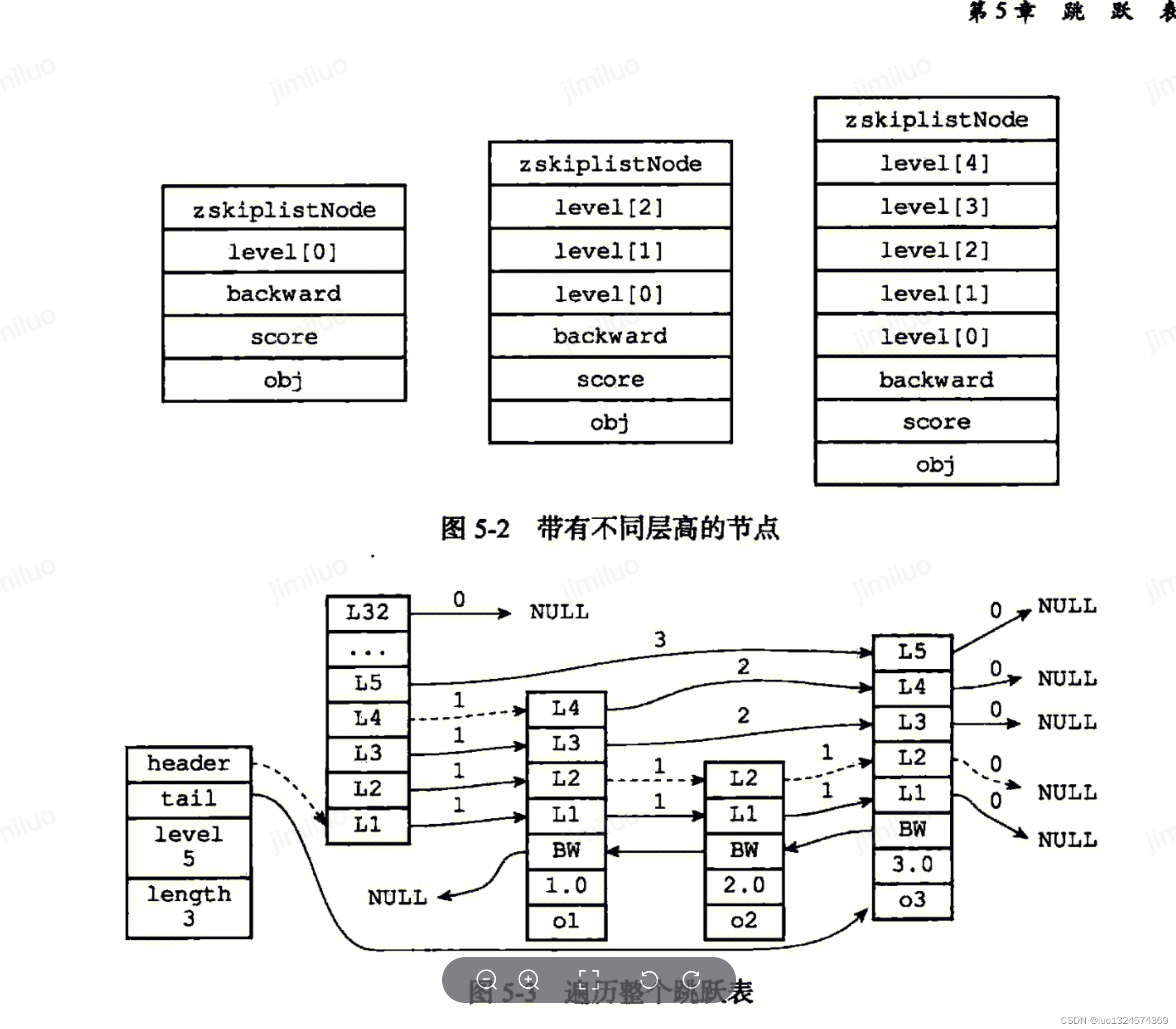

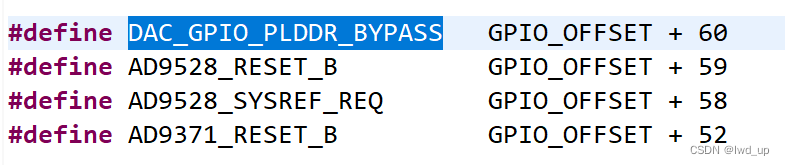

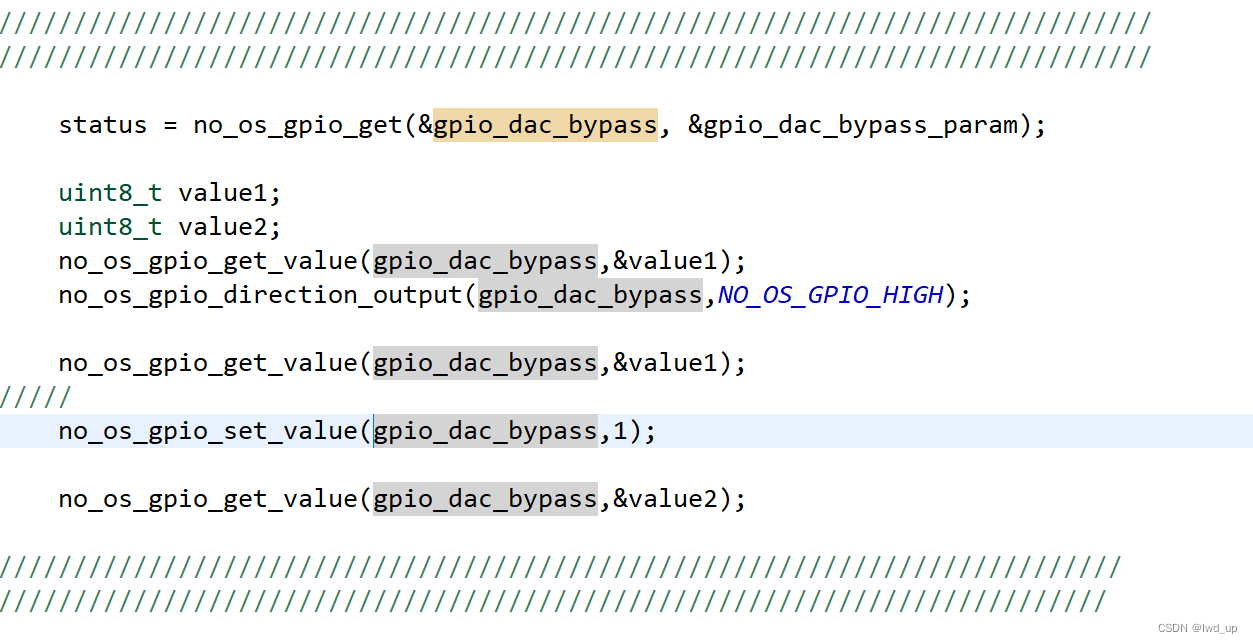

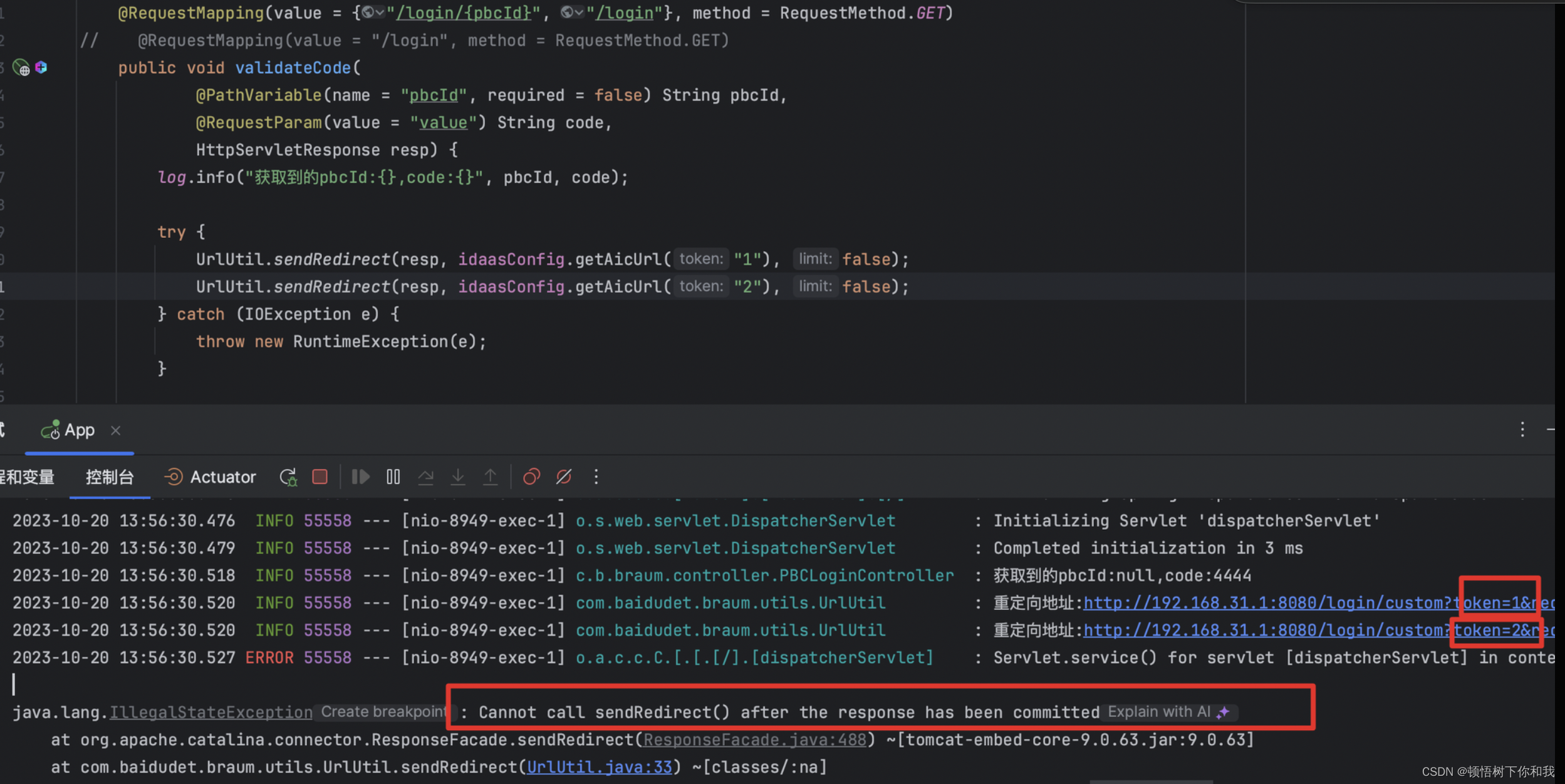

该方法可以不修改HDL以接收数据,通过 拉高 axi_ad9371_dacfifo 的 dac_fifo_bypass 信号,把dacfifo 旁路 ,使用PL DDR, dac_fifo_bypass (gpio_o[60])信号 连接到EMIO 60 引脚

在 common.c 通过以下代码,只要拉高 DAC_GPIO_PLDDR_BYPASS 就可以

最终接收到正确的正弦波

总结

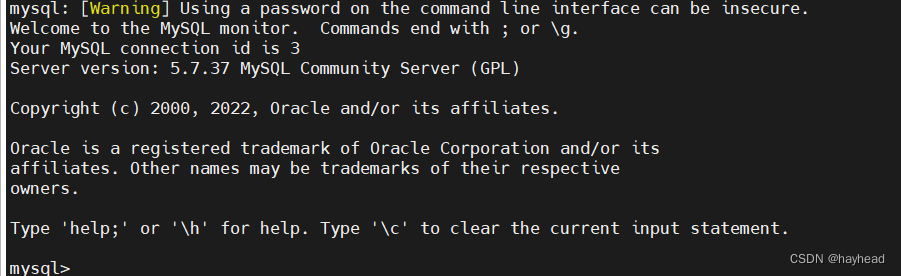

打印信息及部分接收数据如下:

Please wait...

rx_clkgen: MMCM-PLL locked (122880000 Hz)

tx_clkgen: MMCM-PLL locked (122880000 Hz)

rx_os_clkgen: MMCM-PLL locked (122880000 Hz)

MCS successful

CLKPLL locked

AD9371 ARM version 5.2.2

PLLs locked

Calibrations completed successfully

tx_adxcvr: OK (4915200 kHz)

rx_adxcvr: OK (4915200 kHz)

rx_os_adxcvr: OK (4915200 kHz)

rx_jesd status:Link is enabledMeasured Link Clock: 122.882 MHzReported Link Clock: 122.880 MHzLane rate: 4915.200 MHzLane rate / 40: 122.880 MHzLMFC rate: 3.840 MHzLink status: DATASYSREF captured: YesSYSREF alignment error: No

rx_jesd lane 0 status:

Errors: 0CGS state: DATAInitial Frame Synchronization: YesLane Latency: 1 Multi-frames and 60 OctetsInitial Lane Alignment Sequence: YesDID: 0, BID: 0, LID: 0, L: 2, SCR: 1, F: 4K: 32, M: 4, N: 16, CS: 0, N': 16, S: 1, HD: 0FCHK: 0x47, CF: 0ADJCNT: 0, PHADJ: 0, ADJDIR: 0, JESDV: 1, SUBCLASS: 1FC: 4915200 kHz

rx_jesd lane 1 status:

Errors: 0CGS state: DATAInitial Frame Synchronization: YesLane Latency: 1 Multi-frames and 62 OctetsInitial Lane Alignment Sequence: YesDID: 0, BID: 0, LID: 1, L: 2, SCR: 1, F: 4K: 32, M: 4, N: 16, CS: 0, N': 16, S: 1, HD: 0FCHK: 0x48, CF: 0ADJCNT: 0, PHADJ: 0, ADJDIR: 0, JESDV: 1, SUBCLASS: 1FC: 4915200 kHz

tx_jesd status:Link is enabledMeasured Link Clock: 122.882 MHzReported Link Clock: 122.880 MHzLane rate: 4915.200 MHzLane rate / 40: 122.880 MHzLMFC rate: 7.680 MHzSYNC~: deassertedLink status: DATASYSREF captured: YesSYSREF alignment error: No

rx_os_jesd status:Link is enabledMeasured Link Clock: 122.882 MHzReported Link Clock: 122.880 MHzLane rate: 4915.200 MHzLane rate / 40: 122.880 MHzLMFC rate: 7.680 MHzLink status: DATASYSREF captured: YesSYSREF alignment error: No

rx_os_jesd lane 0 status:

Errors: 0CGS state: DATAInitial Frame Synchronization: YesLane Latency: 1 Multi-frames and 56 OctetsInitial Lane Alignment Sequence: YesDID: 0, BID: 0, LID: 0, L: 2, SCR: 1, F: 2K: 32, M: 2, N: 16, CS: 0, N': 16, S: 1, HD: 0FCHK: 0x43, CF: 0ADJCNT: 0, PHADJ: 0, ADJDIR: 0, JESDV: 1, SUBCLASS: 1FC: 4915200 kHz

rx_os_jesd lane 1 status:

Errors: 0CGS state: DATAInitial Frame Synchronization: YesLane Latency: 1 Multi-frames and 56 OctetsInitial Lane Alignment Sequence: YesDID: 0, BID: 0, LID: 1, L: 2, SCR: 1, F: 2K: 32, M: 2, N: 16, CS: 0, N': 16, S: 1, HD: 0FCHK: 0x44, CF: 0ADJCNT: 0, PHADJ: 0, ADJDIR: 0, JESDV: 1, SUBCLASS: 1FC: 4915200 kHz

tx_dac: Successfully initialized (245761108 Hz)

rx_adc: Successfully initialized (122880554 Hz)

rx_obs_adc: Successfully initialized (245761108 Hz)

DMA_EXAMPLE: address=0x951c0 samples=65536 channels=4 bits=16

-18117,3451

-17698,5151

-17096,6857

-16361,8534

-15434,10086

-14402,11551

-13177,12919

-11829,14102

-10392,15189

-8848,16154

-7210,16969

-5504,17584

-3765,18051

-1961,18287

-175,18424

1635,18318

3432,18072

5188,17708

6919,17098

8553,16336

10107,15413

11573,14342

12918,13125

14147,11799

15245,10342

16237,8837

17001,7196

17608,5486

18094,3749

18334,1975

18487,128

18392,-1647

18159,-3463

17751,-5212

17152,-6911

16383,-8563

15498,-10134

14396,-11593

13220,-12928

11890,-14153

10462,-15289

8915,-16206

7322,-17008

5597,-17616

3843,-18055

2049,-18359

208,-18486

-1597,-18385

-3384,-18154

-5144,-17736

-6883,-17116

-8512,-16378

-10099,-15478

-11530,-14371

-12915,-13163

-14123,-11814

-15224,-10370

-16193,-8831

-16949,-7171

-17597,-5469

-18043,-3711

-18318,-1956

-18416,-126

-18360,1690

-18093,3470

-17657,5239

-17077,6927

-16303,8547

-15401,10154

-14326,11592

-13135,12959

-11789,14159

-10347,15238

-8776,16182

-7128,16984

-5431,17609

-3664,18039

-1852,18307

-77,18410

1769,18326

3558,18070

5310,17659

7008,17031

8640,16247

10209,15360

11679,14281

13015,13038

14242,11739

15307,10260

16260,8709

17013,7079

17657,5354

18096,3613

18381,1844

18471,0

18412,-1802

18148,-3601

17726,-5336

17114,-7041

16350,-8699

15434,-10224

14344,-11687

13164,-13017

11801,-14242

10369,-15354

8791,-16253

7134,-17076

5450,-17695

3700,-18097

1928,-18389

105,-18462

-1690,-18410

-3495,-18122

-5252,-17714

-6966,-17080

-8612,-16332

-10163,-15386

-11616,-14299

-12972,-13086

-14189,-11752

-15279,-10297

-16198,-8744

-16996,-7137

-17602,-5424

-18023,-3645

-18328,-1866

-18405,-85

-18320,1732

-18067,3517

-17656,5241

-17076,6934

-16303,8584

-15368,10136

-14339,11574

-13141,12961

-11737,14147

-10331,15251

-8797,16171

-7128,16999

-5417,17584

-3682,18046

-1886,18334

-66,18421

1735,18340

3518,18079

5290,17624

6970,17037

8636,16267

10160,15359

11651,14290

12989,13049

14190,11708

15307,10256

16208,8732

17011,7094

17615,5372

18116,3629

18398,1806

18452,11

18394,-1787

18122,-3563

17716,-5320

17121,-7010

16349,-8669

15410,-10214

14356,-11684

13145,-13011

11781,-14234

10371,-15356

8791,-16261

7188,-17026

5478,-17658

3738,-18103

1952,-18372

134,-18457

-1659,-18380

-3410,-18116

-5168,-17684

-6886,-17116

-8508,-16335

-10080,-15440

-11556,-14347

-12904,-13165

-14132,-11820

-15191,-10413

-16134,-8849

-16934,-7232

-17560,-5544

-18020,-3823

-18333,-1991

-18421,-183

-18366,1582

-18106,3389

-17701,5123

-17113,6861

-16372,8496

-15445,10045

-14416,11513

-13204,12877

-11857,14078

-10459,15164

-8900,16136

-7306,16889

-5626,17552

-3848,18001

-2051,18295

-242,18410

1560,18341

3314,18118

5102,17690

6836,17117

8493,16355

10034,15430

11512,14373

12864,13181

14106,11841

15204,10389

16170,8881

16934,7253

17572,5554

18078,3803

18333,1992

18491,218

18411,-1606

18161,-3403

17758,-5126

17166,-6845

16444,-8505

15528,-10079

14475,-11557

13256,-12921

11936,-14143

10472,-15225

8632,-16377

7005,-17118

5294,-17708

3534,-18113

1749,-18388

-63,-18484

-1877,-18382

-3643,-18091

-5091,-17762

-6784,-17128

-8456,-16422

-10009,-15499

-11490,-14429

-12866,-13203

-14073,-11896

-15181,-10461

-16117,-8914

-16910,-7267

-17535,-5574

-17992,-3835

-18333,-2059

-18412,-216

-18339,1593

![[HCTF 2018] Hide and seek(buuctf),Unzip(ctfshow)](https://img-blog.csdnimg.cn/441d810f85894cb2bbc77638858b80ef.png)