AD9371 系列快速入口

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX_CLK生成 (一)

参考资料:

UltraScale Architecture GTH Transceivers User Guide UG576

文章目录

- 前言

- 一、TXUSRCLK 和 TXUSRCLK2

- 二、TXOUTCLK

- 三、25 MHz clock

前言

接 AD9371 官方例程HDL详解之JESD204B TX_CLK生成 (一)

一、TXUSRCLK 和 TXUSRCLK2

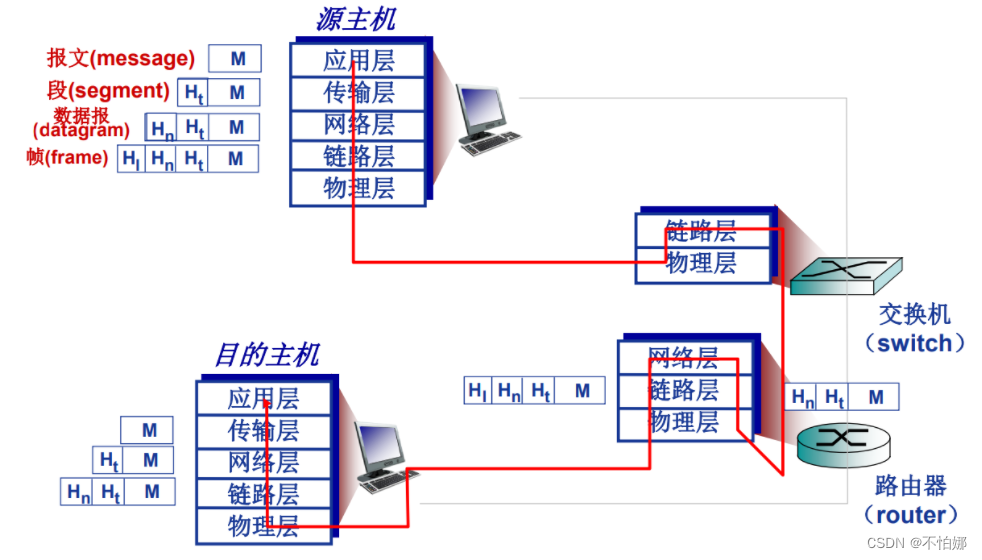

TXUSRCLK2 主要负责 写数据到 TXDATA 端口,TXUSRCLK主要提供 PCS 逻辑时钟。PCS中还有一个时钟域: PMA parallel clock domain (XCLK)。 TX Serial Clock是高速串行时钟。下面重点介绍TXUSRCLK和TXUSRCLK2

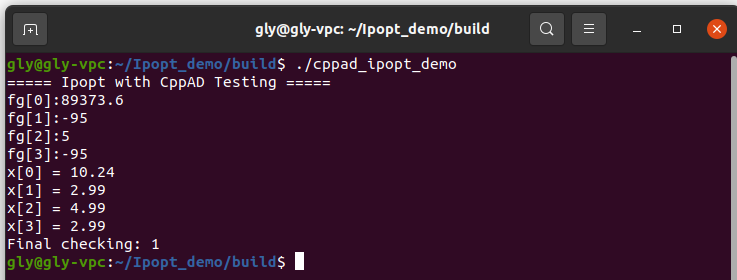

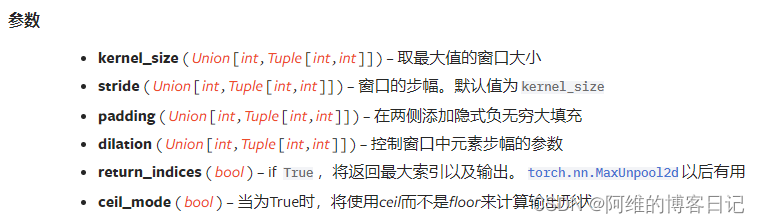

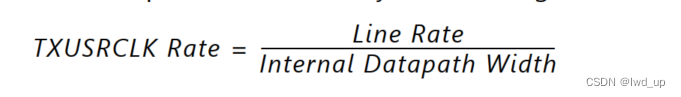

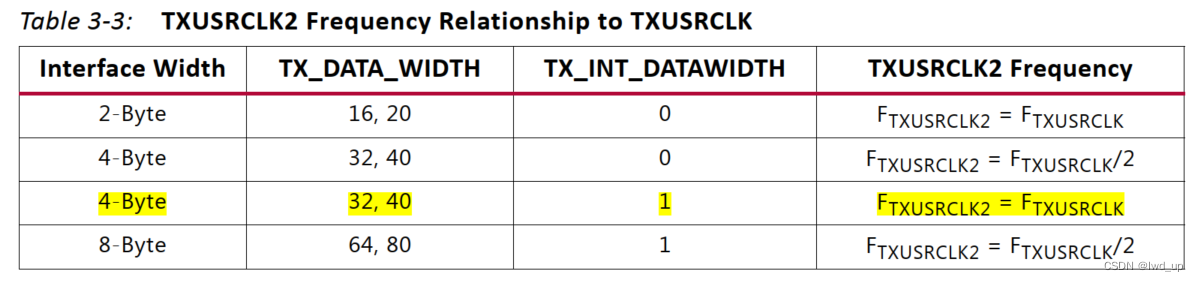

TXUSRCLK 和 TXUSRCLK2 之间的关系和 TX_DATA_WIDTH TX_INT_DATAWIDTH 等参数有关,本例程中,TX8B10BEN=1; TX_DATA_WIDTH =40; TX_INT_DATAWIDTH =1; Internal Data Width =40;

得到TXUSRCLK Rate = Line Rate / 40= link rate;

TXUSRCLK2 = TXUSRCLK= Line Rate / 40= link rate;

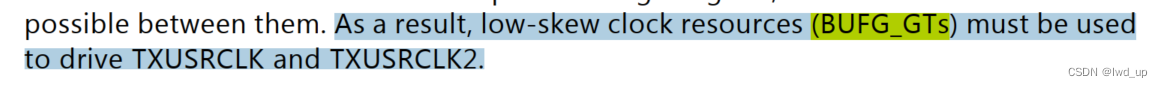

下图中TXOUTCLK 选择的 TXOUTCLKPMA , 本例中 TXOUTCLKPMA =Line Rate / (2(上升沿和下降沿都有效) x 4 x 5)=Line Rate / 40=TXUSRCLK2 = TXUSRCLK ,可以经过BUFG_GT后直接驱动TXUSRCLK2和TXUSRCLK 。

二、TXOUTCLK

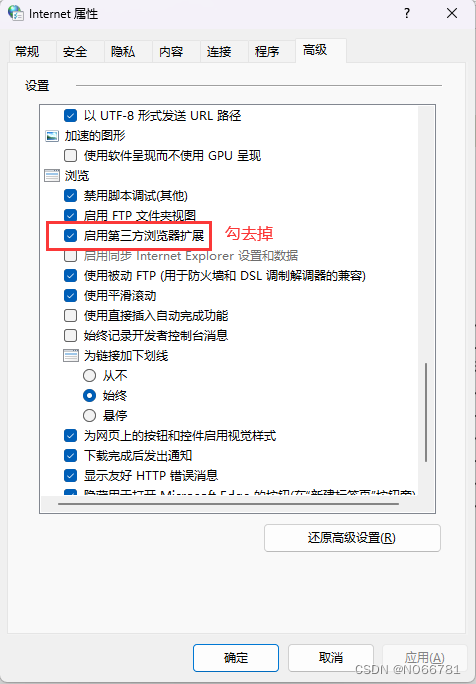

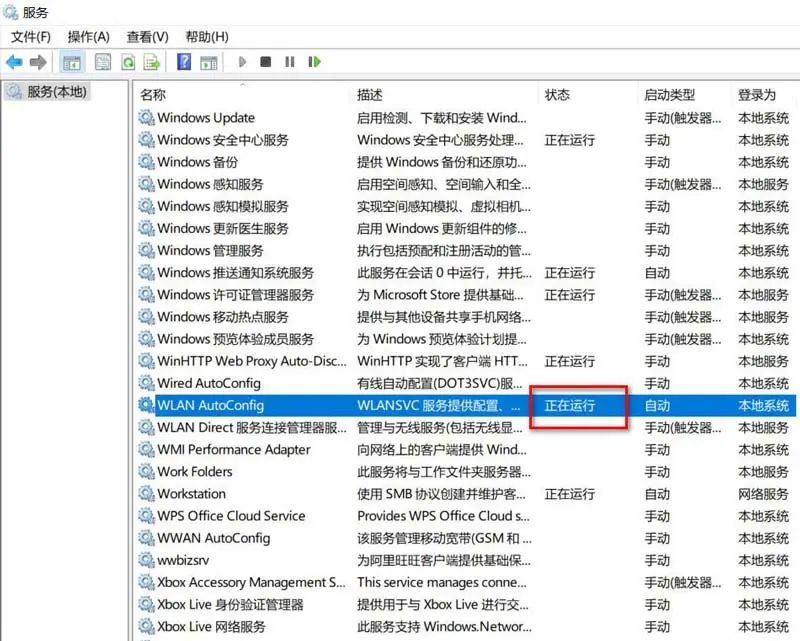

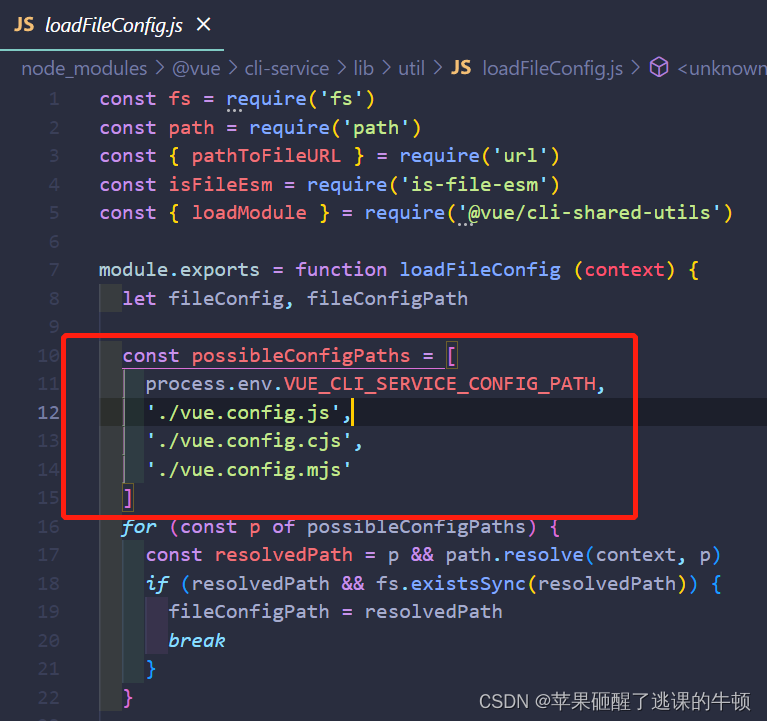

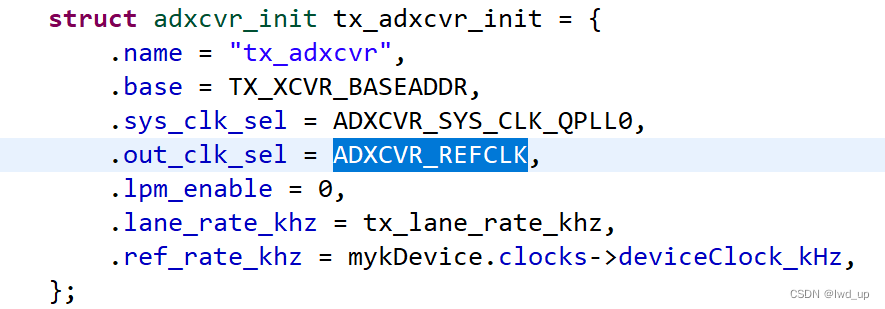

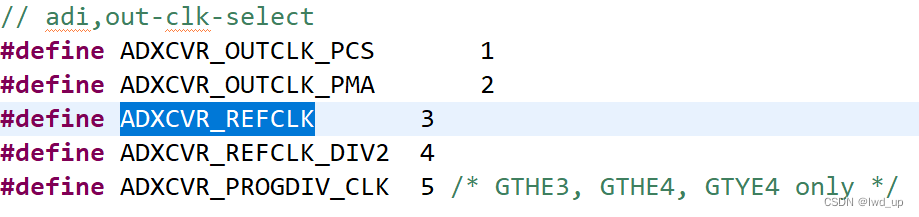

TXOUTCLK 经过 BUFG_GT后 驱动TXUSRCLK2和TXUSRCLK ,TXOUTCLK 可以根据 TXOUTCLKSEL 选择来源,根据下述程序 TXOUTCLK = 3’b011; 选择 TXPLLREFCLK_DIV1

TXPLLREFCLK_DIV1 根据 TXSYSCLKSEL选择时钟源

sys_clk_sel = ADXCVR_SYS_CLK_QPLL0=3;

TXSYSCLKSEL: assign tx_sys_clk_sel_s = (up_tx_sys_clk_sel[1] == 0) ? 2'b00 : {1'b1,~up_tx_sys_clk_sel[0]};

所以最低位取反,TXSYSCLKSEL = 2’b10 ;TXOUTCLK 来自于 QPLL0 的参考时钟

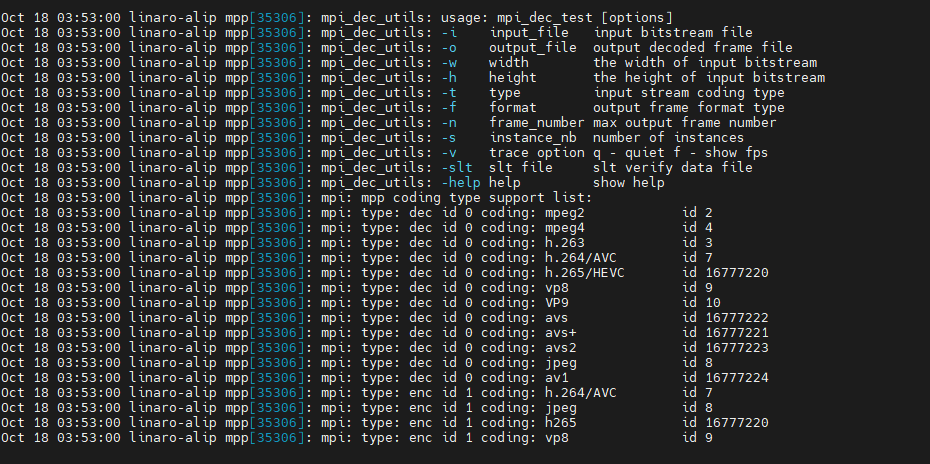

由上节可知 QPLL0、 QPLL1、 CPLL的参考时钟 都是 MGTREFCLK 通过 IBUFDS_GTE4后提供的GTREFCLK0,即 ref_clk1,AD9528 的 OUT1,TXOUTCLK 来自于AD9528 的 OUT1 。

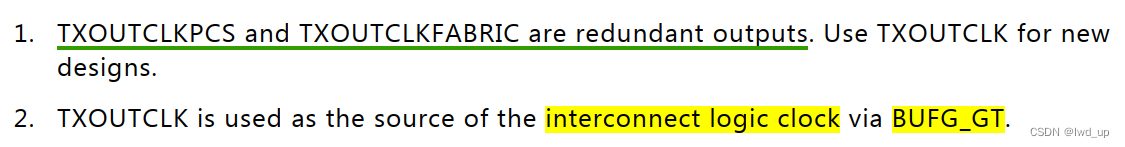

TXOUTCLKPCS 和 TXOUTCLKFABRIC 是冗余输出

TXOUTCLK 通过 BUFG_GT后 可以用作互联逻辑时钟

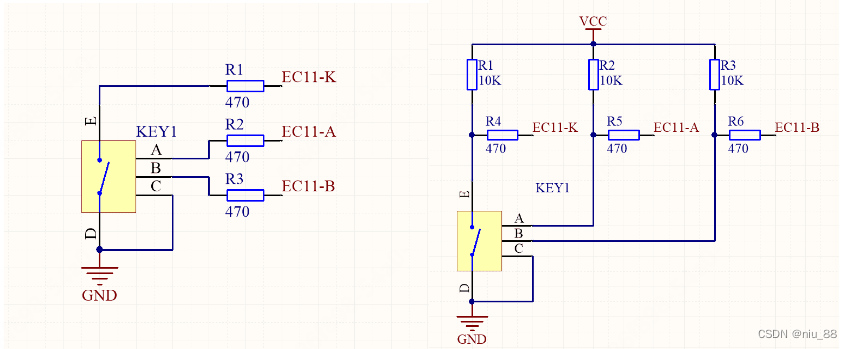

三、25 MHz clock

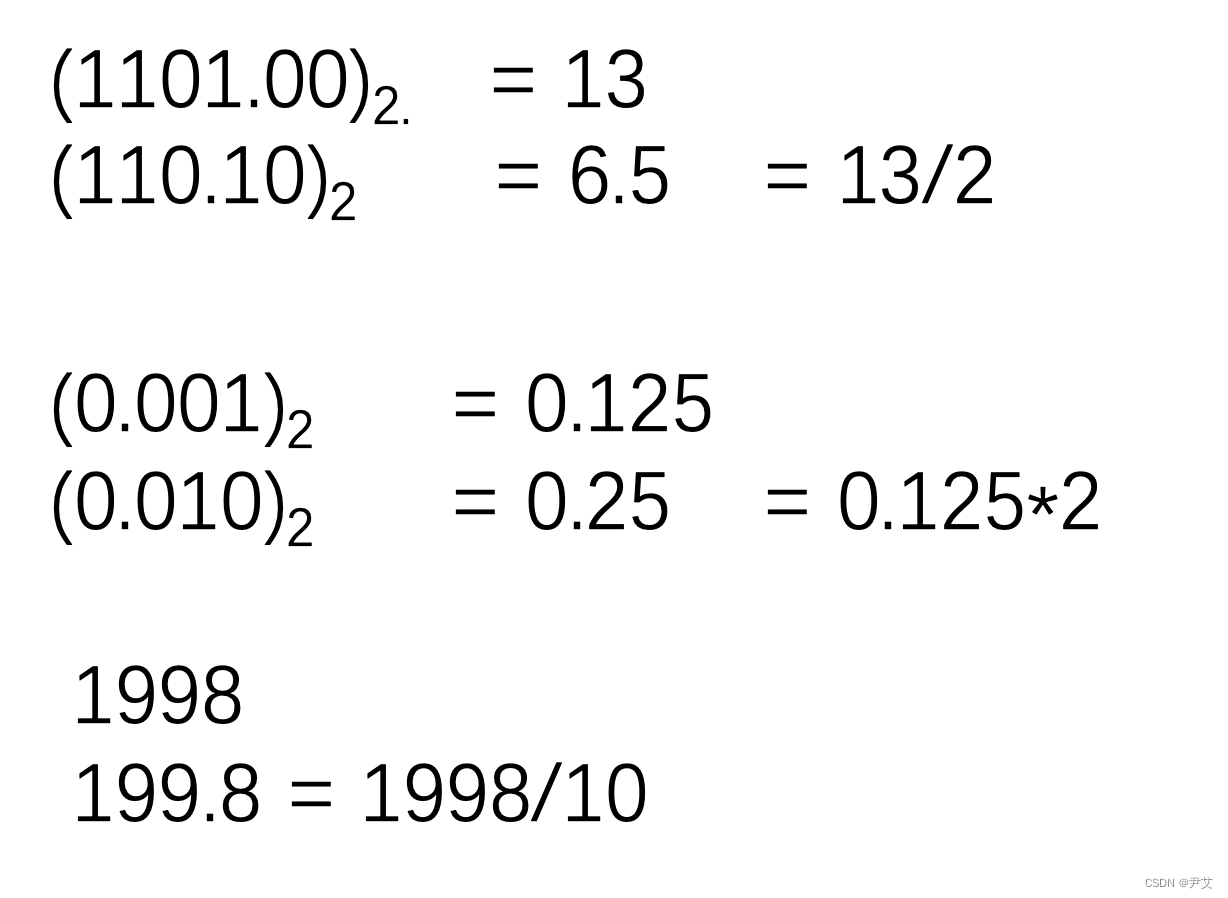

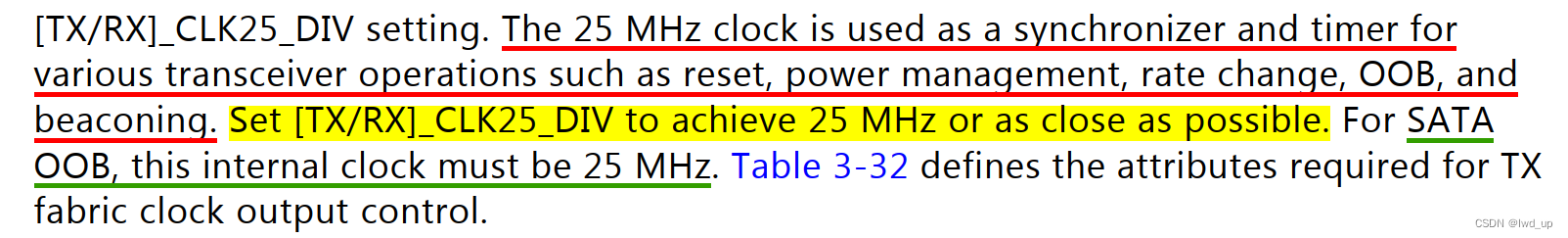

对于同步和定时,需要一个 尽可能接近25MHz的时钟 ,对于SATA OOB,必须是25MHz

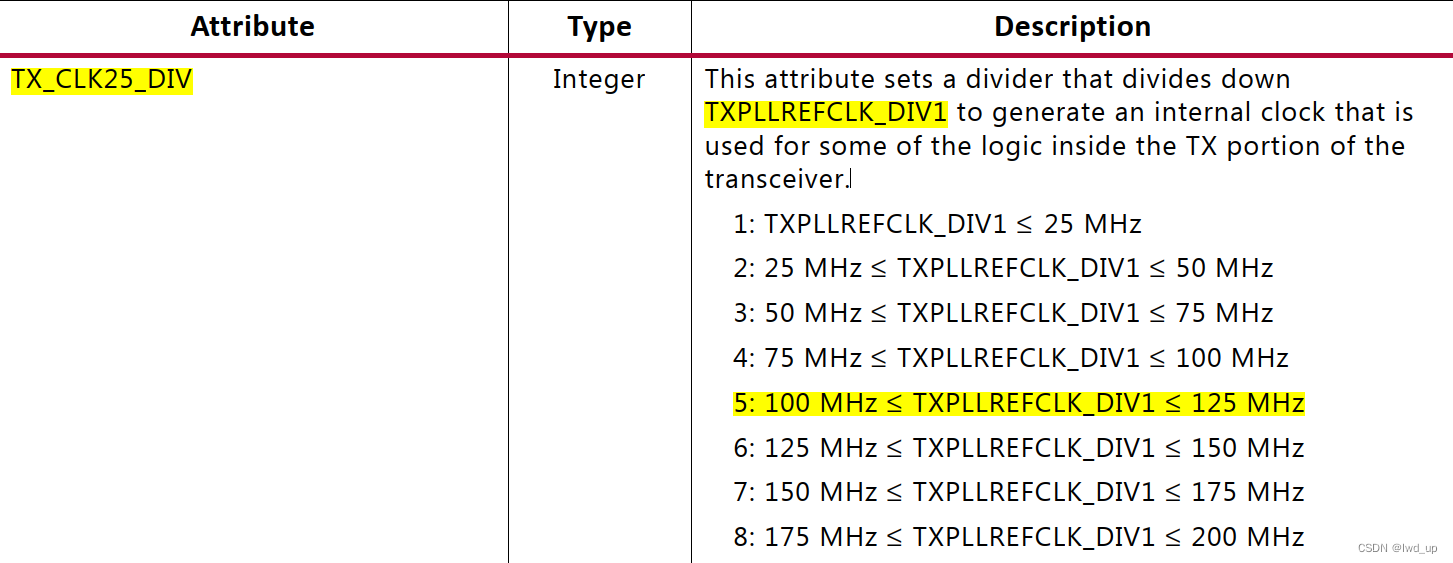

25MHz 根据 TXPLLREFCLK_DIV1 分频产生 ,TXPLLREFCLK_DIV1 是PLL的参考时钟,目前 AD9528 输出的OUT1 是122.88MHz, 大于100 ,小于 125 , 所以 TX_CLK25_DIV = 5 ;同理 RX_CLK25_DIV = 5 。

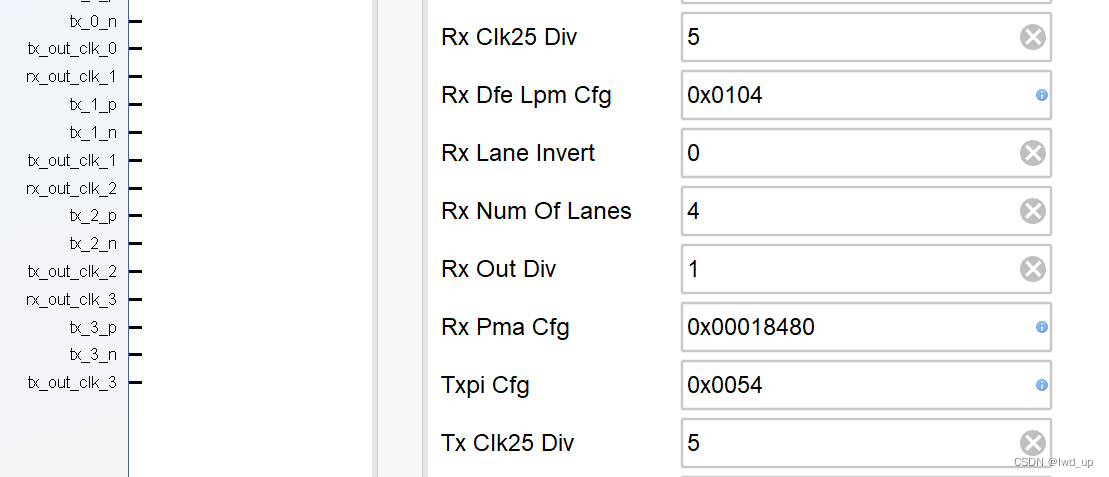

TX CLK25 DIV 和 RX CLK25 DIV 在 util_ad9371_xcvr ip 中 设置为5