目录

一:IP核简介(具体可参考野火FPGA文档)

二: 章节导读

三:PLL电路原理

3.1 PLL基本实现框图

3.2 PLL倍频实现

3.3 PLL分频实现

四: 基于 PLL 的多时钟 LED 驱动设计

4.1 配置 Clocking Wizard 核

4.2 led 闪烁控制

4.2.1 LED闪烁代码设计

4.3 顶层模块代码设计

4.4 仿真测试文件

4.5 仿真结果

4.6 管脚约束文件

4.7 上板验证结果

一:IP核简介(具体可参考野火FPGA文档)

IP ( Intellectual Property)即知识产权, 简言而之,IP 即电 路功能模块。 IP 核在数字电路中常用于比较复杂的功能模块(如 FIFO 、 RAM 、 FIR 滤波 器、 SDRAM 控制器、 PCIE 接口等)设计成参数可修改的模块,让其他用户可以直接调用 这些模块。

IP 核有三种不同的存在形式:

HDL 语言形式---(软核)硬件描述语言;可进行参数调整、复用性强;布局、布线灵活;设计周期短、设计投入少网表形式---(固核)完成了综合的功能块;可预布线特定信号或分配特定的布线资源。版图形式---(硬核)硬核是完成提供设计的最终阶段产品-掩膜(Mask);缺乏灵活性、可移植性差;更易于实现IP核的保护。IP核缺点:

- IP核往往不能跨平台使用

- IP核不透明,看不到内部核心代码

- 定制IP需额外收费

二: 章节导读

在 verilog 设计中,程序的运行往往都是围绕着时钟展开,越是复杂的设计往往会涉及越多不同的时钟。 而对于开发板来说,通常都只设计有一个晶振, 以 ACZ702 开发板的 PL 端为例,就板载了一个 50MHz 的有源晶振。通过开发板 内部逻辑,虽然能够基于该时钟分频倍频,产生不同频率的时钟,但是这些时 钟往往质量较差,并不适合应用。

FPGA 厂商为了解决这个问题,会在器件内部加入专用的时钟电路,也就是 我们常说的锁相环(PLL)。通过该专用时钟电路分频倍频产生的时钟,不仅质 量好,精度也会更高。本章我们将带大家学习锁相环的工作机理,并结合 xilinx 提供的 clocking wizard 软核,通过一个简单的应用来带领大家熟悉锁 相环的基础使用方法。

三:PLL电路原理

锁相环(PLL , Phase-Locked Loop ),是一种反馈控制电路,常常用于利用 外部输入的参考信号控制环路内部振荡信号的频率和相位。锁相环在工作时, 当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,因此得名锁相环。 PLL是最常用的IP核之一,其性能强大,可以对输入到FPGA的时钟信号进行 任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。

锁相环通常由 下图 所示的架构组成:

其中,输入分频、输出分频、反馈分频为三个分频计数器,对时钟分频以满足需求。其余四个模块的功能分别如下:

- 鉴相鉴频器 PFD(Phase Frequency Detector):对输入的基准信号(通常是来自频率稳定的晶振)和反馈回路的信号进行频率的比较,输出一个代表两者相位差异的信号。若相同则输出0 。参考时钟大于对比时钟频率会输出变大的成正比的值,小于就变小的成正比的值。

其中,VCO 输出的时钟经过反馈分频后传回 PFD 这一电路我们称之为 反馈回路 。 PLL 在工作时,压控振荡器输出的时钟信号在经过反馈回路后输入到 PFD 中, PFD 会将其与输入的基准时钟比较,从而得到二者间的频率和相位差。 频率和相位差会以信号的方式输出,驱动 CP 产生电压,经过低通滤波后转换为 直流脉冲电压,作为 VCO 的控制电压,驱动 VCO 改变输出时钟。输出时钟又 会经由反馈回路,输入到 PFD 与基准时钟对比,如此往复,最终输出稳定的满足需求的时钟。

因此,PLL 输出的时钟并不是由输入的基准时钟直接分频倍频得来,而是 基于基准时钟,通过内部的震荡电路生成新的时钟,再经由反馈电路将时钟环 回给 PFD ,通过不断将新产生的时钟与基准时钟作比较,最终输出频率和相位 稳定的时钟。 也正是因为如此,在使用 PLL 时,当基准时钟输入进 PLL 之后,我们并不 能立马得到输出时钟,即使得到也不能立马使用。因为此时的时钟还并不稳定, 需要等待一段时间之后,才能得到精确且稳定的时钟。

3.1 PLL基本实现框图

下图中鉴相鉴频器 PFD(Phase Frequency Detector)是用来比较输入参考信号与反馈信号的频率与相位的。最终它们会趋近于相同,及输出为0。

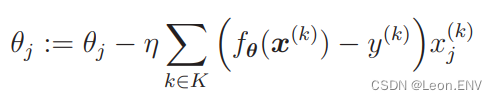

3.2 PLL倍频实现

从下图可以看出倍频多出了一个DIV倍频环节,如果输入信号是50MHz的频率,因为鉴相鉴频器 PFD的两端最终归趋近于相等,则经过DIV之后的频率会变成50MHz。即如果是2倍频,则pll_out会变成100MHz输出。实现倍频输出。

3.3 PLL分频实现

从下图可以看出分频多出了一个DIV分频环节放在输入信号那里,如果输入信号是50MHz的频率,如果分频器DIV是5倍分频,则输入PFD的频率是10M,因为鉴相鉴频器 PFD的两端最终归趋近于相等,则经过反馈回路输出的频率也为10MHz。则pll_out会变成10MHz输出。实现5分频输出。

四: 基于 PLL 的多时钟 LED 驱动设计

本次设计我们将通过 PLL 产生 4 个不同的时钟,这四个时钟分为两个频率,同一频率之间的时钟在相位或占空比上存在差异。通过仿真,对比输出时钟波 形间的关系,验证 PLL 的基础功能。同时,为了验证 PLL 输出的时钟能否稳定 用于其他模块, PLL 输出的时钟还将被用于驱动 LED 。

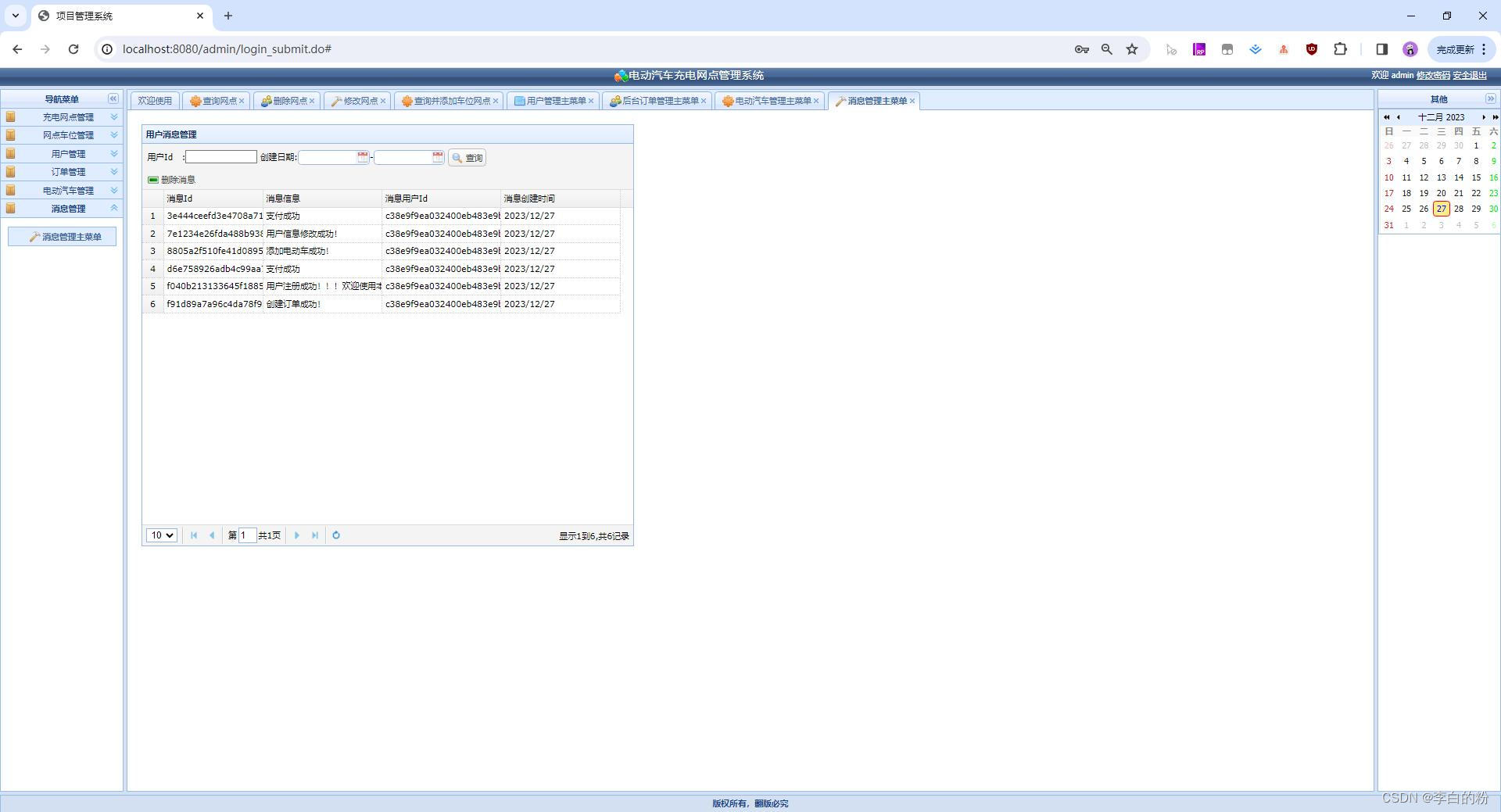

4.1 配置 Clocking Wizard 核

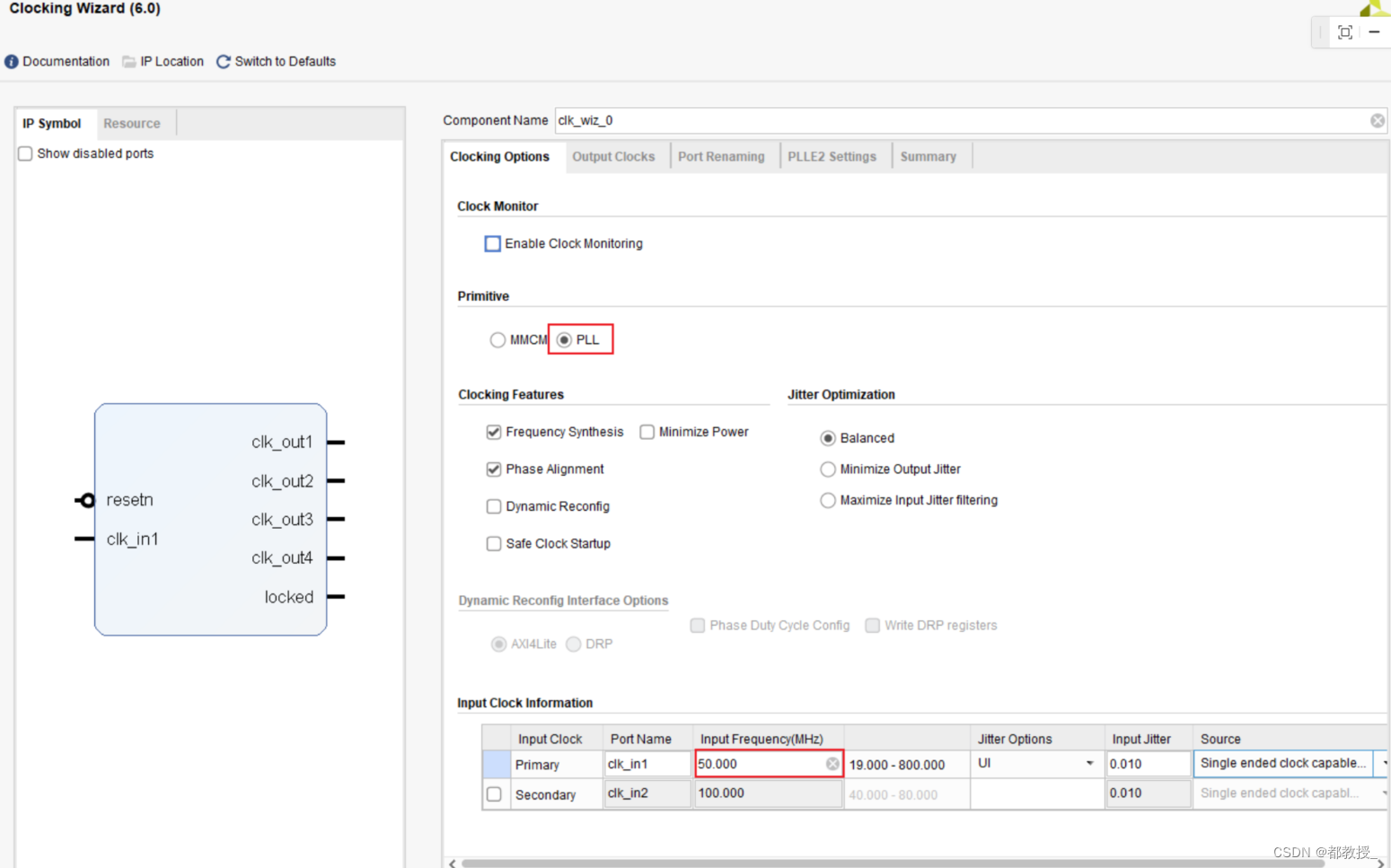

首先,通过 IP Catalog 为设计添加 clocking wizard 核。为了与大多数使用情况一致,本次设计使用的 PLL 结构,输入时钟使用的 50M 板载晶振,输出时钟 频率为常见的 100MHz 和 200MHz ,复位类型为低电平复位。因此, IP 核的时钟 配置界面如下图 所示:

为了观察输出时钟相位和占空比的变化,我们分别对 clk_out2 的相位和clk_out4 的占空比进行了修改,以方便仿真时对照波形。

4.2 led 闪烁控制

基于“视觉暂留”现象,当人眼被中等强度的光刺激以后,人眼看到的图像会短暂停留 0.1~0.4 秒。而如果我们直接使用生成的时钟驱动 led 闪烁,其变 化速率便会远远超过人眼的识别速度,因此,我们需要设计一个分频计数模块, 对输入的时钟分频,控制 LED 的闪烁频率。

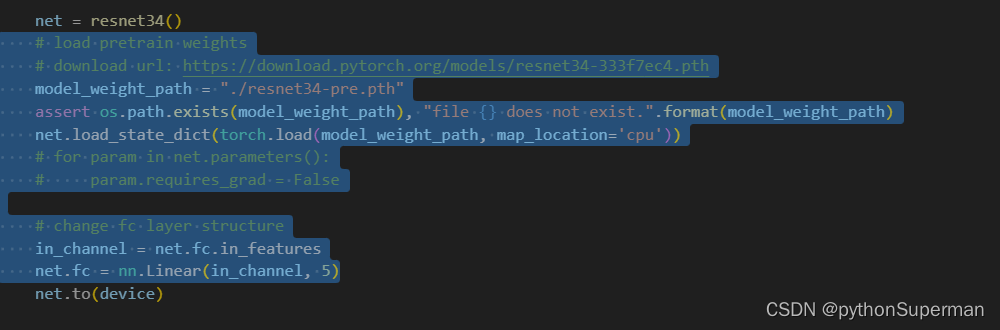

4.2.1 LED闪烁代码设计

module led_ctrl(input clk,input reset_n,output reg led);parameter MCNT = 1000_0000;reg [29:0]cnt;//led翻转计数逻辑always@(posedge clk or negedge reset_n)if(!reset_n)cnt <= 0;else if(cnt >= MCNT-1) cnt <= 0;else cnt <= cnt + 1;always@(posedge clk or negedge reset_n)if(!reset_n)led <= 0;else if(cnt >= MCNT-1) led <= ~led;else led <= led; endmodule

4.3 顶层模块代码设计

module pll_led(input sys_clk,input reset_n, output [3:0]led

);wire locked ;wire clk_100m ;wire clk_100m_s90 ;wire clk_200m ;wire clk_200m_d20 ;led_ctrl #(.MCNT (5000_0000))led_ctrl_inst0(.clk (clk_100m),.reset_n (locked),//当locked信号为高电平时方可使用,其输出的才是稳定的时钟信号。.led (led[0]));led_ctrl #(.MCNT (5000_0000))led_ctrl_inst1(.clk (clk_100m_s90),.reset_n (locked),.led (led[1]));led_ctrl #(.MCNT (5000_0000))led_ctrl_inst2(.clk (clk_200m),.reset_n (locked),.led (led[2]));led_ctrl #(.MCNT (5000_0000))led_ctrl_inst3(.clk (clk_200m_d20),.reset_n (locked),.led (led[3]));clk_wiz_0 clk_wiz_0_inst(// Clock out ports.clk_100m(clk_100m), // output clk_100m.clk_100m_s90(clk_100m_s90), // output clk_100m_s90.clk_200m(clk_200m), // output clk_200m.clk_200m_d20(clk_200m_d20), // output clk_200m_d20// Status and control signals.resetn(reset_n), // input resetn.locked(locked), // output locked// Clock in ports.sys_clk(sys_clk)); // input sys_clk

endmodule

4.4 仿真测试文件

`timescale 1ns / 1ps

module pll_led_tb();reg sys_clk ;

reg reset_n ;

wire clk_100m ;

wire clk_100m_s90 ;

wire clk_200m ;

wire clk_200m_d20 ;

wire [3:0]led ;pll_led pll_led(.sys_clk (sys_clk) ,.reset_n (reset_n) ,.clk_100m (clk_100m) ,.clk_100m_s90(clk_100m_s90) ,.clk_200m (clk_200m) ,.clk_200m_d20(clk_200m_d20) ,.led (led)

);//重定义,缩短仿真时间defparam pll_led.led_ctrl_inst0.MCNT = 26'd500;defparam pll_led.led_ctrl_inst1.MCNT = 26'd500;defparam pll_led.led_ctrl_inst2.MCNT = 26'd500; defparam pll_led.led_ctrl_inst3.MCNT = 26'd500;initial sys_clk = 1'b1;always #10 sys_clk = ~sys_clk;initialbeginreset_n = 0;#201;reset_n = 1;#20000; $stop;endendmodule

4.5 仿真结果

4.6 管脚约束文件

set_property IOSTANDARD LVCMOS33 [get_ports reset_n]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property PACKAGE_PIN F20 [get_ports reset_n]

set_property PACKAGE_PIN G17 [get_ports {led[0]}]

set_property PACKAGE_PIN G19 [get_ports {led[1]}]

set_property PACKAGE_PIN G18 [get_ports {led[3]}]

set_property PACKAGE_PIN G20 [get_ports {led[2]}]

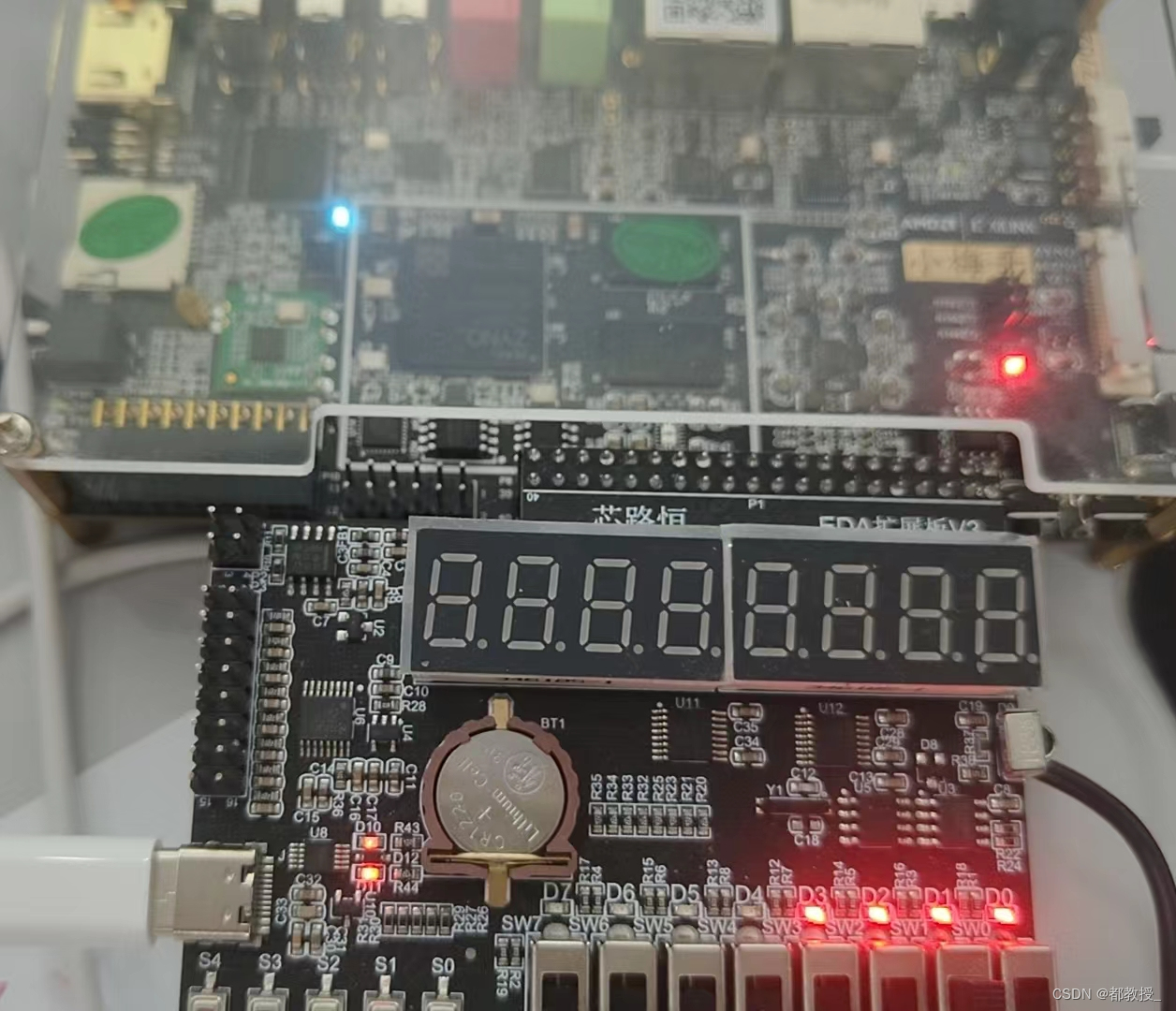

4.7 上板验证结果

至此PLL的IP核调用实验完美成功。