在数字IC后端设计实现过程中,我们一直强调做时钟树综合要把clock skew做到最小。原因是clock skew的存在对整体设计的timing是不利的。

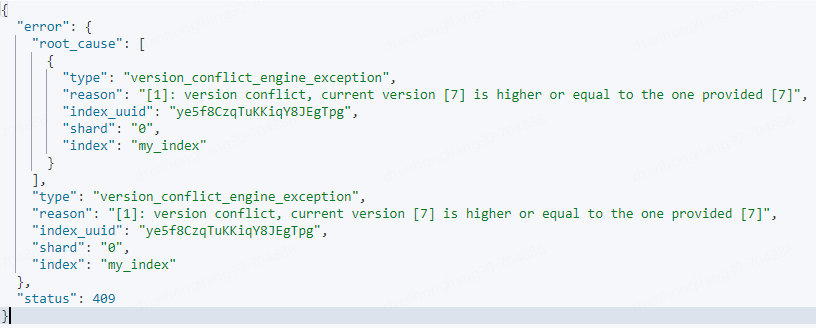

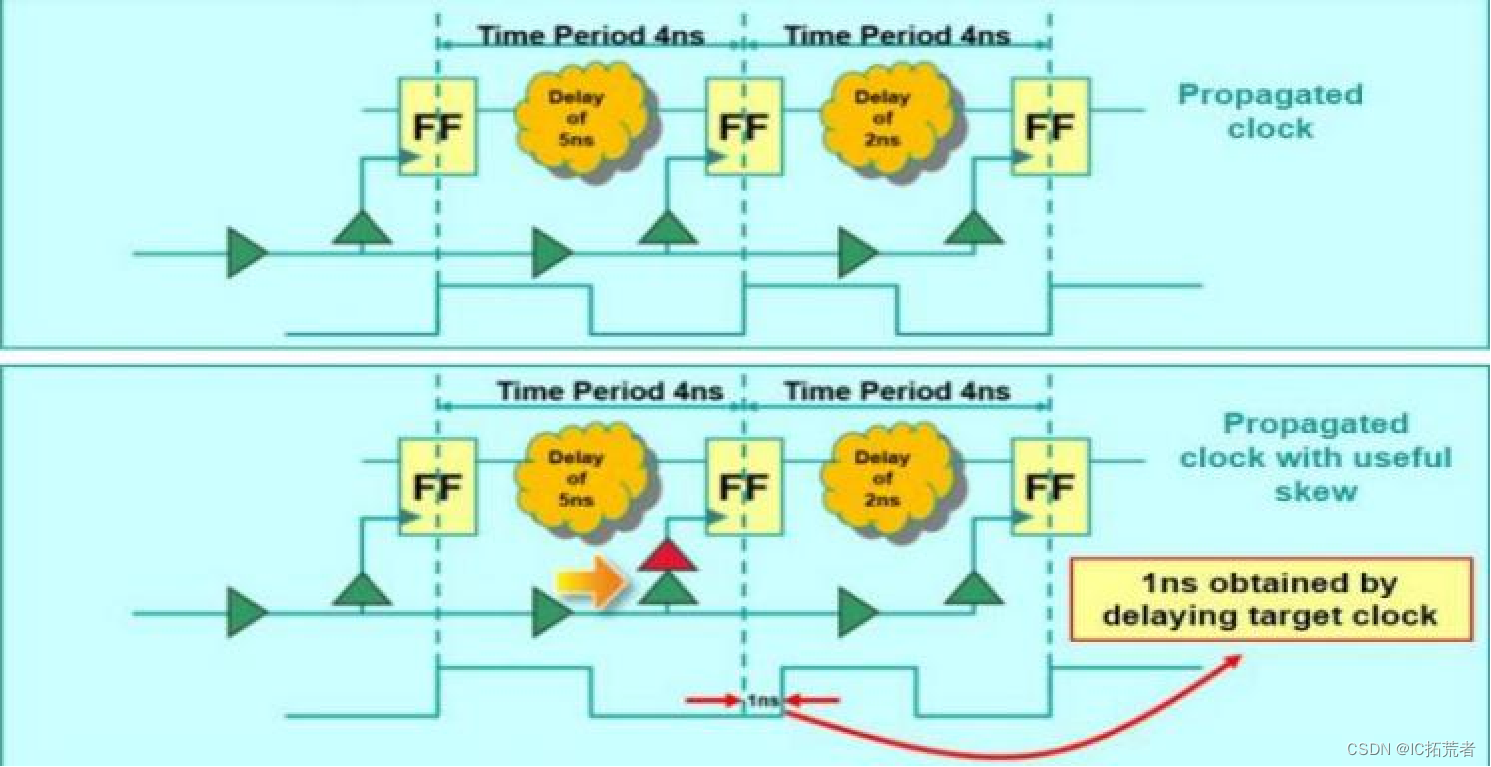

但是具体到某些timing path,可能它的local clock skew对timing是有帮助的,比如如下图所示。

第一级FF到第二级FF的setup原来存在-1ns的violation。经过借用后一级的timing margin把第二个FF的tree做长1ns后这条timing path的setup slack变成0ns,即meet了。而且我们发现第二级FF到第三级FF的setup slack虽然从原来的2ns slack变成1ns的slack,但依然还是正的slack。

所以,这个人为引入的clock skew对我们的setup是有利的,所以把这个技术称作usefu skew。

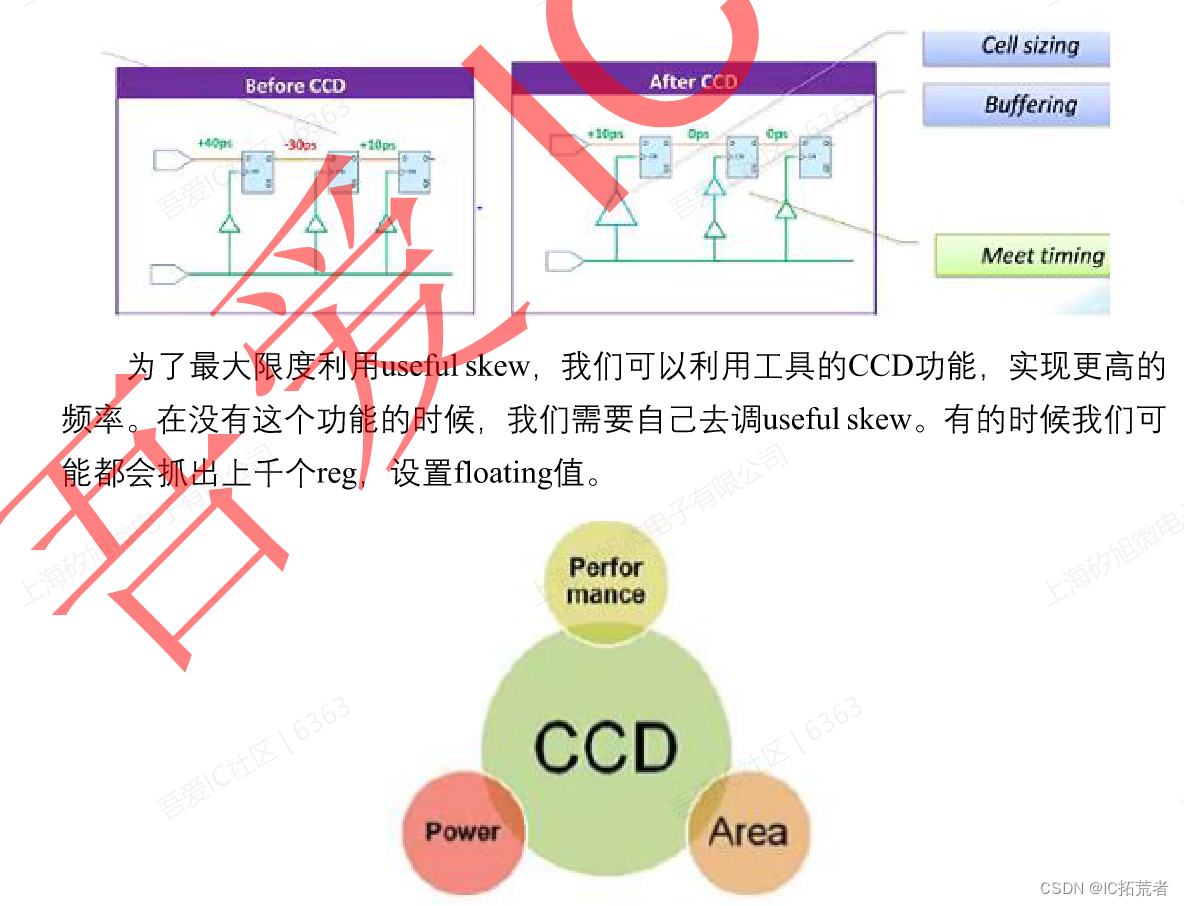

所以EDA工具无论是Synopsys还是Cadence的,在时序优化阶段都支持clock和data的同步优化功能。

在没有这个功能时,我们需要一个个去分析到底哪些点的sink需要做长做短。现在我们可以直接通过模式和选项的设置让工具自己帮助我们来利用好useful skew。

ICC2:

set_app_options -name clock_opt.flow.enable_ccd_route_clock -value true

set_app_options -name clock_opt.flow.enable_ccd_route_clock_eco -value true

设置useful skew可利用区间

set_app_options -list “ccd.max_postpone 0.06”

set_app_options -list “ccd.max_prepone 0.06”

限制CCD应用在boundary

set ccd.optimize_boundary_timing false

set ccd.optimize_boundary_timing_upstream false

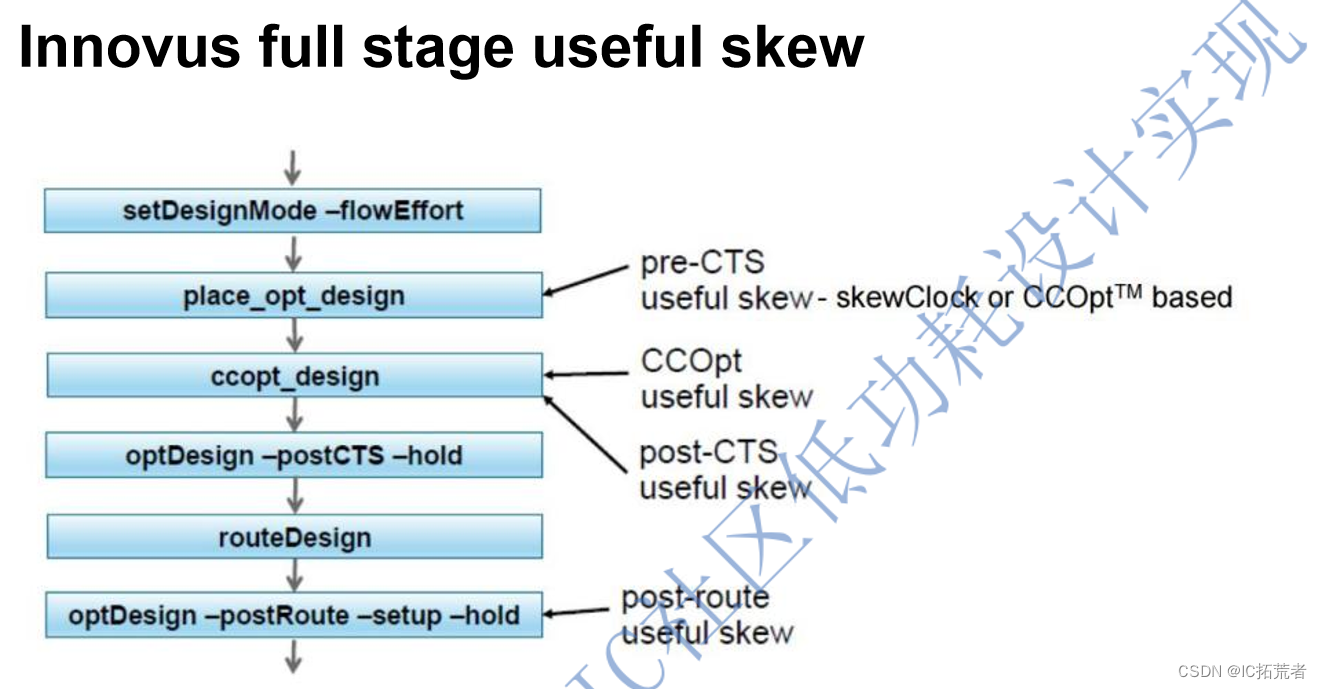

Innovus:

在数字IC后端实现innovus PR过程中一般建议全流程打开useful skew。对于高性能 ARM CPU设计,建议结合early clock flow来使用,效果最佳。

setOptMode -usefulSkew true

setOptMode -usefulSkewPreCTS true

setOptMode -usefulSkewCCOpt extreme

setOptMode -usefulSkewPostRoute true

setUsefulSkewMode -maxAllowedDelay 0.06

setOptMode -usefulSkew是主开关,它控制optDesign在整个Flow的useful skew。如果设置为false,则无论其他控制开关的设置如何,flow中的任何位置都不会利用Useful skew。该选择在工具里面默认是true。

setDesignMode -flowEffort是一个design level的控制开关,用于根据设计目标来调节优化的力度。

新的setOptMode -usefulSkewCCOpt控制命令替换了早期的参数-usefulSkewCTS和-usefulSkewPostCTS,以及命令set_ccopt_effort。

innovus也支持对某些特殊的sink点施加特殊的约束,告知工具不使用useful skew技术。

setOptMode -skewClockPreserveLatencyTermList $special_clk_pin_name

setOptMode -usefulSkewPreCTSPreserveLatencyTermList $special_clk_pin_name

set_ccopt_property schedule off -pin $special_clk_pin_name

![LeetCode[105] 从前序与中序遍历序列构造二叉树](https://img-blog.csdnimg.cn/img_convert/7734f2d365035a4069006c67e7c1efb9.jpeg)

![[计算机提升] 创建FTP共享](https://img-blog.csdnimg.cn/direct/9232e63d960744b0b1bc9c87953c0f5f.png)