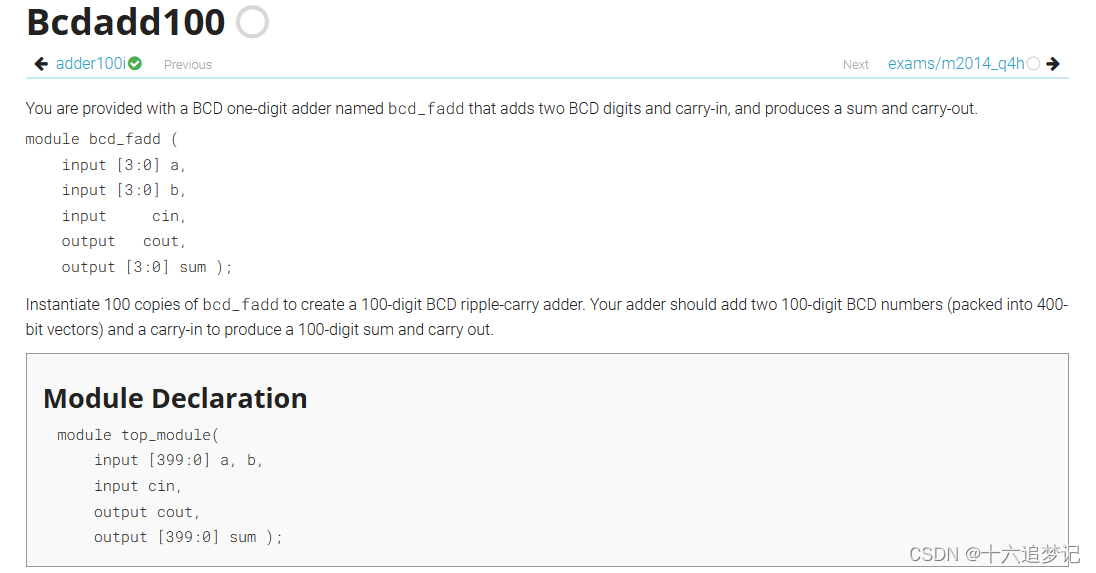

题目:

You are provided with a BCD one-digit adder named bcd_fadd that adds two BCD digits and carry-in, and produces a sum and carry-out.

解题:

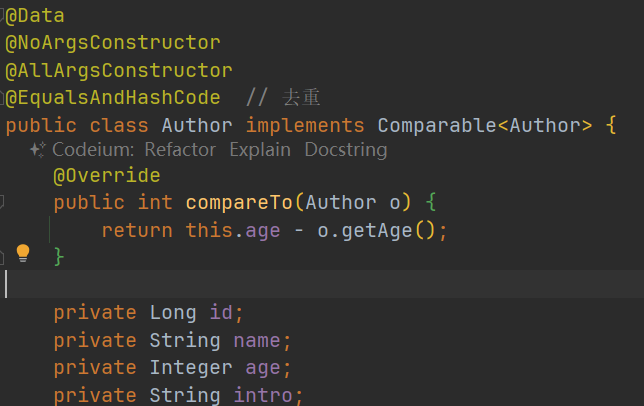

module top_module( input [399:0] a, b,input cin,output cout,output [399:0] sum );reg [99:0] cined;bcd_fadd u0(a[3:0],b[3:0],cin,cined[0],sum[3:0]);genvar i ;generatefor(i=1;i<=99;i=i+1)begin:bcd_faddbcd_fadd u2(a[i*4+3:i*4],b[i*4+3:i*4],cined[i-1],cined[i],sum[i*4+3:i*4]);endendgenerateassign cout = cined[99];endmodule

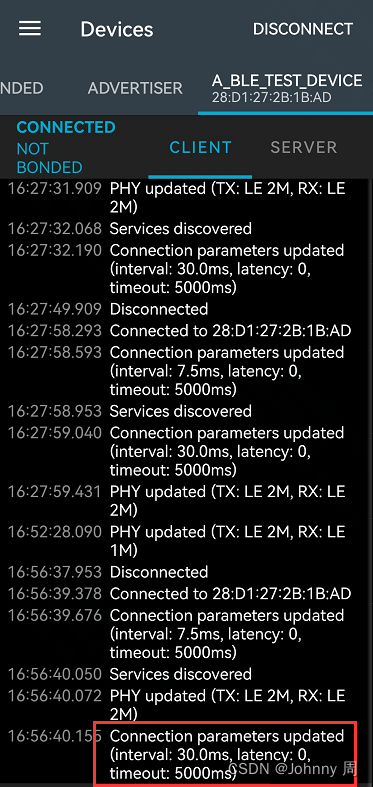

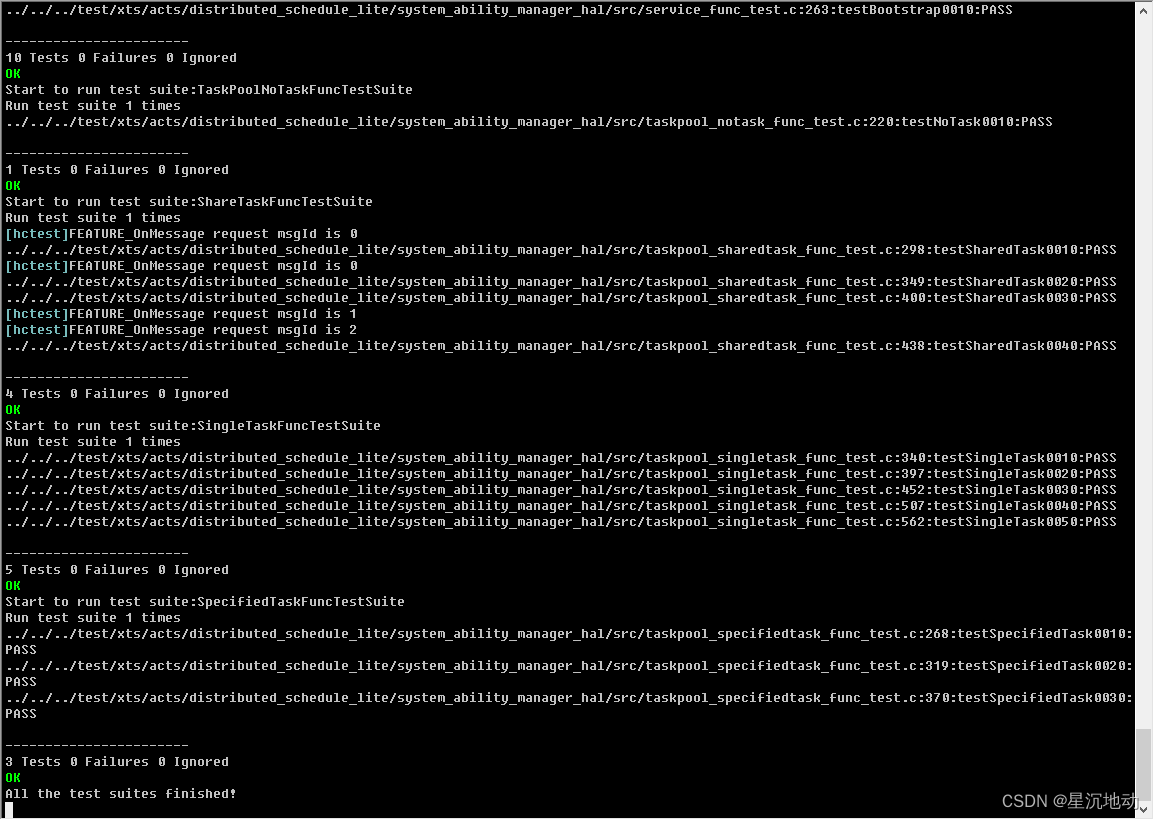

结果正确:

注意点:

在 Verilog 中,generate 是一个关键字,用于在编译时生成硬件结构(如模块实例、端口连接等)或产生代码块。generate 语句提供了一种在编译时根据参数或条件生成代码的机制,从而实现灵活的硬件描述。

使用 generate 语句可以在一个模块中根据条件生成不同的硬件实例。这是一种方便的方式来处理可配置和可重用的模块结构。常见的使用场景包括,但不限于:

根据参数生成多个实例:可以根据参数的值来生成不同的硬件实例,从而减少代码冗余。

循环生成: 可以使用 generate 和 for 循环语句生成多个实例或者生成重复的结构。

根据条件生成: 可以使用 if 语句来根据条件生成不同的硬件结构。

下面是一个使用 generate 语句生成多个模块实例的示例:

module Example #(parameter N = 4) (input [N-1:0] a,output [N-1:0] b

);generategenvar i;for (i = 0; i < N; i = i + 1) begin// 根据循环生成多个实例ExampleInstance #(.ID(i)) inst (.a(a[i]),.b(b[i]));endendgenerateendmodule

在上面的示例中,定义了一个模块 Example,该模块具有参数 N 来指定生成实例的数量。在 generate 语句中,我们使用了 for 循环来生成 N 个 ExampleInstance 模块实例,每个实例具有不同的 ID。

需要注意的是,generate 语句不会在运行时执行,而是在编译时生成硬件结构。因此,在使用 generate 语句时,要确保生成的代码在编译期间是合法的,并遵循 Verilog 的语法规则。

通过使用 generate 语句,可以根据条件或参数生成灵活的硬件结构,从而在硬件描述语言中实现更可配置和可重用的设计。