1.NAND FLASH的简介

NAND FLASH 的概念是由东芝公司在 1989 年率先提出,它内部采用非线性宏单元模式,为固态大容量内存的实现提供了廉价有效的解决方案。 NAND FLASH 存储器具有容量较大,改写速度快等优点,适用于大量数据的存储,在业界得到了广泛应用,如: SD 卡、 TF 卡、 U盘等,一般都是采用 NAND FLASH 作为存储的。 关于 NAND FLASH 的基础知识,请大家自行百度学习。接下来,我们介绍 NAND FLASH 的一些重要知识。

2.NAND FLASH 信号线

因为 NAND FLASH 地址/数据是共用数据线的,所以必须有 CLE/ALE 信号,告诉 NAND

因为 NAND FLASH 地址/数据是共用数据线的,所以必须有 CLE/ALE 信号,告诉 NAND

FLASH,发送的数据是命令还是地址。

3.存储单元

NAND FLASH 存储单元介绍,我们以 MT29F4G08( x8,8 位数据)为例进行介绍, MT29F4G08 的存储单元组织结构如图所示

由图可知: MT29F4G08 由 2 个 plane 组成,每个 plane 有 2048 个 block,每个 block 由 64

由图可知: MT29F4G08 由 2 个 plane 组成,每个 plane 有 2048 个 block,每个 block 由 64

个 page 组成,每个 page 有 2K+64 字节( 2112 字节)的存储容量。所以, MT29F4G08 的总容

量为: 2204864*( 2K+64) = 553648128 字节( 512MB)。其中, plane、 block、 page 等的个数,根据 NAND FLASH 型号的不同,会有所区别。

4.NAND FLASH 的地址

NAND FLASH 的地址分为三类:块地址( Block Address)、页地址( Page Address)和列地

址( Column Address)。以 MT29F4G08 为例,这三个地址,通过 5 个周期发送,如图所示

表中, CA0~CA11 为列地址( Column Address),用于在一个 Page 内部寻址, MT29F4G08

的一个 Page 大小为 2112 字节,需要 12 个地址线寻址; PA0~PA5 为页地址( Page Address),用于在一个 Block 内部寻址, MT29F4G08 一个 Block 大小为 64 个 Page,需要 6 个地址线寻址;

BA6~BA17 为块地址( Block Address),用于块寻址, MT29F4G08 总共有 4096 个 Block,需要

12 根地址线寻址。

整个寻址过程,分 5 次发送( 5 个周期),首先发送列地址,在发送页地址和块地址。这里提醒一下:块地址和页地址,其实是可以写在一起的,由一个参数传递即可,所以表中的 BA并不是由 BA0 开始的,大家可以理解为这个地址( PA+BA)为整个 NAND FLASH 的 Page 地址。在完成寻址以后,数据线 I/O0~ I/O7 来传输数据了。

5.NAND FLASH的控制命令

例如:读页命令

READ PAGE

该指令用于读取 NAND 的一个 Page(包括 spare 区数据,但不能跨页读),该指令时序如图所示:

由图可知, READ PAGE 的命令分两次发送,首先发送 00H 命令,然后发送 5 次地址( Block&Page&Column 地址),指定读取的地址,随后发送 30H 命令,在等待 RDY 后,即可读取 PAGE 里面的数据。注意:不能跨页读,所以最多一次读取一个 PAGE 的数据(包括 spare区)。

由图可知, READ PAGE 的命令分两次发送,首先发送 00H 命令,然后发送 5 次地址( Block&Page&Column 地址),指定读取的地址,随后发送 30H 命令,在等待 RDY 后,即可读取 PAGE 里面的数据。注意:不能跨页读,所以最多一次读取一个 PAGE 的数据(包括 spare区)。

6.FMC 接口的 NAND FLASH 控制寄存器

⚫ 独立 NAND FLASH 存储区域,可独立配置

⚫ 支持 8 位和 16 位 NAND FLASH

⚫ 支持硬件 ECC 计算(汉明码)

⚫ 支持 NAND FLASH 预等待功能

NAND FLASH 的控制寄存器: FMC_PCR,该寄存器各位描述如图所示:

该寄存器只有部分位有效,且都需要进行配置:

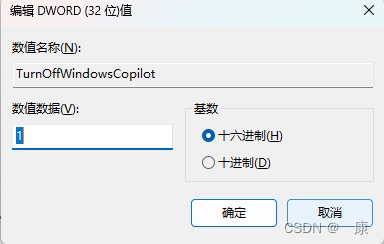

PWAITEN:该位用于设置等待特性: 0,禁止; 1,使能。这里我们设置为 0,禁止使用控制器自带的等待特性,因为如果使能的话,将导致 RGB 屏抖动( STM32 硬件 bug)。

PBKEN:该位用于使能存储区域: 0,禁止; 1,使能。我们要正常使用某个存储区域,必须设置该位为 1,所以,这个位要设置为 1。

PWID:这两个位,用于设置数据总线宽度: 00, 8 位宽度; 01, 16 位宽度。我们使用的MT29F4G08 为 8 位宽度,所以这里应该设置为: 00。

ECCEN:该位用于使能 STM32 的硬件 ECC 计算逻辑: 0,禁止/复位 ECC; 1,使能 ECC计算;每次读写数据前, 应该设置该位为 1,在数据读写完毕,读取完 ECC 值之后,设置该位为 0,复位 ECC,以便下一次 ECC 计算。

TCLR:这四个位用于设置 CLE 到 RE 的延迟: 0000~1111,表示 1~16 个 fmc_ker_ck 周期。对应 NAND FLASH 数据手册的 tCLR 时间参数: t_clr=(TCLR+SET+2)*Tfmc_ker_ck。 TCLR 就是本寄存器的设置值, SET 对应 MEMSET 的值(我只用到 MEMSET), Tfmc_ker_ck 对应fmc_ker_ck 的周期。 MT29F4G08 的 tCLR 时间最少为 10ns,以 220M 的 fmc_ker_ck 频率计算,一个 fmc_ker_ck=4.5ns(下同),我们设置 TCLR=5,则 t_clr 至少为 7 个 fmc_ker_ck 即 31.5ns。

TAR:这四个位用于设置 ALE 到 RE 的延迟: 0000~1111,表示 1~16 个 HCLK 周期。对应NAND FLASH 数据手册的 tAR 时间参数,这里设置的 t_ar=(TAR+SET+2)* Tfmc_ker_ck。 TAR就是本寄存器的设置值, SET 对应 MEMSET 的值(我只用到 MEMSET), Tfmc_ker_ck 对应fmc_ker_ck 的周期。 MT29F4G08 的 tAR 时间最少为 10ns,我们设置 TAR=5,则 t_ar 至少为 7个 fmc_ker_ck 即 31.5ns。

ECCCPS:这三个位用于设置 ECC 的页大小: 000, 256 字节; 001, 512 字节; 010, 1024字节; 011, 2048 字节;100, 4096 字节; 101, 8192 字节。我们需要以 512 字节为单位进行ECC 计算,所以 ECCCPS 设置为: 001 即可。

NAND FLASH 的空间时序寄存器: FMC_PMEM,该寄存器各位描述如图所示:

该寄存器用于控制 NAND FLASH 的访问时序,非常重要。我们先来了解下 NAND FLASH控制器的通用存储器访问波形,如图所示:

由图可知, MEMxSET+MEMxHOLD 控制 NWE/NOE 的高电平时间, MEMxWAIT 控制NWE/NOE 的低电平时间, MEMxHIZ 控制写入时数据线高阻态时间。接下来我们分别介绍这几个参数:

MEMSET: 这八个位定义使能命令( NWE/NOE)前,地址建立所需要的 fmc_ker_ck 时钟周期数,表示 NWE/NOE 的高电平时间, 0000 0000~1111 1110 表示 1~255 个 fmc_ker_ck 周期。MT29F4G08 的 tREH/tWH 最少为 10ns,设置 MEMSET=3,即 4 个 fmc_ker_ck 周期,约 18ns。另外, MEMHOLD,也可以用于控制 NWE/NOE 的高电平时间,在连续访问的时候, MEMHOLD

和 MEMSET 共同构成 NWE/NOE 的高电平脉宽时间。

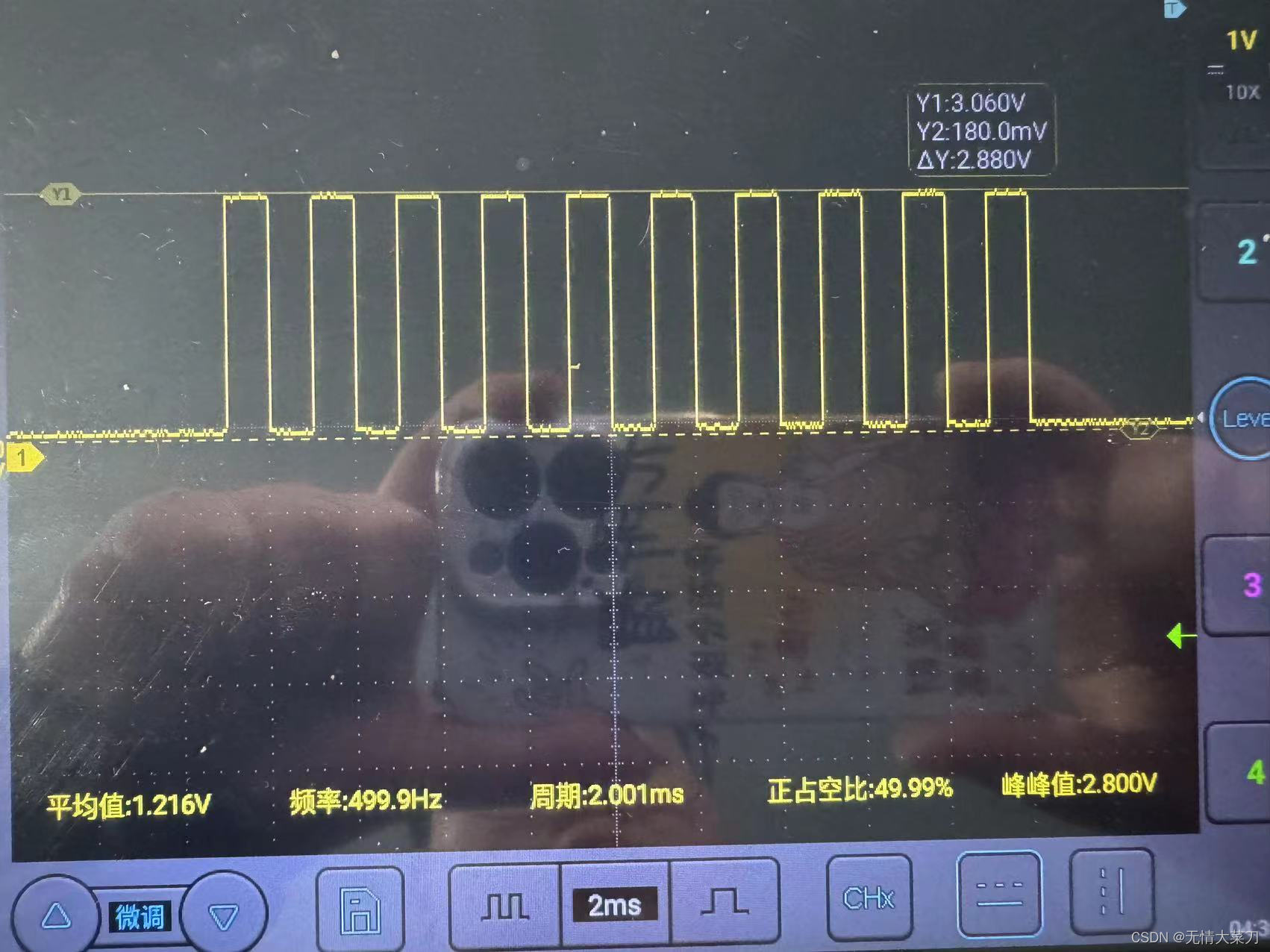

MEMWAIT:这八个位用于设置使能命令( NWE/NOE)所需的最小 fmc_ker_ck 时钟周期数(使能 NWAIT 将使这个时间延长),实际上就是 NWE/NOE 的低电平时间, 0000 0000~1111,1110 表示 1~255 个 HCLK 周期。 MT29F4G08 的 tRP/tWP 最少为 10ns,我们设置 MEMWAIT =5,即 6 个 fmc_ker_ck 周期,约 27ns。这里需要设置时间比较长一点,否则可能访问不正常。

MEMHOLD:这八个位用于设置禁止使能命令( NWE/NOE)后,保持地址(和写访问数据)的 fmc_ker_ck 时钟周期数,也可以用于设置一个读写周期内的 NWE/NOE 高电平时间, 00000000~1111 1110 表示 0~254 个 HCLK 周期。我们设置MEMHOLD=2,表示 2 个 fmc_ker_ck 周期,加上前面的 MEMSET,所以 NEW/NOE 高电平时间为 6 个 HCLK,即 27ns 左右。

MEMHIZ:这八个位定义通用存储空间开始执行写访问之后,数据总线保持高阻态所持续的 fmc_ker_ck 时钟周期数。该参数仅对写入事务有效, 0000~1111 1110 表示 0~254 个 fmc_ker_ck周期。我们设置 MEMHIZ=3,表示 3 个 fmc_ker_ck 周期, 即 13.5ns 左右。

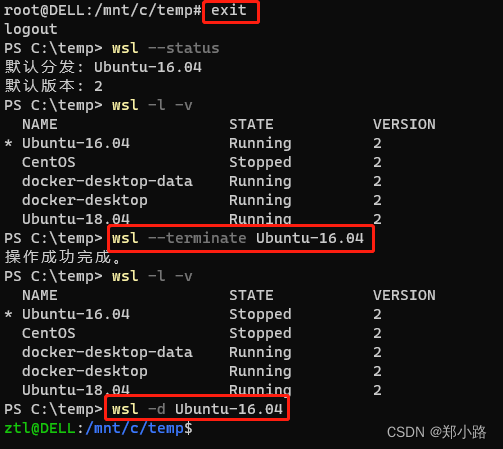

7.NAND FLASH和STM32芯片的连接图

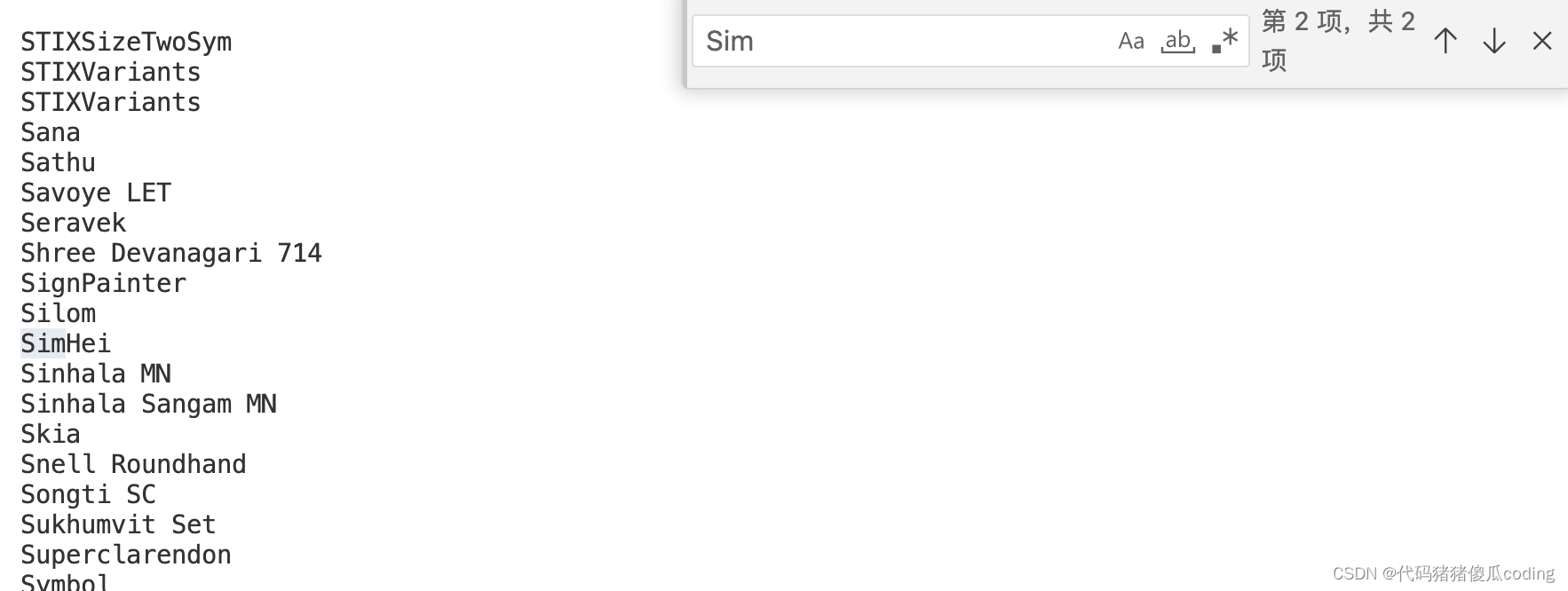

8.STM32CubeMx配置Nand Flash

(1).选择FMC项

Data/Address:由于Nand Flash是地址和数据共线,由于MT29F4G08芯片是8根数据线,所以这里设置为8bits。

Ready or busy:等待特性使能/失能,对应FMC_PCR寄存器中的PWAITEN位,用于设置等待特性: 0,禁止; 1,使能。这里我们设置为 0,禁止使用控制器自带的等待特性,因为如果使能的话,将导致 RGB 屏抖动( STM32 硬件 bug)。

ECC computation:ECC计算逻辑使能/失能,对应FMC_PCR寄存器中的ECCEN位,0:禁止/复位ECC,1:使能ECC计算

ECC page size:ECC页大小,对应FMC_PCR寄存器中的ECCCPS,这三个位用于设置ECC的页大小,256字节,512字节,1024字节,2048字节,4096字节,8192字节。

CLE low to RE low delay in HCLK cycles:CLE到RE的延迟,对应FMC_PCR寄存器中的TCLR,这四个位用于设置 CLE 到 RE 的延迟: 0000~1111,表示 1~16 个 fmc_ker_ck 周期。对应 NAND FLASH 数据手册的 tCLR 时间参数: t_clr=(TCLR+SET+2)*Tfmc_ker_ck。 TCLR 就是本寄存器的设置值, SET 对应 MEMSET 的值(我只用到 MEMSET), Tfmc_ker_ck 对应fmc_ker_ck 的周期。 MT29F4G08 的 tCLR 时间最少为 10ns,以 220M 的 fmc_ker_ck 频率计算,

一个 fmc_ker_ck=4.5ns(下同),我们设置 TCLR=5,则 t_clr 至少为 7 个 fmc_ker_ck 即 31.5ns。

ALE low to RE low delay in HCLK cycles:ALE到RE的延时,对应FMC_PCR寄存器中的TAR位,这四个位用于设置 ALE 到 RE 的延迟: 0000~1111,表示 1~16 个 HCLK 周期。对应NAND FLASH 数据手册的 tAR 时间参数,这里设置的 t_ar=(TAR+SET+2)* Tfmc_ker_ck。 TAR就是本寄存器的设置值, SET 对应 MEMSET 的值(我只用到 MEMSET), Tfmc_ker_ck 对应fmc_ker_ck 的周期。 MT29F4G08 的 tAR 时间最少为 10ns,我们设置 TAR=5,则 t_ar 至少为 7个 fmc_ker_ck 即 31.5ns。

NAND common space timing in HCLK cycles为NAND 通用存储器空间时序,NAND attribute space timing in HCLK cycles为NAND 特性存储器空间时序,这两个参数信息设置一致即可。

Common space setup time:地址建立的时间,对应空间时序寄存器,FMC_PMEM中的MEMSET,这八个位定义使能命令( NWE/NOE)前,地址建立所需要的 fmc_ker_ck 时钟周期数,表示 NWE/NOE 的高电平时间, 0000 0000~1111 1110 表示 1~255 个 fmc_ker_ck 周期。MT29F4G08 的 tREH/tWH 最少为 10ns,设置 MEMSET=3,即 4 个 fmc_ker_ck 周期,约 18ns。另外, MEMHOLD,也可以用于控制 NWE/NOE 的高电平时间,在连续访问的时候, MEMHOLD

和 MEMSET 共同构成 NWE/NOE 的高电平脉宽时间。

Common space wait time:对应空间时序寄存器,FMC_PMEM中的MEMWAIT,这八个位用于设置使能命令( NWE/NOE)所需的最小 fmc_ker_ck 时钟周期数(使能 NWAIT 将使这个时间延长),实际上就是 NWE/NOE 的低电平时间, 0000 0000~11111110 表示 1~255 个 HCLK 周期。 MT29F4G08 的 tRP/tWP 最少为 10ns,我们设置 MEMWAIT =5,即 6 个 fmc_ker_ck 周期,约 27ns。这里需要设置时间比较长一点,否则可能访问不正常。

Common space hold time:对应空间时序寄存器,FMC_PMEM中的MEMHOLD,这八个位用于设置禁止使能命令( NWE/NOE)后,保持地址(和写访问数据)的 fmc_ker_ck 时钟周期数,也可以用于设置一个读写周期内的 NWE/NOE 高电平时间, 00000000~1111 1110 表示 0~254 个 HCLK 周期。我们设置 MEMHOLD=2,表示 2 个 fmc_ker_ck 周

期,加上前面的 MEMSET,所以 NEW/NOE 高电平时间为 6 个 HCLK,即 27ns 左右。

Common space Hi-Z time:对应空间时序寄存器,FMC_PMEM中的MEMHIZ,这八个位定义通用存储空间开始执行写访问之后,数据总线保持高阻态所持续的 fmc_ker_ck 时钟周期数。该参数仅对写入事务有效, 0000~1111 1110 表示 0~254 个 fmc_ker_ck周期。我们设置 MEMHIZ=3,表示 3 个 fmc_ker_ck 周期, 即 13.5ns 左右。

Page size:Nand Flash芯片每页的字节数。

Spare area size:Nand Flash芯片每页中备份区域的字节数。

Block size:Nand Flash芯片中每块的字节数大小,字节限制为0-4294967295,因为最高支持的容量为4GB。128K+4K=135168。

Block number:Nand Flash芯片中块的数目。

Phane number:Nand Flash芯片中平面的数目。

Phane size:Nand Flash芯片中每个平面的字节数,128K+4K=135168,135168*1024=138412032。

(2).配置GPIO Settings

根据电路原理图,配置相应的管脚

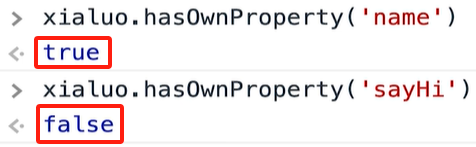

9.MT29F4G08芯片时序时间表

10.MPU和Nand Flash的关系

特别注意,STM32芯片中带有MPU功能的在使用Nand Flash芯片时需要配置对应地址的MPU,否则将会导致读写数据不成功。