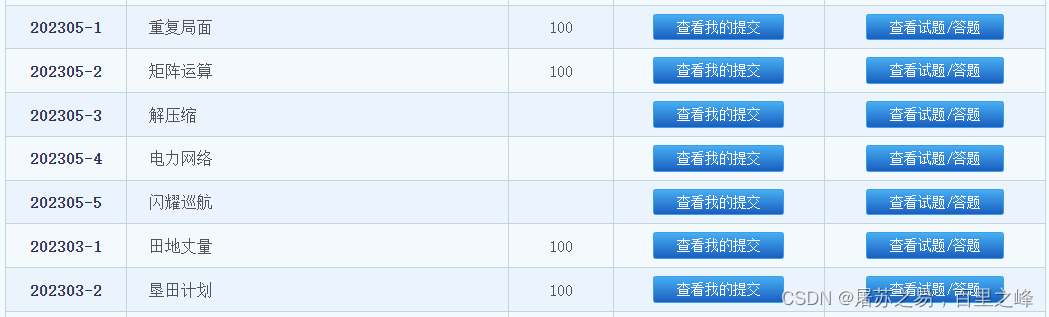

1、内存控制器概述

龙芯处理器内部集成的内存控制器的设计遵守 DDR2/3 SDRAM 的行业标准

(JESD79-2 和 JESD79-3)。在龙芯处理器中,所实现的所有内存读/写操作都遵守 JESD79-2B 及 JESD79-3 的规定。龙芯处理器支持最大 4 个 CS(由 4 个 DDR2 SDRAM 片选信号实现,即两个双面内存条),一共含有 19 位的地址总线(即: 16 位的行列地址总线和 3 位的逻辑 Bank 总线)。龙芯处理器在具体选择使用不同内存芯片类型时,可以调整 DDR2/3 控制器参数设置进行支持。其中,支持的最大片选(CS_n)数为 4,行地址(RAS_n)数为 16,列地址(CAS_n)数为 15,逻辑体选择(BANK_n)数为 3。CPU 发送的内存请求物理地址可以根据控制器内部不同的配置进行多种不同的地址映射。龙芯处理器所集成的内存控制电路只接受来自处理器或者外部设备的内存读/写请求,在所有的内存读/写操作中,内存控制电路处于从设备状态( SlaveState)。

龙芯处理器中内存控制器具有如下特征:

#接口上命令、读写数据全流水操作

# 内存命令合并、排序提高整体带宽

#配置寄存器读写端口,可以修改内存设备的基本参数

#内建动态延迟补偿电路(DCC),用于数据的可靠发送和接收

#ECC 功能可以对数据通路上的 1 位和 2 位错误进行检测,并能对对 1 位错误进行自动纠错

#支持 133-800MHZ 工作频率

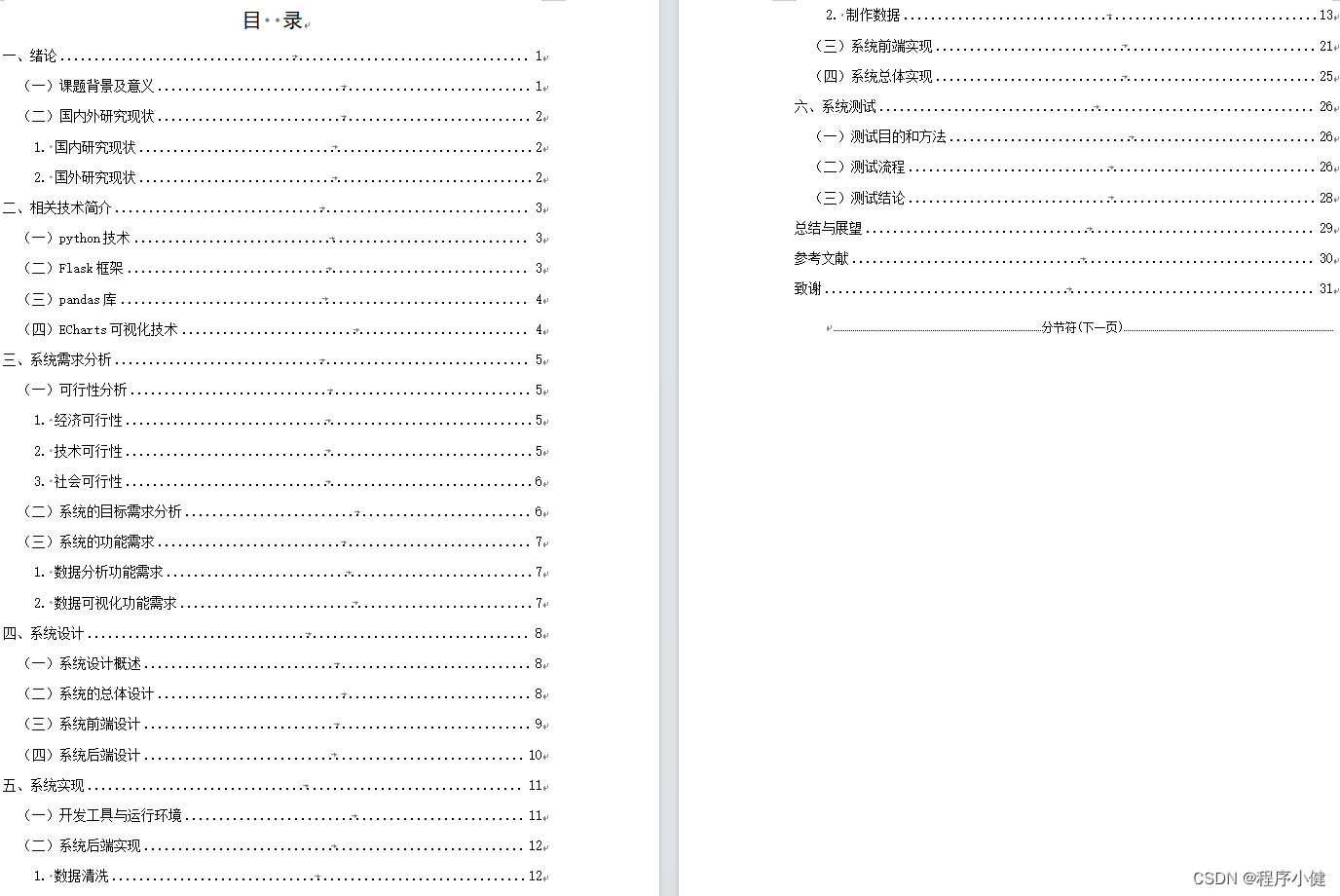

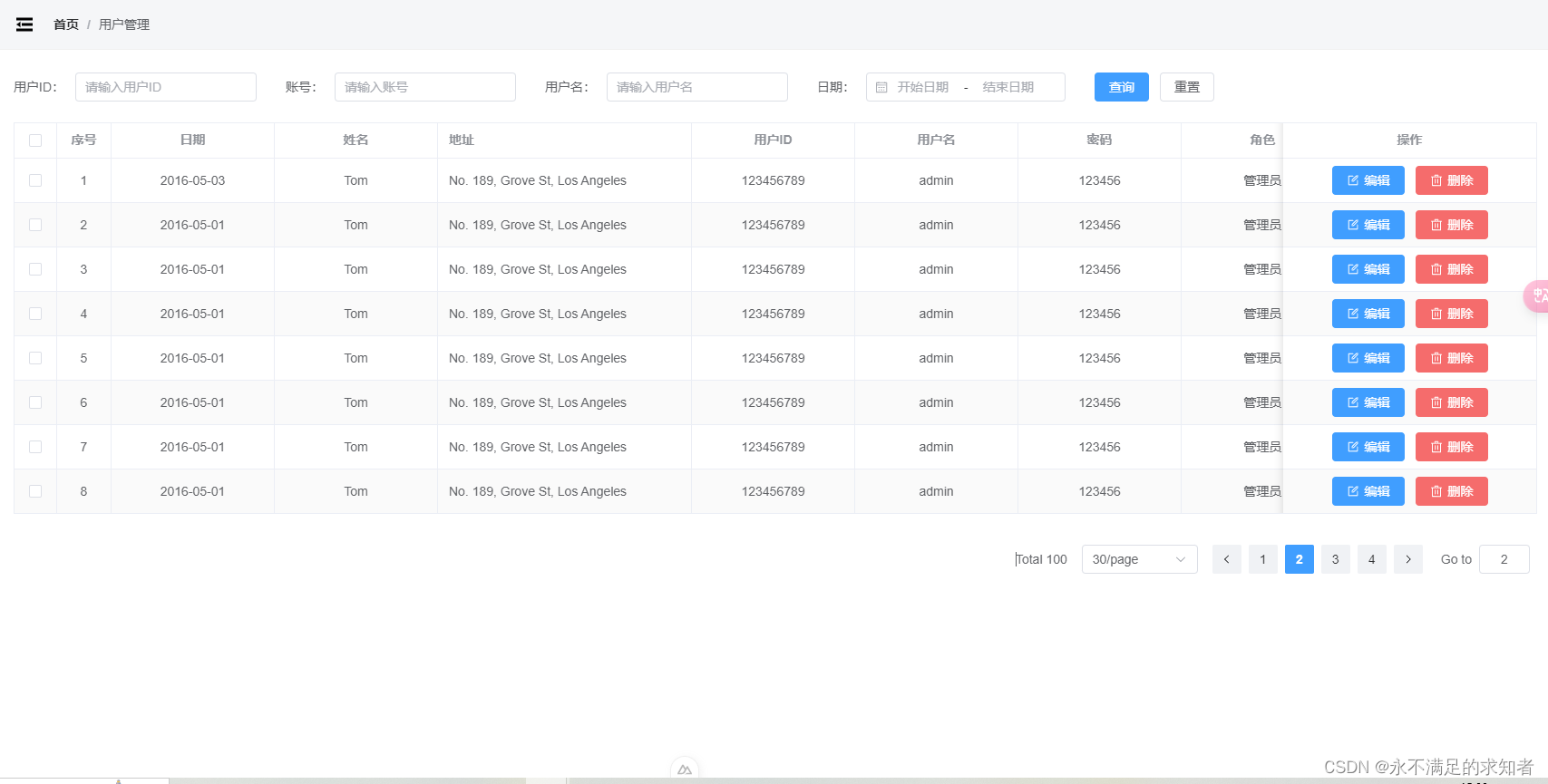

2、龙芯内存控制器结构

龙芯内存控制器主要结构图如上图所示,主要模块包括:

streambuffer:用于内存数据预取,以降低内存访问延时、提升内存带宽; command scheduler: 基于优化的调度策略,对接收到的访存命令重排序,以降低访存冲突,提升内存带宽。timing control: 该模块主要按照 JEDEC 协议的要求处理内存接口的时序,以保证访问内存的命令不会违反协议。PHY interface: 该模块主要处理内存接口的信号。内存训练相关的控制、 内存读写信号的时序处理以及输出驱动能力的调整、阻抗匹配这些功能都通过该模块实现。

configure manager: 管理内存控制器所有的配置寄存器,也是硬件与软件的接口。

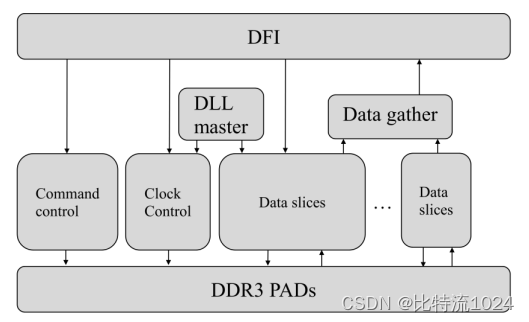

3、龙芯内存控制器 PHY 结构

PHY 主要结构图如图 2-2 所示,主要模块包括:

Dll master:DLL 主控模块,用于计算一个时钟周期内延时单元个数;

Command control:控制发给内存的命令、地址及控制信号,同时实现 2T/3T

功能;

Clock control:控制发送到内存的时钟信号,为了便于调试,实现了内存时钟

信号的任意相位调整功能;

Dataslice: 数据控制模块,用于实现内存要求的 DQ-DQS 关系以及 PAD 输

出使能的控制等功能。

Datagather:用于收集读返回数据并送给上层逻辑电路。