1.总线简介

什么是总线?首先,在学习AMBA总线之前,我们先对总线下一个定义。根据维基百科的定义:总线(Bus)是指计算机组件间规范化的交换数据(data)的方式,即以一种通用的方式为各组件提供数据传送和控制逻辑。根据chatgpt的解释:总线(Bus)是计算机中用于传输数据、地址和控制信号的一组共享的物理电线或逻辑路径。通过总线,不同的组件和设备可以相互通讯,并进行数据交换。计算机系统中的总线可以分为多种类型,如地址总线、数据总线、控制总线等,它们都有各自的作用和特点。总线的速度、宽度和时序等参数决定了计算机的性能和可扩展性。总线技术是计算机硬件设计的核心内容之一,也是高速、稳定、可靠的计算机系统的基础。

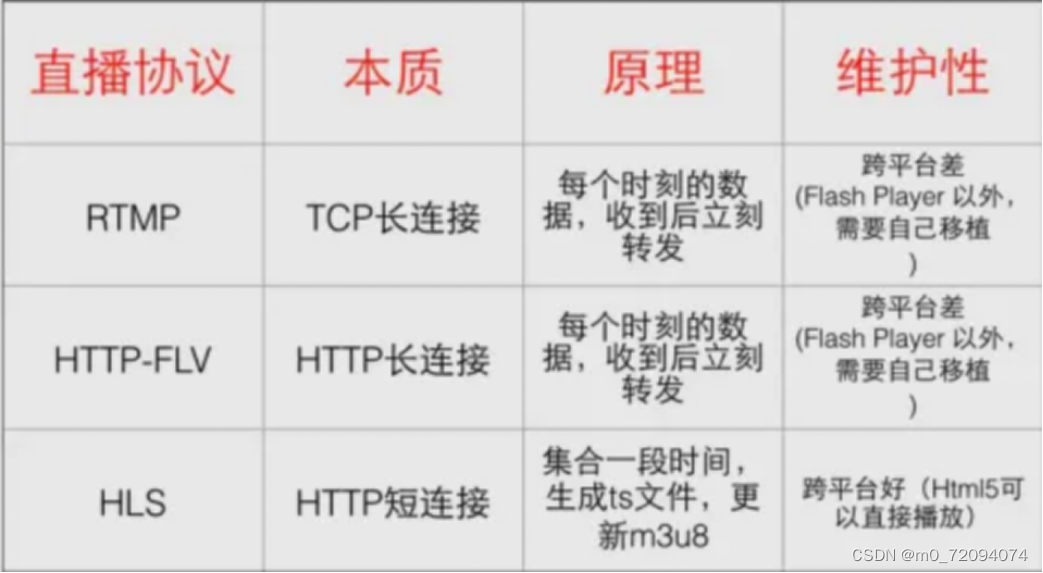

当我们谈到总线的时候,大致可以将其分为片上总线和片外总线。其中片外总线一般指的是两颗芯片或者两个设备之间的数据交换传输方式,包括UART、I2C、CAN、SPI等都可以纳入这一范畴。而AMBA总线为片上总线,即同一个芯片上不同模块之间的一种规范化交换数据的方式。基于片上总线,我们可以非常迅速的搭建SoC,AMBA总线在片上总线处于绝对统治的地位,对于芯片工程师而言,必须掌握AMBA总线。

对于总线而言,有以下比较重要的性能指标或者是概念需要掌握:

- 带宽:指的是单位时间内总线上传送的数据量;其大小为总线位宽*工作频率(单位为bit,但通常用Byte表示,此时需要除以8)。

- 位宽:指的是总线有多少比特,即通常所说的32位,64位总线。

- 时钟频率:以MHz或者GHz为单位。

- 延迟:一笔传输从发起到结束的时间。在突发传输中,通常指的是第一笔的发起和结束时间之间的延迟(什么事是突发传输后面再讲)。

- 传输方式:总线传输数据的方式主要有同步传输和异步传输两种模式。同步传输通过时钟信号来控制数据的传输,而异步传输则是直接在总线上进行数据交换

2.AMBA总线

AMBA总线规格

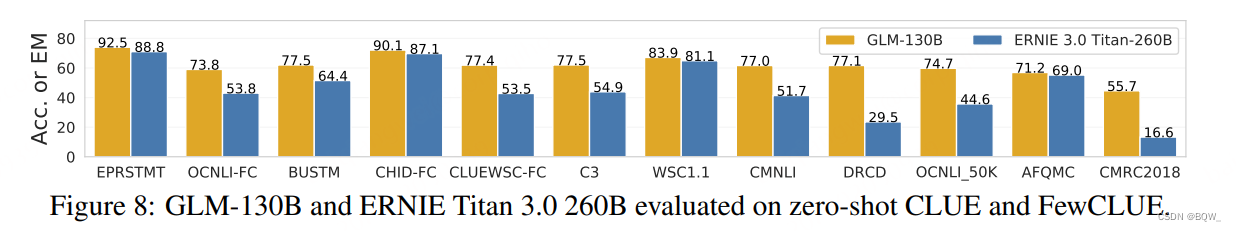

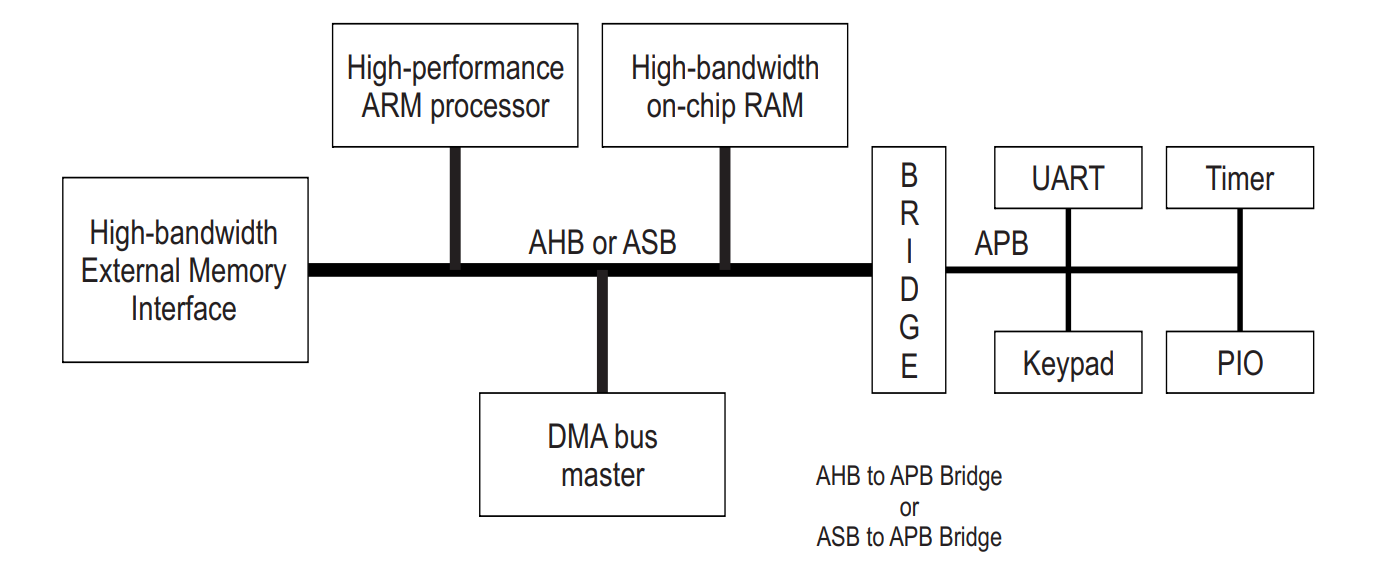

AMBA的全称为Advanced Microcontroller Bus Architecture。AMBA为一系列的协议,其为ARM公司的知识产权。其定义了SoC各个模块之间是如何互联,如何通信的。虽然AMBA直接翻译过来为高级微控制器总线架构,但实际上其应用场景已经远远不止于微控制器上。下图为基于AMBA总线的一个互联架构。可以看到基于AMBA总线,可以快速的将各个模块连接起来。

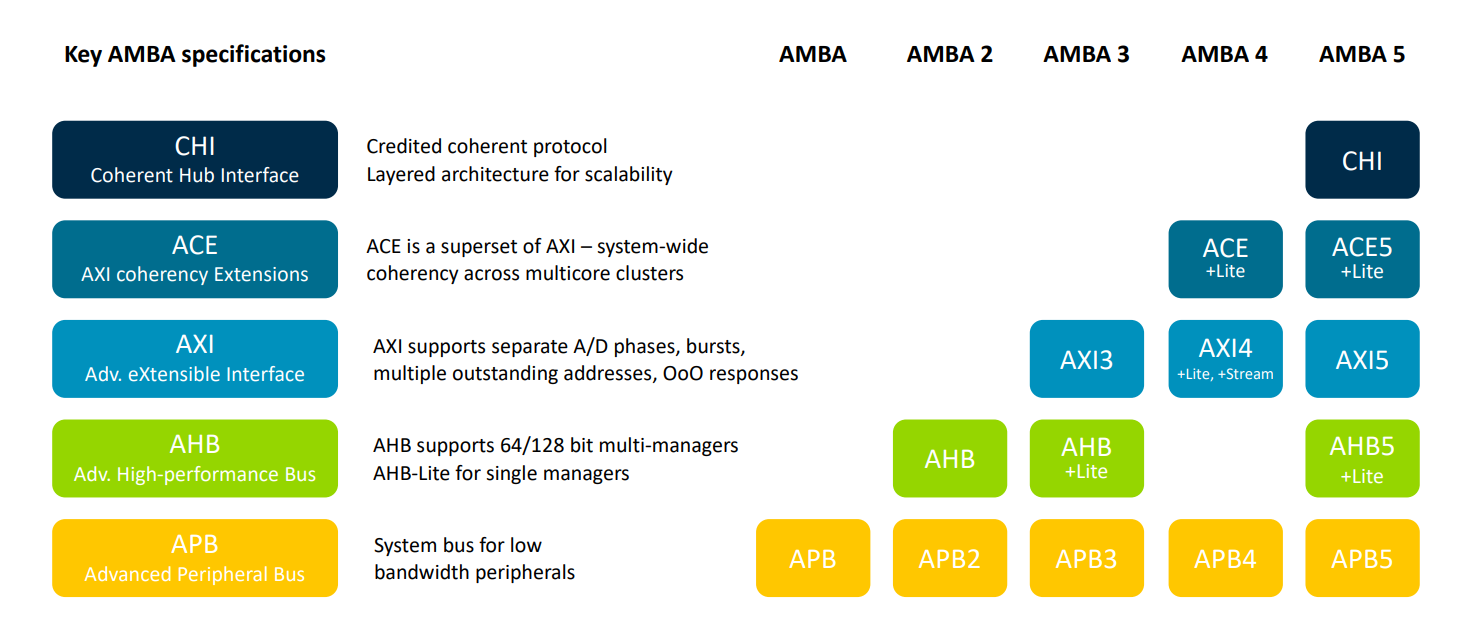

前面已经提到,AMBA是一系列的协议。其最早由ARM于1996年提出,一经发出便取得了巨大成功。其发展历史如下图所示。由于AMBA发展时间很久,出现了多代产品。其中的某个协议的叫法也存在不同。因此有以下几点需要说明,AMBA“X”代表了第多少代协议:

- AMBA1已经不用掌握了,因为市场已经抛弃了这代协议。

- AMBA2推出了AHB协议,该协议沿用至今;而AMBA2中的APB2协议,也已经被市场抛弃了。

- AMBA3推出了APB3、AXI3、AHB-lite协议(ATB协议是用作CPU的trace的,绝大部分人都不会用到)。需要注意的是,AXI3代表的含义是,第三代AMBA总线中的AXI协议。这也是AXI协议的首次提出。因此也没有AXI1和AXI2协议!APB3和AHB-lite目前仍然广泛使用,后面会进行讲解。

- AMBA4推出了ACE协议,以及AXI的兄弟协议,AXI-lite和AXI-stream。

- AMBA5对AXI、AHB和ACE协议进行了优化,此外还推出了CHI协议。

APB1.0一般指的是2003年发布的AMBA3中的APB版本,也就是APB3。而APB2.0一般指的是2010年发布的AMBA4中的APB的2.0版,也就是APB4(是不是听到这里已经晕了,再结合图片看看)

对于AMBA协议,APB的信号都是以P开头,AHB的信号都是以H开头,而AXI的信号都是以A开头。

3.APB总线

APB的全称为Advanced Peripheral Bus,高级外设总线。顾名思义,其设计之初的主要目的就是用该协议连接外设。但由于APB总线自发布至今已经过去了20多年了,因此以现在的眼光看,该总线没有什么高级一说,其连接的外设也往往是低速且低功率的外设,如I2C、UART、SPI等,除了连接低速外设之外,APB总线还广泛用于配置各种IP的寄存器(这些IP预留用户控制信号,由软件进行配置,这个时候就可以选择使用APB总线来配置这些寄存器)。此外为了使得APB能够容易的被整合进大部分的设计流程中,APB规定所有的信号必须在时钟的上升沿进行传递。

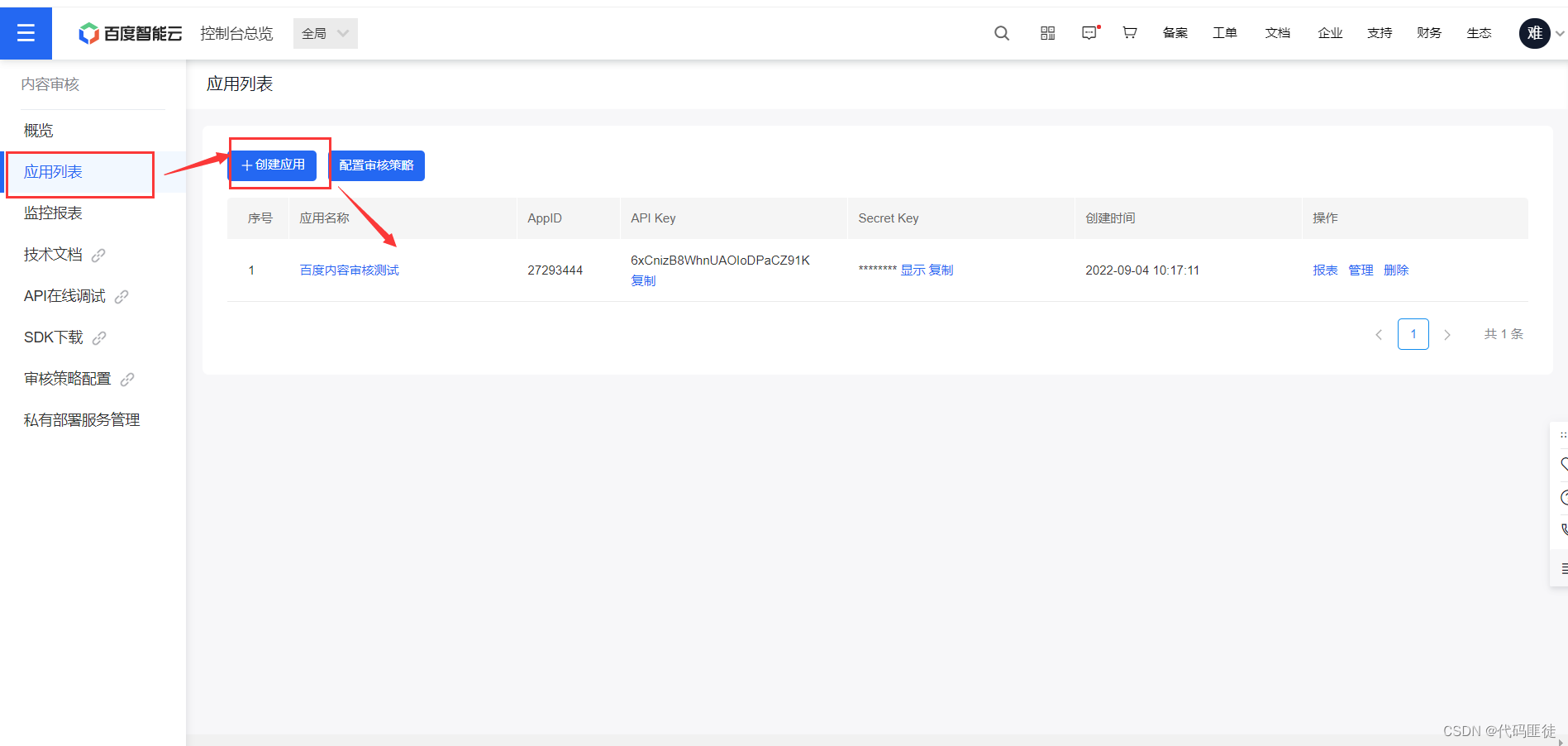

一个SOC的典型架构

下面简单介绍一下APB的发展历史,ARM公司于1998年发布了APB2,又于2003年发布了APB3,在2010年又发布了APB4。目前最常见的为APB3或APB4,其主要区别如下:

- APB2:

- APB总线的基础版本。

- APB3:

- 增加PREADY信号:用于反压master

- 增加PSLVERR:用于代表传输是否发生错误

- APB4:

- 增加PPROT保护信号。

- 增加PSTRB代表字节选通。

- APB5:

- 增加PWAKEUP信号,从机唤醒功能

- 增加PAUSER信号,用户请求分配

- 增加PWUSER信号,用户写数据分配

- 增加PRUSER信号,用户读数据分配

- 增加PBUSER信号,用户数据分配

3.1 APB信号列表

| 信号名 | 方向 | 说明 | 版本 |

|---|---|---|---|

| PCLK | Global | 时钟信号,上升沿同步 | APB2/3/4/5 |

| PRESETn | Global | APB总线复位信号为低有效并且通常将该信号直接连接到系统总线的复位信号 | APB2/3/4/5 |

| PADDR | M-->S | 地址总线,最多可高达32位 | APB2/3/4/5 |

| PSEL | M-->S | 选通信号,当该信号拉高意味着要发起一次传输了 | APB2/3/4/5 |

| PENABLE | M-->S | 使能信号,用于表示一次APB传输的第二个周期(在阻塞情况下为第二个及以上的周期,该信号的存在完全是历史遗留问题,后面详细讲) | APB2/3/4/5 |

| PWRITE | M-->S | 该信号为高标志这次是写传输,反之则为读传输 | APB2/3/4/5 |

| PWDATA | M-->S | 写数据总线,由Master在写周期进行持续性驱动(PWRITE为高),支持8/16/32位。 | APB2/3/4/5 |

| PRDATA | S-->M | 读数据总线,由Slave在读周期进行持续性驱动(PWRITE为低),支持8/16/32位。 | APB2/3/4/5 |

| PREADY | S-->M | 指示外设是否已经准备好接收或发送数据 | APB3/4/5 |

| PSLVERR | S-->M | 指示外设是否存在错误 | APB3/4/5 |

| PPROT | S-->M | 用于实现外设的访问保护,保护外设不受未授权的访问和恶意攻击 | APB4/5 |

| PSTRB | S-->M | 用于指示主设备传输的数据位(byte或者word)是否有效 | APB4/5 |

| PWAKEUP | S-->M | APB5 | |

| PAUSER | S-->M | APB5 | |

| PWUSER | S-->M | APB5 | |

| PRUSER | S-->M | APB5 | |

| PBUSER | S-->M | APB5 |

- PREADY

PREADY(Peripheral Ready)信号用于指示外设是否已经准备好接收或发送数据。当外设准备好时,它会将PREADY信号置为逻辑高电平,表示它已经可以接受或发送数据。主设备将等待该信号的出现,然后将数据发送给外设或者接收从外设发来的数据。

对于写操作而言,PREADY信号用于标志slave设备是否已经准备好接收这一笔数据。而对于读操作而言,PREADY信号用于标志slave设备是否已经准备好了要返回给Master的数据。

有了PREADY信号,从机就可以反压主机。因此PREADY这个信号可以说是非常的棒啊,它让主从之间的通信更加的可靠,也增加了从机的控制能力,不至于出现主机写的数据从机压根没收到或者从机没有准备好读数据,进而主机读到错误的数据的情况。

此外我再讲解一下为什么会出现从机没有准备好的情况。对于读操作而言,非常好理解,你要读的数据我还没准备好呢(可能正在运算),那我当然不能拉高PREADY,不然就给了你错误的数据了。只有我数据准备好的时候,我拉高PREADY,这样才能确保读不出问题。而写的话,这种情况往往出现在写特定的地址,这个时候外设本身要进行判断是否可以写,因此两个周期就完成不了,就暂时不能拉高PREADY,你的Master就必须要维持住。当PREADY拉高代表这一拍能够写进去了。因此主机也就可以不再维持原有的状态了。

- PSLVERR

PSLVERR(Peripheral Slave Error)信号用于指示外设是否存在错误。当外设在处理主设备的请求时遇到错误时,它会将PSLVERR信号置为逻辑高电平,通知主设备发生了错误。

用于从slave向master返回传输错误,这个错误是slave自己定义的,比如写了不允许写的地址,即非法地址访问。或者是访问超时了,slave回应不了了。就可以拉高这个信号,从而避免总线锁死。

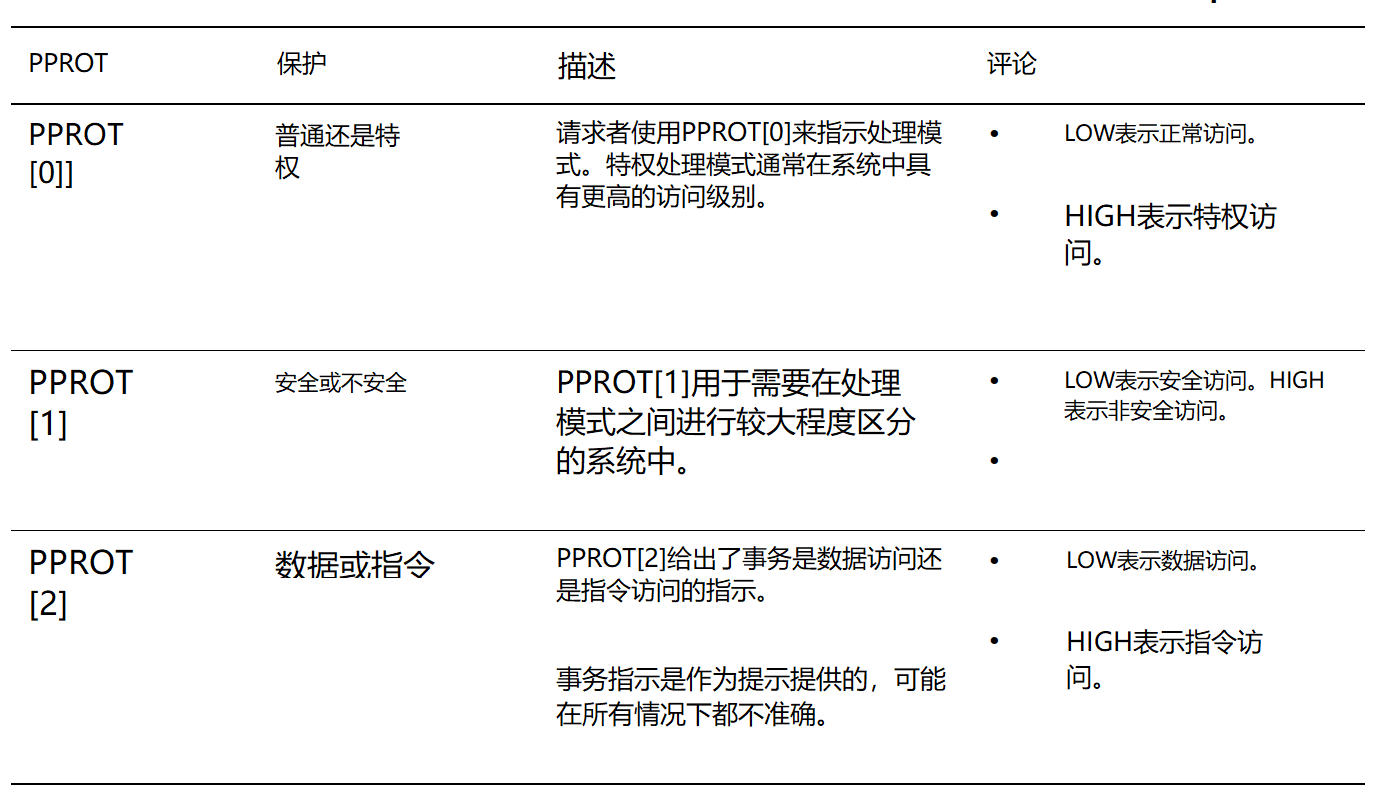

- PPROT

PPROT(Peripheral Protection)信号用于实现外设的访问保护,保护外设不受未授权的访问和恶意攻击。

对于CPU而言,可以工作在用户模式下也可以工作在特权模式下(比如RISC-V的USM三种模式)。对于支持trustzone的CPU,可以工作在secure world下,也可以工作在normal mode下。又由于现在的系统越来越复杂了,以前的外设是随意读写都可以,现在的一些外设或memory(比如一些CSR寄存器,Trusted RAM等)要求只能在secure下或者privileged模式下访问,因此就需要PPROT信号。

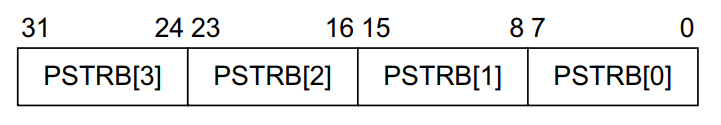

- PSTRB

PSTRB(Peripheral Strobe)信号用于指示主设备传输的数据位(byte或者word)是否有效。主设备在传输数据时,需要使用PSTRB信号来标识传输的数据位是否有效,以确保外设可以正确接收和处理数据。

允许稀疏的写。其中的每一个比特对应于PWDATA的每一个字节。用1代表PWDATA的这一字节是否有效,其对应关系如下图所示

3.2 APB传输

3.2.1 APB状态机

APB2的状态机

- IDLE:此时为默认状态。PSEL和PENABLE都为0,没有通信请求。

- SETUP:当需要发起传输的时候,会进入该状态,此时PSEL为1,PENABLE为0。PSEL从0到1说明要发起一次传输了,而PENABLE为0表示这是传输的第一个时钟周期。(这个状态也就是setup phase)

- ENABLE:这个状态PENABLE需要拉高,进而完成数据的传输。

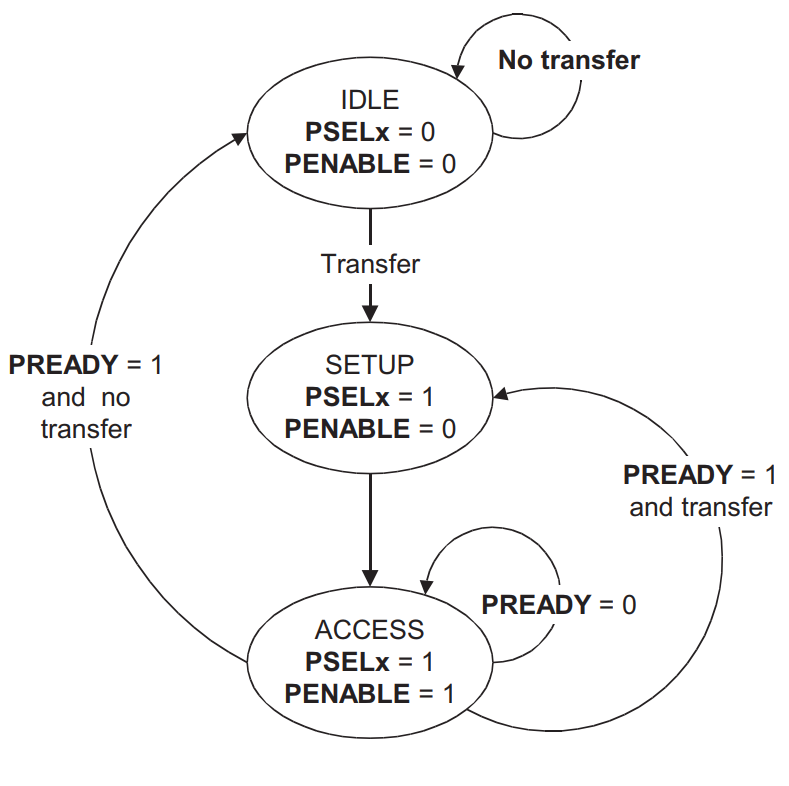

APB3/4/5的状态机

状态机有以下几种状态:

- IDLE:APB的默认状态。

- SETUP:当需要传输时,总线进入SETUP状态,在此状态下断言适当的选择信号PSELx。总线只在一个时钟周期内保持SETUP状态,并且总是在时钟的下一个上升沿移动到ACCESS状态。

- ACCESS:在ACCESS状态下断言启用信号PENABLE。在从SETUP到ACCESS状态的转换过程中,地址、写、选择和写数据信号必须保持稳定。退出ACCESS状态由从机发出的PREADY信号控制:

- 如果从机将PREADY保持为低,则外设总线保持在ACCESS状态。

- 如果从机驱动PREADY为高,则退出ACCESS状态,如果不再需要传输,则总线返回到IDLE状态。或者,如果接下来发生另一次传输,总线将直接移动到SETUP状态。

3.2.2 APB2读写操作

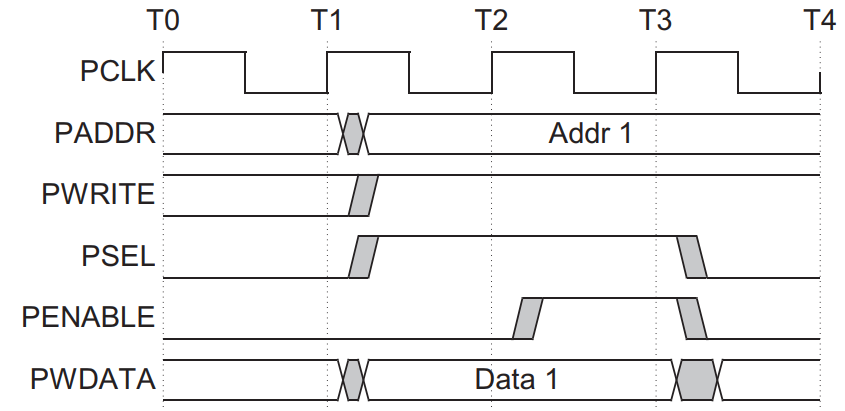

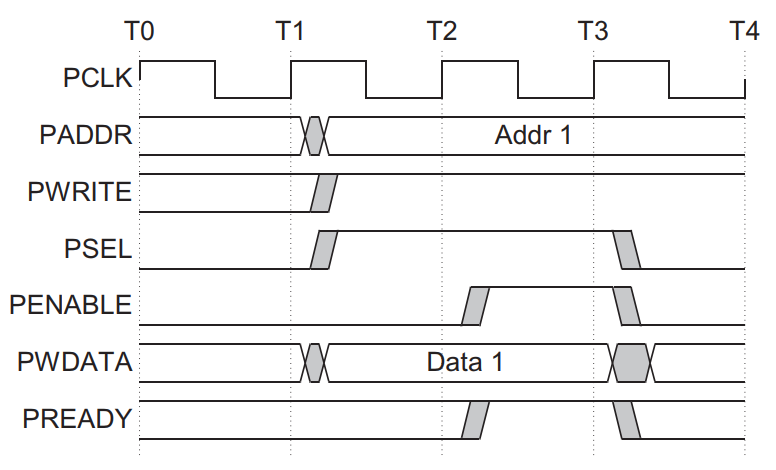

- 写操作

可以看到写操作非常的简单:

- T1->T2这一个周期

- PSEL信号拉高,意味着要发起一次新的传输了。

- PWRITE信号为1,因此此次传输为写操作。

- PWDATA为要传输的数据,PADDR为要写的地址。二者都应该保持不变,直到此次传输结束。

- 而PSEL拉高的第一个时钟周期,PENABLE应该为0。

- T2->T3这一个周期

- PSEL信号继续拉高

- PWRITE、PADDR、PWDATA应该保持不变

- PENABLE信号拉高,用于代表这已经是写传输的第二个周期了

至此一次传输结束。可以看到,APB对每一笔数据的传输,需要花费两个时钟周期。且APB的数据传输不支持流水线操作(即不可以重叠)。因此APB是非常低效的。

理论上写数据完全可以同时给出写地址和写数据,一拍就搞定,为什么APB要大费周章弄成两拍呢?这主要是那个年代的芯片本身的制程工艺以及片上互连线导致的。一个周期可能无法完成从Master向Slave写入数据的整个操作流程。因此采用两拍的方式,第一拍告诉你,我要开始传输啦!(称为setup phase)第二拍才真正的完成数据的传输。(称为access phase)。

如果Master想要马上发起一次新的传输,可以不拉低PSEL让其继续为1,但是必须要将PENABLE拉低。否则Slave侧的判断逻辑就会出现问题!

由于APB向下兼容,这一历史遗留问题一直延续至今。不过好在APB应用的场景本身就是配置寄存器等操作,因此多花一个时钟周期也没什么大不了的。

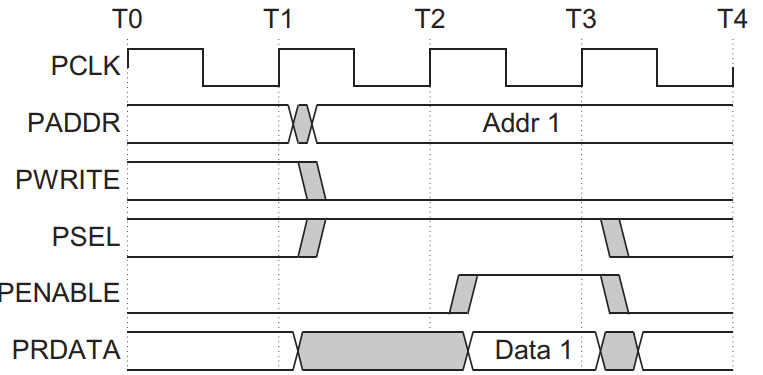

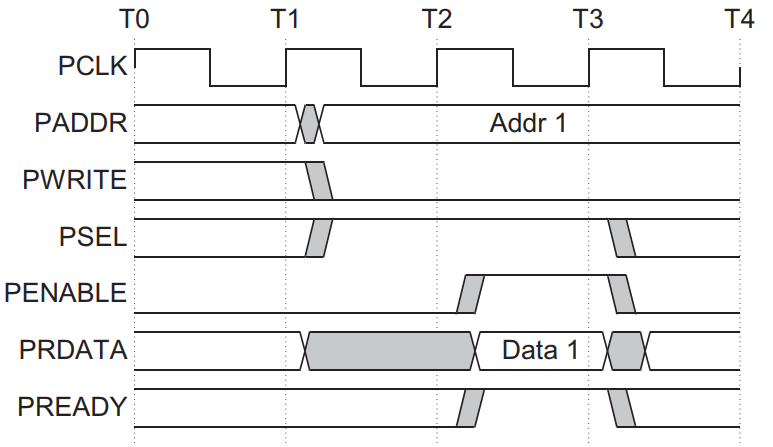

- 读操作

可以看到读操作非常的简单,跟写几乎一样。这里就不再做详细的解释了。

要特别注意的是,T2以后,也就是进入ENABLE周期后,APB的SLAVE设备必须要将M所需要读取的数据准备好,以便M可以在ENABLE的周期末也就是T3正时钟沿触发时正确的将数据读取。

3.2.3 APB3读写操作

- 写操作

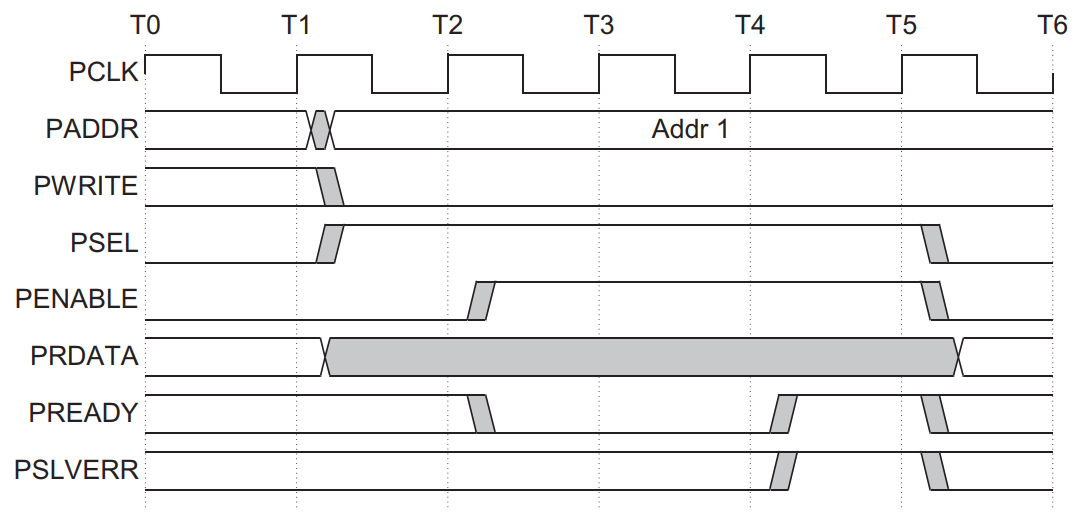

- 读操作

上图是没有wait states的情况。两拍完成写操作。和APB2的区别在于多了个PREADY,需要在传输的第二拍也就是真正发生数据传输的那一拍拉高。其它的和上面的写时序是一模一样的,因此不再讲解。

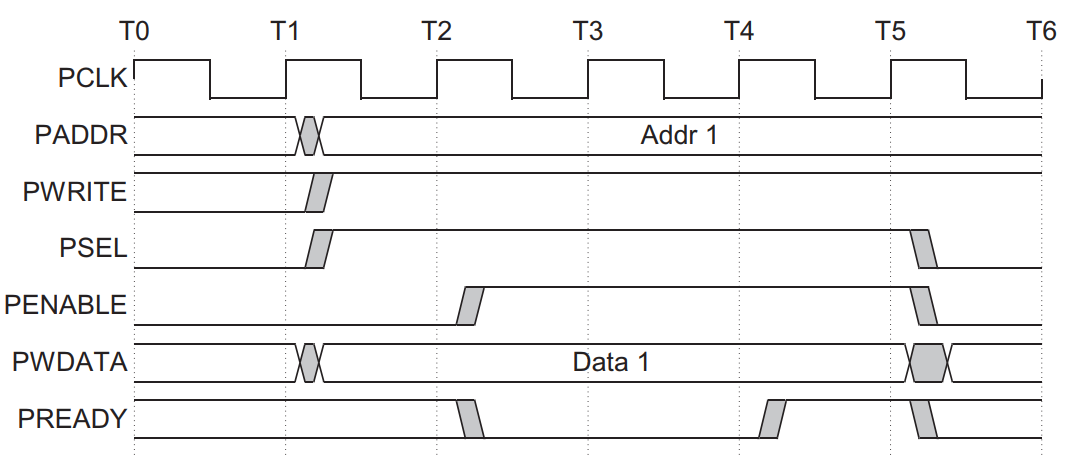

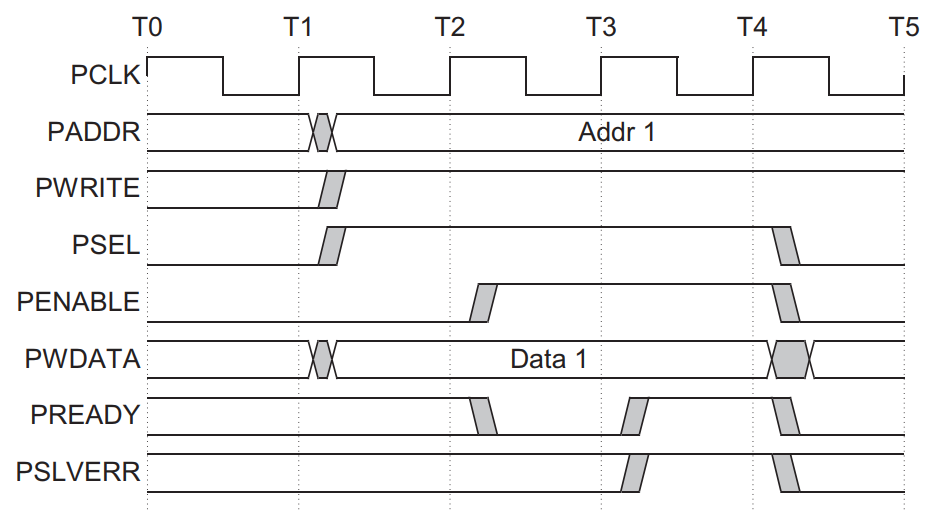

- 写操作(等待)

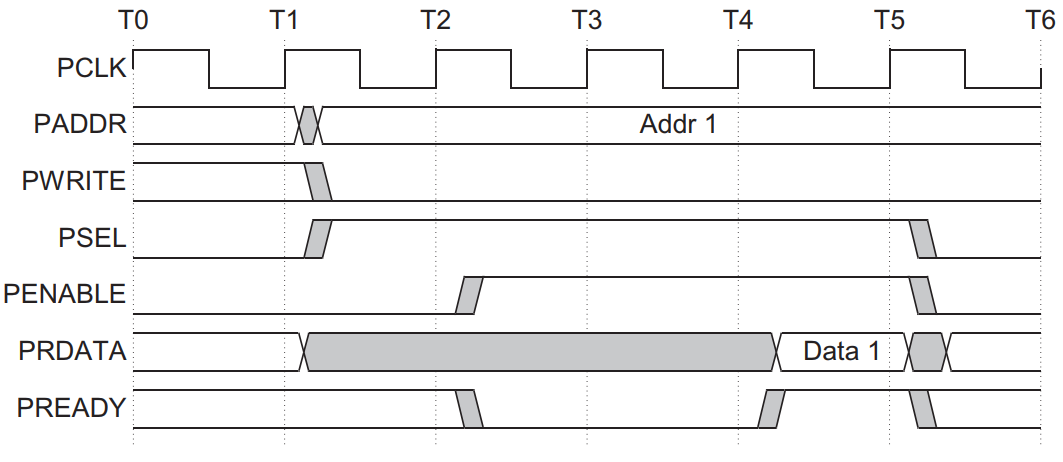

- 读操作(等待)

我们再看看有wait states的情况,上图四拍才完成写操作。此时setup还是一个周期(从T1->T2),而access是三个时钟周期(从T2->T5)。可以看到主机的信号应该保持不变,一直持续到从机的PREADY信号拉高以后,等待拉高以后的这一拍完成传输,才可以改变其它的信号。(即T1->T5这段过程,PADDR、PWRITE、PSEL、PWDATA都应该保持不变)。

- 写操作(错误)

- 读操作(错误)

读写操作进行中PSLVERR信号拉高,表明此次写/读操作有误,所写入/读取的数据未正确写入/读取。

3.3 版本兼容

以APB4的slave和APB3的master为例,这个时候应该把PSTRB信号固定为全1,PPROT信号则取决于Slave是如何使用该信号的,根据不同的场景固定为不同的值。

而APB3的slave和APB4的master相连接,这个时候实际上需要一个转接桥,因为本身可能只想写某一个字节,而slave此时不支持也不知道,那就需要一个中间逻辑将pwdata变成想要的值。(比如读回来时32'h2345,想将最高字节改写为6,此时只写一个32'h6000,PSTRB为1000,标志别的字节不要动。这个时候就需要一个中间逻辑将写的数据变成32'h6345)。实际上写起来也很麻烦,因此此时最好将APB3的slave改成APB4协议。

至于APB3和APB2不建议一起用,因为APB2没有PREADY反压机制,因此实际使用起来完全不一样,强行一起用会有巨大的坑。

3.4 APB2AHB

待补充

3.5 APB参考

- 深入理解AMBA总线(一)APB总线入门

https://zhuanlan.zhihu.com/p/623829190

https://zhuanlan.zhihu.com/p/623829190 -

深入理解AMBA总线(二)APB slave设计

https://zhuanlan.zhihu.com/p/624022715

https://zhuanlan.zhihu.com/p/624022715 -

AMBA总线协议(一)——一文看懂APB总线协议

https://blog.csdn.net/vivid117/article/details/107511746

https://blog.csdn.net/vivid117/article/details/107511746