目录

摘要

0 引言

1 为什么需要 2000A 的数字电子产品?

2 2000A 的供电电源设计

2.1 "MPM3698+ 2*MPM3699"的 MPS扩展电源架构

2.2 使用恒定导通时间(COT)模式输出核心电压的原因

2.3 模块化 VRM 的优势

2.4 用步进负载验证2000A的设计难点

2.4.1 电源网络

2.4.2 电压调节

2.4.3 建模与分析

2.4.4 模拟负载

2.4.5 瞬态分析

2.4.6 噪声分析

2.4.7 热分析

2.4.8 测量设备

2.4.9 小信号和大信号

2.4.10 测试方法

2.4.11 设计迭代和改进

2.4.12 安全

2.5 基于测试的元件建模

2.6 对电磁 (EM) 模型的需求

2.7 端到端的数字孪生模拟

3 测量案例研究

4 结论

参考文献

附录--测量微欧姆(μΩ)的CMRR校正

摘要

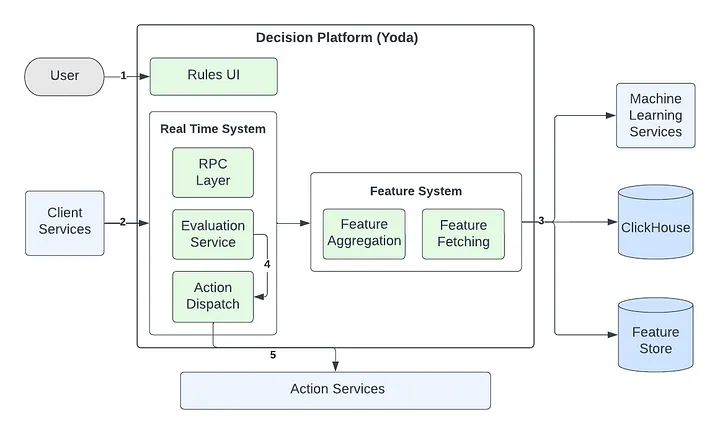

本文的目的是演示如何使用一个2000A 阶跃电子负载对2000A PCB核心电源网络(PDN)设计进行有效验证。在此过程中,还需要进行可扩展的2000A供电网络的实际设计,包括并联电压转换器和多个控制回路,以此了解设计的权衡和挑战。并且,使用最新的基于测量的模型对转换器进行建模,然后使用最新的 EDA 仿真工具对瞬态、频率、EM、DC 和电热进行仿真,这对于节约硬件设备的采购资金投入是非常有意义的。另外,这种可扩展的 2000A PDN 设计还可用于演示带动态电流步进负载的核心电源的超高速测试,以验证大信号时域瞬态行为。

0 引言

本文通过设计、仿真和验证的全流程演示,阐明可扩展的2000APDN设计所面临的诸多挑战。针对大电流 PDN,选择合适的电源结构需要进行各种权衡分析,其中小信号和大信号控制回路响应尤为重要,并联转换器之间的电流共享也是一个关键的考虑因素,并且涉及PCB的布局对称以及电源模块和中央控制器之间的通信,这些因素都需要通过仿真进行具体的评估和分析。

除此之外,研究中还包含对其他layout设计因素的考虑。例如,干净的电压检测走线通常被设计用于传输靠近 ASIC 封装甚至在ASIC封装上的工作电压。然而,通过仿真和测量来验证检测线上的串扰噪声并确定与2000A开关负载的关联性是至关重要的。此外,测量和验证2000A 电源输出电流质量的方法既复杂又具有挑战性。评估中,将电源网络加载到ASIC 的极限峰值功率是必要的,但如果ASIC 尚未可用,则必须为 PCB PDN 的早期设计选择合适的步进负载设备。另外,评估大信号响应需要用代表 ASIC封装极限的边沿转换速度以动态调制电源网络,通常在100MHz左右或上升/下降时间约为3ns。虽然实现大电流、高速调制具有挑战性,但动态电流的测量不妨碍动态边沿的正常转换也是至关重要的。

本文全面介绍了上述的这些话题,并提供了一个完整的设计、仿真和验证2000A核心电源电压网络的流程。该流程基于一个定制设计的评估板来实现,该评估板带有水冷超高速插座式负载,该负载采用最新的电源完整性仿真软件进行设计。如图1所示,展示了评估板工作在 256A 时的测试场景。

1 为什么需要 2000A 的数字电子产品?

虽然 2000A 看似夸张,但人工智能、数据中心和超级计算机日益增长的处理能力已经超过了目前的水平。用于AI应用的 NVIDIA H100 Tensor Core GPU约为750A,但预计下一代 X100将需要约 1500A。224G SerDes收发器的指数级扩展也将极大地增加工作电流。可以预期,随着技术创新对计算能力的要求越来越高,消耗电流的量级将会继续增加。

一些公司正在评估将2000A总电流分散在多个芯片上的布局方案,以减少每个芯片的电流消耗。虽然这个概念很有趣,但总电流仍然高达2000A,并且增加了额外的设计成本。

一些供应商已经开发了可扩展的 VRM解决方案,它们既可以支持低电流应用(低至150A到200A),也可以提供2000A以上的可扩展性。每个供应商都为其解决方案选择了不同的电源拓扑,因此本文将会对这些拓扑选项进行考察。

2 2000A 的供电电源设计

目前有两种主要的架构路径,单级谐振转换器和两级电源设计:

单级谐振变换器架构可以高效地实现48V直接降压到核心电压[1]。然而,如果输入电压变化较大,而输出电压需要严格的精度调节,则谐振变换器的设计将面临很大的挑战性。当选择如图2所示的传统全桥串联谐振DC-DC变换器,设计从36V到54V的宽输入电压,得到输出稳压为1V,当负载电流变化较大时,谐振电感Llp需要设计得比变压器电感Lm大得多,以应对最坏情况[2]。由于Llp和Lm具有相同的电流,所以Llp的尺寸大于降压变压器,这大大降低了能量密度,增加了系统的复杂性。

另一种方法是使用两级电源。输入电压先被降压到一个中间电压值,如12V或5V,再降压到所需的核心电压。该解决方案有大量的分立组件或模块可供选择。此外,一级电源转换器不需要精度调节,因此,如上图所示的传统全桥串联谐振DC-DC变换器是该应用的理想选择,因为它可以以极高的效率提供非稳压的中间电压。与稳压变换器不同,非稳压变换器不需要大型Llp电感。在非稳压级的输出之后是一个稳压降压转换器,将12V或5V转换为核心电压。第二级的设计才是至关重要的,因为转换器需要保持一个高精度的输出电压,同时具备提供数百 A 电流,以及快速响应负载瞬变的能力。本文选择MPS 的 MPM3698 和 MPM3699 电源模块组合作为第二级电源,以提供所需的核心电压。

2.1 "MPM3698+ 2*MPM3699"的 MPS扩展电源架构

MPM3698 是一个完全集成的电压调节器模块(VRM)。标准化的数字接口,如PMBus,在负载处理器(如 FPGA 或大型ASIC)之间建立了预定义的通信协议。使用此控制协议,处理器可以命令 VRM 在低功耗模式和高性能模式之间快速切换。MPM3698 VRM 可提供高达120A的峰值电流,并与多个MPM3699模块配对,以进一步增加输出电流。每个MPM3699可以提供额外的160A峰值电流。如果将一个MPM3698模块和两个MPM3699模块组成一个输出电压模组,如图3所示,它们总共可以提供440A的峰值输出电流。MPM3698 和 MPM3699模块的可接受输入电压范围为4.5V-16V,输出电压范围为0.4V-3.3V。从而可以支持12V或5V电源输入,以及为不同的处理器提供不同的核心电压。本文采用5组这样的组合模块进行并联,以产生所需的2000A 输出电流(440*5=2200A)。

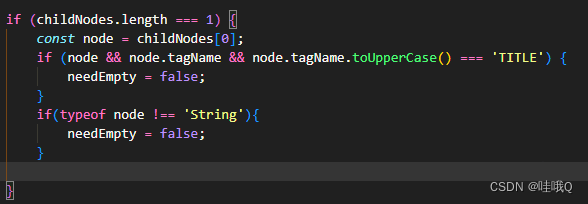

2.2 使用恒定导通时间(COT)模式输出核心电压的原因

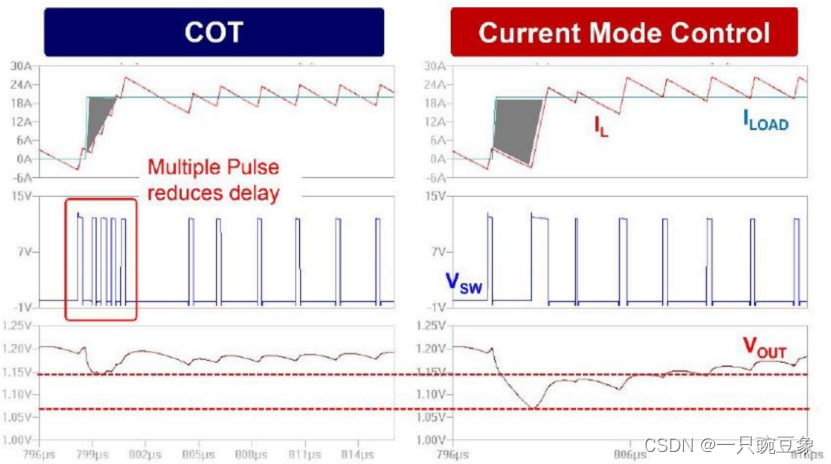

随着计算能力的提高,动态电流转换速率也在不断提高。对于一个电源来说,通常要求它提供至少200A/μs的转换速率。传统上,要求更高的瞬态转换速率将需要具有额外输出电容的设计来维持所需的电压调节的稳定性。然而,这种增加的所需电容总量可能非常大,此外,电容器占据了很大的PCB布局空间。参考文献[3]中的switching caps已经被评估用于减少输出电容器占用的物理空间,但它是以增加硬件和控制的复杂性为代价的。对于快速负载响应的另一种优化解决方案是使用恒定准时(COT)控制的DC-DC转换器。COT没有传统的电压或电流模式控制补偿器所带来的延迟[4]。如图4所示,COT控制具有更快的切换速度,减小了电感与输出电流之间的间隙,从而进一步减小输出下冲。这消除了复杂的控制回路设计,减少了所需的输出电容,节省了设计时间、材料成本和 PCB布局空间。

2.3 模块化 VRM 的优势

使用MPM3698和MPM3699的组合VRM作为解决方案的额外优点是功率密度和空间利用率。与分立元器件相比,单片VRM的集成度更高,功率密度也更大,另外,在设计分立降压变换器时,设计者需要通过最小化开关回路和防范任何噪声耦合来降低开关噪声,这是一个高级的设计挑战,需要多年的PCB 设计经验才能正确消除噪声。而电源模块厂商已经在其产品中集成了减轻VRM切换噪声的技术。设计者只需按照设计要求,在单片VRM 的输入和输出处放置适当的去耦电容器,从而极大地降低了设计难度,提高了设计效率。

2.4 用步进负载验证2000A的设计难点

电源完整性(PI)领域在过去几年中取得的飞跃式的发展,PI的测试验证也成为一项极其复杂的挑战任务。以下是在验证2000A阶跃负载的PDN 时需要考虑的环节:电源网络;电压调节;建模与分析;模拟负载(VRM->PCB->PKG->Die);瞬态分析;噪声分析;热分析;测量设备;小信号和大信号测试;测试方法;设计迭代和改进;安全。

2.4.1 电源网络

设计者必须彻底了解所设计的电源网络,包括但不限于:

1. 电源:VRM 厂商、类型、多相规模和数量、环路带宽频率等;

2. PCB:层数和厚度,元件,如电压调节器,电容器和电感器;

3. PKG: BGA 球数,核心电源的孔分布,电源层数,去耦电容器;

4. Die:芯片功率模型,RC模型。

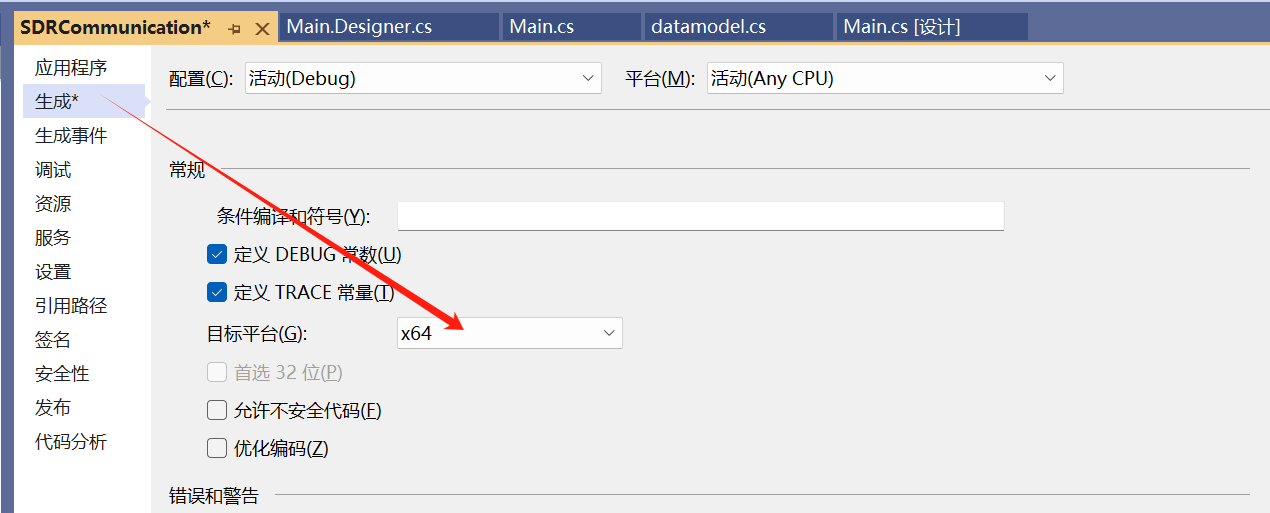

2.4.2 电压调节

选择正确的多相 VRM 解决方案对于实现成功的设计至关重要,需要分别验证VRM可以在稳态和瞬态状态下保持所需的供电电压水平,甚至在2000A阶跃负载中。

如今,越来越多的 VRM 供应商正在转向开关频率为3-10MHz的电源解决方案。这样做的好处是,ASIC 设计人员可以大幅减少PDN 电容,因为VRM 具有更高的环路带宽,可以覆盖更宽的功率传输带宽,但是,如何在较高频率下保持控制器的稳定和输出效率,依然是一个挑战。除此之外,在选择VRM时,还需要考虑使用负载的线性/非线性和自适应闭环控制的能力。

2.4.3 建模与分析

使用建模和仿真工具来预测负载将如何影响供电网络,系统中的电感、电容和电阻以及稳压器的瞬态响应都应考虑在内,还需要引入VRM、PCB、PKG 和 Die 的行为模型,而且在没有检查 Die的情况下,不要假设获取的Die模型的正确性,这一点至关重要[5]。根据芯片性能和功率分布,需要从负载到PCB检测位置添加所需的观测点,以便可以通过仿真和测量来获取对比数据。

2.4.4 模拟负载

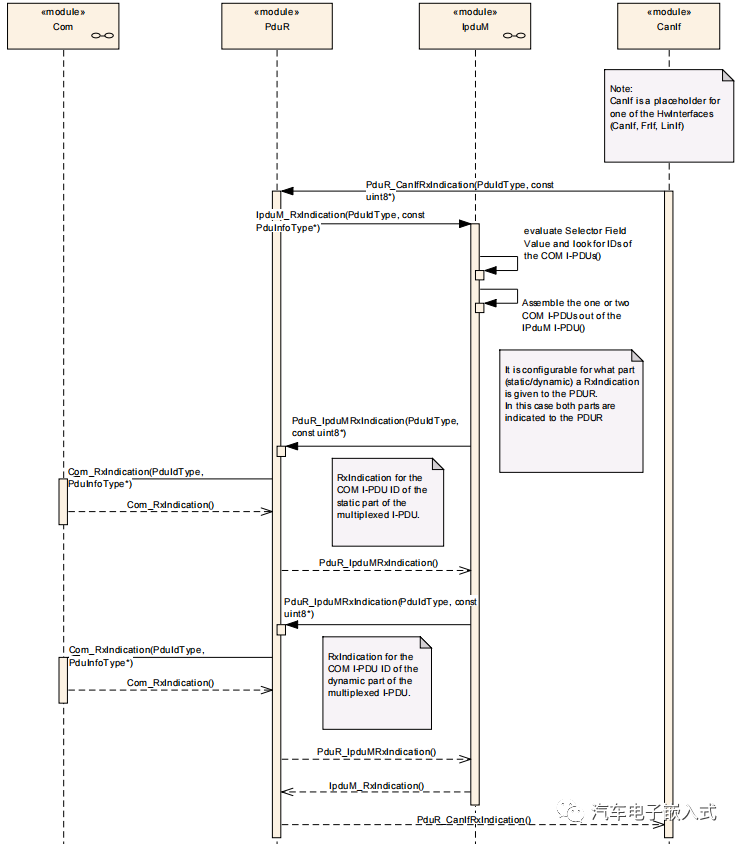

在向系统施加 2000A阶跃负载进行测试之前,必须使用仿真工具对负载进行模拟,这将有助于预测潜在的问题并及时的调整,如图5所示,仿真需要将VRM、PCB、PKG 和Die 的行为模型进行级联。

2.4.5 瞬态分析

接下来是进行瞬态仿真分析,以了解当施加2000A阶跃负载时电压和电流的变化情况。这将有助于识别 PDN 中的噪声纹波和振铃,图6展示了瞬态仿真的结果。

2.4.6 噪声分析

当添加Die行为模型时,检查在阶跃负载转换期间PDN中是否有任何不必要的噪声或尖峰,以考虑是否需要更多的电容,或者是否需要改变布局以及PCB叠构以减少环路电感和压降。

2.4.7 热分析

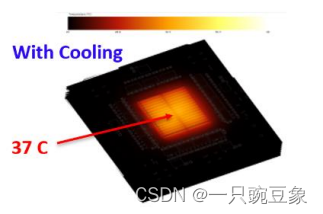

在 2000A 的稳态下工作并伴随着大的动态阶跃负载时,可以在组件中产生显著的热消耗,而热仿真可以提供早期的设计布局改进,以防止过热并确保组件的可靠性,如图7所示,根据热分析的结果,可以在模具内部添加测量点,以确保最坏情况下的温度不会超过设计规格。

2.4.8 测量设备

高质量的测量设备,包括频谱分析仪、实时示波器、网络分析仪、电流探头(包括近场探头)和高带宽电压探头。

2.4.9 小信号和大信号

这是对PDN 进行分析时,根据信号的大小和影响的分类术语:

大信号聚焦于瞬态、阶跃响应、电压跌落(电流陡升时电压下降)和峰值功率的场景;

小信号表示相对恒定的信号,并且通常在标称工作点(DC)周围有很小的变化。小信号用于表征和了解 PDN 阻抗随频率的变化规律,也可用于噪声裕度的分析。

伯德图是小信号稳态交流行为,而阶跃负载是大信号时域响应。两者都需要用于评估电源分配网络在所有工作条件下的全部性能。

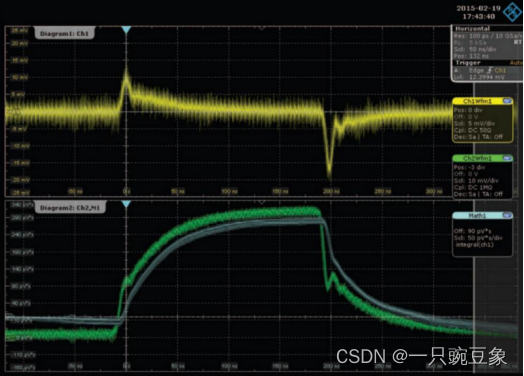

如图 8 所示,展示了小信号和大信号的测量波形。最初的0A-20A阶跃代表一个“瞬态大信号",随后的 20A-22A阶跃代表一个“交流小信号”,组合负载周期设置为1ms [6]。

2.4.10 测试方法

完成上述一系列的仿真预测后,就可以开始测试了。使用测量设备在时域和频域监测电压和电流水平,寻找任何意想不到的行为或偏离仿真的结果。由于冷却装置的结构限制,几乎不可能靠近 Die进行测试,替代的选择是使用2端口shunt-thru方法在频域测量PDN阻抗以取得测试和仿真的关联性[7]。

器件通常会提出 PDN 的纹波电压指标,时域测量也需要捕捉大信号2000A阶跃电压降和电流阶跃行为。如图9所示,位于芯片上的探测点(Interposer)可以用于测量负载端的阶跃负载变化时的压降。

在大型芯片模组的情况下,建议在几个不同的位置测量压降。到这些电源检测点的任何 PCB走线都必须以差分对(V+&V-[GND])布线,以避免噪声耦合。

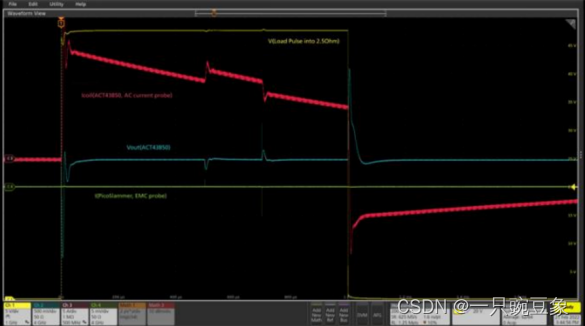

准确测量阶跃电流取决于其阶跃转换率,对于人工智能、高性能计算和超级计算机来说,是纳秒级,但对于数据中心来说,更接近微秒级。无论哪种方式,都需要高带宽的测量设备。较好的选择是使用近场探头[8],简单地将探头探测到的动态磁场积分得到电流幅值。传统电流钳探头带宽不够高,而Rogowski 线圈等专用电流探头可以进行交流电流耦合,提供电流幅值以及上升和下降时间,如图10所示[9]。

2.4.11 设计迭代和改进

电源完整性验证通常涉及基于仿真和测量的多次分析迭代,以进行必要的设计改进。这可能涉及增加电容器的数量,使用低ESR(等效串联电阻)的电容器,以及优化 PCB 布局和叠构以提高设计裕量等。

2.4.12 安全

确保系统能够承受大电流,而不会造成过热、火灾或静电损坏等安全隐患。

2.5 基于测试的元件建模

端到端电源完整性建模已经相当具有挑战性,而获得准确的供应商模型又是另外一个挑战,特别是当供应商提供的模型没有行业标准规范进行约束时[10]。但是,为了满足2000A 电源的高保真建模要求,必须对系统中使用的每个模型进行分析。

考虑到供应商的电容器模型没有统一的商业标准,设计人员需要准备好对设计中所使用的每款电容器进行测量。电容器测量必须将测量夹具去嵌,以便仅保留电容器的行为,并且,电容器模型还需要从RLC格式转换成宽带SPICE模型,以满足瞬态时域仿真所需的带宽。

如文献[11]中所述,电源不是简单的串联电阻和电感,负载也不是静态电阻。这意味着模拟端到端 PDN 系统必须包括开关电源控制回路、千兆开关数字负载以及滤波和去耦组件的分布式 PCB 网络。Sandler状态空间平均模型(SSAM)使用控制环理论状态空间方程来创建开关电源(SMPS)的行为模型,并支持快速仿真。先前发表的SSAM[12]在使用中具有很高的保真度,包括用于稳定性评估的动态控制回路行为、大信号和小信号噪声纹波以及电源抑制比(PSRR)。该模型还可以与非侵入性稳定性测量(NISM)方法一起使用,从简单的输出阻抗数据中评估控制回路的相位裕度。

首先要了解VRM的架构,才能准确地建立2000A 的VRM模型。这就需要深入了解控制回路、输出相数、补偿网络,以及确定VRM是工作在电压模式还是电流模式下。如前所述,这项工作的重点是使用五组“MPM3698 +2*MPM3699”VRM模块并联使用,以产生所需的2000A 输出电流。

参考 MPS MPM3698框图,如图11所示,可以看到有3个输出相,每一个都有一个120 nH的内部电感。MPM3699具有与MPM3698相似的架构,除了有4个输出相,每个输出相使用相同的 120 nH 电感。使用Picotest MPS EVAL PCB对MPM3698VRM进行初步验证,使用 MPS Virtual Bench Pro 4.0 来模拟该VRM模块的 PSRR 增益和相位。

为了建立SSAM 模型,首先需要通过Ri和开环增益测量来获取VRM的增益参数,然后进行 PSRR和输出阻抗的测量以获取闭环增益和PDN参数。通常,大多数VRM通过封装上的外部 Vcomp 引脚提供对控制回路的访问。但是,目前大多数供应商提供的VRM 解决方案不可能访问控制回路,以MPM3698和MPM3699为例,这种架构不仅抑制了获取这些增益参数的能力,而且使基于测量的建模变得更加困难。

然而,从供应商的数据表中获得足够的信息,如方框图、PSRR和阻抗信息,依然可以用于开发准确的SSAM 模型。但这个过程使得设计者不得不使用参数扫描优化工具,以便实现最佳的模型相关性。在这种情况下,SSAM平均模型的增益参数是使用图12所示的测量阻抗数据、图13所示MPS Virtual Bench的PSRR模拟数据获得的。

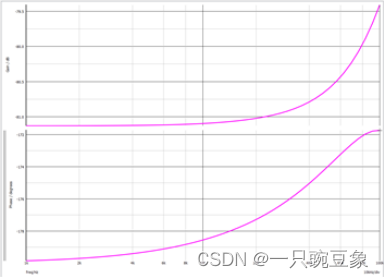

如图14所示,使用三相MPM3698VRM模块可以实现良好的测量与仿真相关性。一旦了解了MPM3698的初始架构,使用多组MPM3698和MPM3699模块扩展到2000A的解决方案就变得简单了。

2.6 对电磁 (EM) 模型的需求

电源网络是交流而非直流工作的,无论多么完善的VRM总是存在一些寄生阻抗。寄生电阻可能在微欧姆,但在2000A时,它所造成的压降是不可忽视的。如图15所示,简单的直流压降 EM 仿真可以快速确定最佳检测线位置,以补偿直流压降。此外,直流压降仿真可用于 VRM 位置、金属层厚度和所需电源接地层数量的设计权衡。

如图16所示,直流电热仿真可用于探索所需的冷却方式和温度传感的最佳位置。

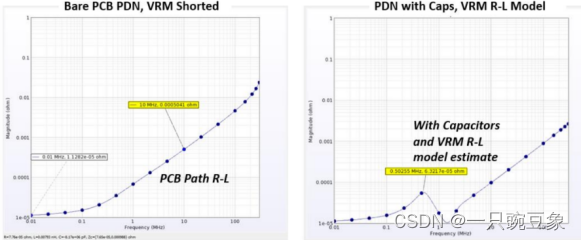

如图17所示,最重要的是在整个工作带宽范围内获得正确的交流阻抗,这意味着需要精确的电容器测量模型和完整的 PCB EM 模型来考虑电容器和PCB分布参数寄生效应。

如图18所示,将PCB EM模型和所有600多个电容器放置在底层原理图中,并生成用于仿真的电路组件,从而大大简化了端到端的仿真设置。

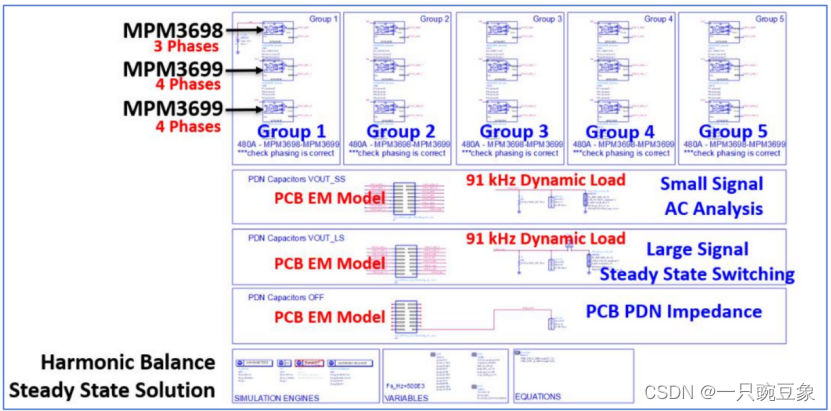

2.7 端到端的数字孪生模拟

通过精确的电容模型、EM 提取的PCB模型以及使用5组MPM3698和MPM3699 模块的2000A VRM 模型,建立了完整的系统仿真模型,如图19所示。2000AVRM模型支持负载线、小信号和大信号分析。MPM3698和MPM3699模块的SSAM子模型如图 20所示,该系统模型允许进行频域和时域分析。

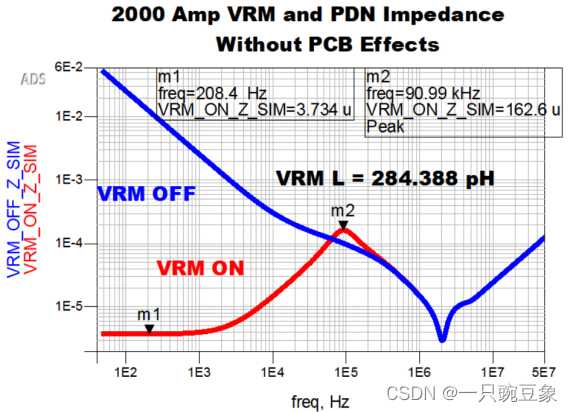

2000A VRM和PDN设计的系统阻抗如图21所示,其中描述了165Hz时的 23μΩ阻抗。为了进行比较,图22显示了没有PCB效应的2000A VRM和 PDN设计的系统阻抗。如图21中标记m2所示的阻抗峰值,而在没有PCB效应的情况下,如图22中标记m2所示,来自 VRM 控制回路的电感减少了11%,这是由于缺少PCB 电感所导致的。

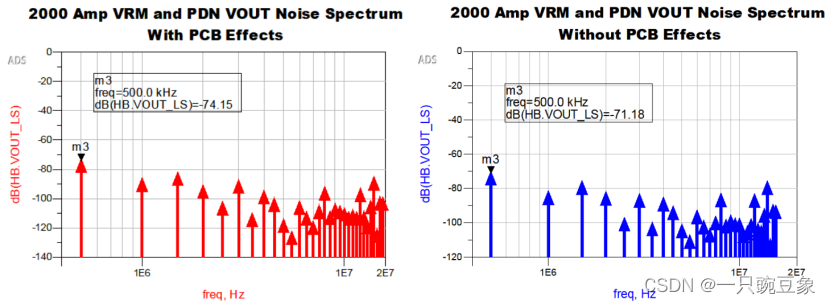

为了最终证明 PCB效应在 2000A VRM 和 PDN的设计中的重要性,图23提供了有和没有 PCB 效应的噪声频谱的比较。在VRM的开关频率下(500kHz),可以观察到PCB效应的噪声频谱高了 3dB。

最后,为了检查最坏情况下的电源纹波,将固定负载电阻替换为91kHz的动态电流负载。在500kHz DC-DC变换器开关频率和91kHz动态2000A负载这两个噪声源的已知谐波条件下,用谐波平衡法(Harmonic Balance)进行了仿真,求解了系统在频域的稳态运行。仿真运行了 55个并联 VRM SSAM 模型(如图20所示)、PCB PDN EM S参数模型和动态负载,运行时间不到5分钟。然后将频域数据转换到时域,稳态结果如图24所示。

3 测量案例研究

测量 PDN 之前,需要搞清楚动态目标阻抗,如果假设0.8V 电源网络的纹波规格为80mV,则在 2000A 阶跃负载下,目标阻抗(ZTGT)为40μΩ。

另外,已知,共模抑制比(CMRR)是成功进行微欧姆级低阻抗测量的重要指标,详细的测量设置见附录。

随着 CMRR 地环路误差校正完成,可以使用2端口 shunt-thru 以及定制的地环路隔离器进行频域阻抗测量。在这块板上进行了两种不同的测量,以突出测量的灵敏度:

如图 25 所示,在 PCB 顶部相邻的两个焊盘上进行单面测量,探测尖端之间的耦合可能对结果造成偏差影响;

如图 26所示,在PCB的两侧的同一焊盘上进行双面测量,有助于避免探头尖端之间的耦合。

如图 27 所示,为 VRM 处于 ON 和 OFF 时的 PDN 阻抗测试结果,请注意,此阻抗测量是在使用 VRM 模块默认参数配置下进行的。

VRM处于ON 状态下,两种探头测量方式在大约100kHz的范围内,测量结果是相同的。差异主要是由探头耦合造成的。默认设计满足高达约1MHz的目标阻抗要求,但VRM峰值为 15 kHz。

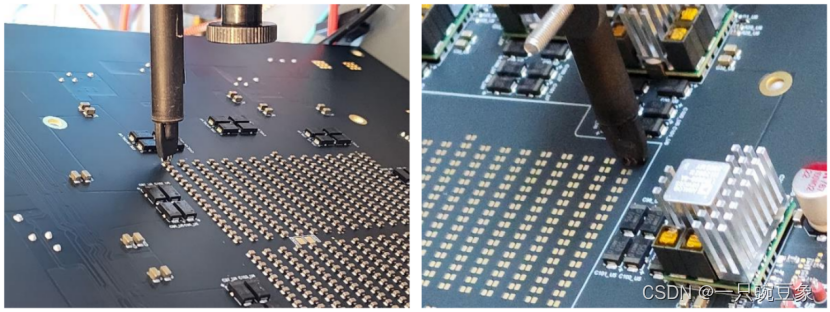

该阻抗测试验证了小信号控制回路的阻抗,但瞬态动态阻抗可以是大信号,因此也被普遍测量。采用 Picotest 超高速氮化镓步进负载连接在电源板上以模拟瞬态负载性能,该负载能够以1A 为步进增量提供0-2047A的电流变化,转换速率为几ns级。如图28 所示,PCB 芯片底部总共使用了 512 个去耦电容器。

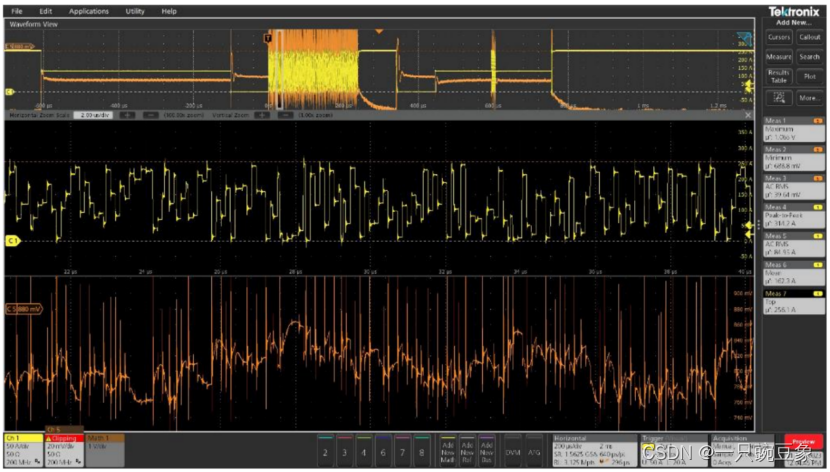

超高速负载的控制采样速率高达50 MSPS,图29演示了这种激励,屏幕上方展示了指数上升和下降、线性上升和下降、高速突发、正弦和伪随机的激励变化过程,屏幕下方的放大窗口展示了伪随机激励变化部分的负载电流和纹波电压波形。

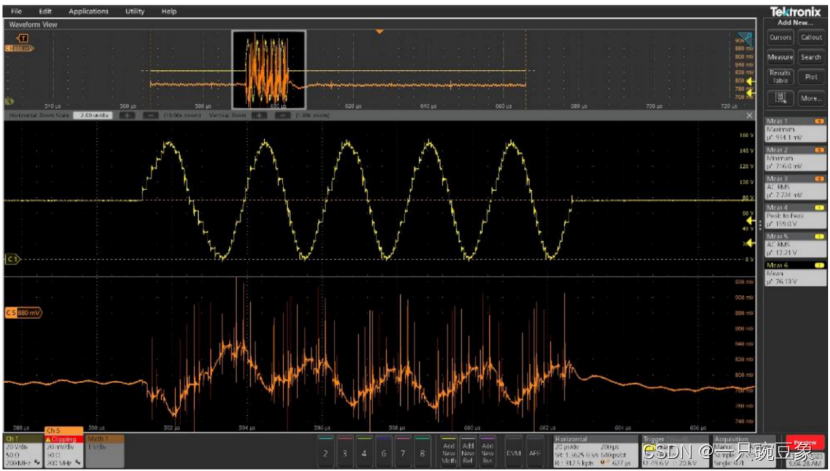

图30中的放大窗口展示了负载电压正弦激励变化和电压纹波波形。

4 结论

如今,这种高电流的PDN 设计正变得越来越普遍,而且电流还在继续增加,很有可能在几年内达到5000A。在本文中,展示了设计这种PDN网络的一些关键方面。讨论了可用的拓扑以及拓扑的影响、VRM模型对准确预测PDN阻抗的意义、PCB EM仿真的基本需求,PCB EM模拟对于电容的选择也是必不可少的,特别是选择感抗最低的高频去耦电容,还讨论了验证过程,以及为什么同时使用小信号和大信号进行评估,还验证了超高速瞬态步进负载在2000A 中的应用。

参考文献

[1] J. Lu, D. J. Perreault, D. M. Otten and K. K. Afridi, "Impedance Control Network Resonant DC–DC Converter for Wide-Range High-Efficiency Operation," in IEEE Transactions on Power Electronics, vol. 31, no. 7, pp. 5040-5056, July 2016, doi: 10.1109/TPEL.2015.2480747.

[2] T. Hudson, “Understanding LLC Operation (Part II): What to Consider in LLC Converter Design”, 2022.

[3] Y. Ni, S. Pervaiz, M. Chen and K. K. Afridi, "Energy Density Enhancement of Stacked Switched Capacitor Energy Buffers Through Capacitance Ratio Optimization," in IEEE Transactions on Power Electronics, vol. 32, no. 8, pp. 6363-6380, Aug. 2017, doi: 10.1109/TPEL.2016.2619370.

[4] “AN 136 COT Buck Loop Bandwidth and Load Step Response Comparison”, 2019, Retrieved from Monolithic Power Systems Website

[5] B. Dannan, J. Kuszewski, “What is enough? VDDQ Package Power Integrity Analysis with a DDR4 PHY”, EDICON, 2023.

[6] Evaluating Voltage Regulator Stability Using Step Load Testing”, PSD, 2022.

[7] Idan Ben Ezra, John Phillips, and Ilan Wolff, “A Step-by-Step Guide to a Novel Lab Correlated PDN Co-Simulation Methodology”, DesignCon, 2022.

[8] Fundamentals of Power Electronics: Robert Erickson: Springer.

[9] S. M. Sandler, “Faster-Switching GaN”, IEEE, 2015.

[10] W. McCaffrey, T. Huddleston, B. Dannan, and J. Kuszewski, “Who Put that Inductor in My Capacitor”, Signal Integrity Journal, 2024.

[11] S. M. Sandler, B. Dannan, H. Barnes, and C. Yots, “VRM Modeling and Stability Analysis for the Power Integrity Engineer”, DesignCon, 2023.

[12] S. M. Sandler, “Measurement Based VRM Modeling”, IEEE SPI 2017.

[13] S.M. Sandler, The Inductive Nature of Voltage Control Loops, EDN, Feb 5, 2015,

[14] S. M. Sandler, “Designing Power for Sensitive Circuits”, Eddison, 2017.

[15] S. Sandler, “How to Design for Power Integrity” Keysight sponsored YouTube Video Series.

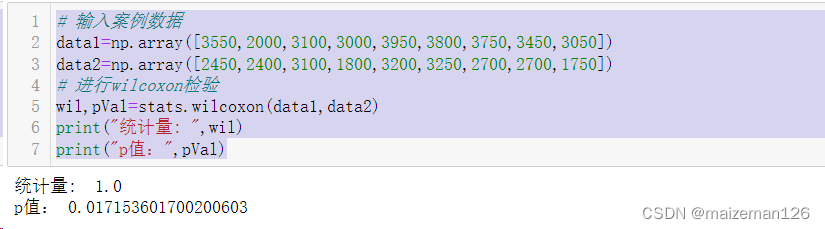

附录--测量微欧姆(μΩ)的CMRR校正

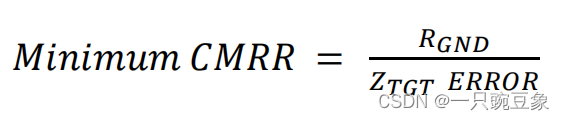

为了证明 CMRR抑制的必要性,可以首先使用如下公式计算最小所需的CMRR。其中 Probe_GND 为15 mΩ,每根电缆屏蔽电阻为30mΩ,因此,式中RGND=Probe_GND+电缆屏蔽层= 15 mΩ + 15 mΩ =30 mΩ,假设两侧电缆相等。如果期望的ZTGT_ERROR 为10%或 4μΩ,则最小 CMRR 为81 dB。

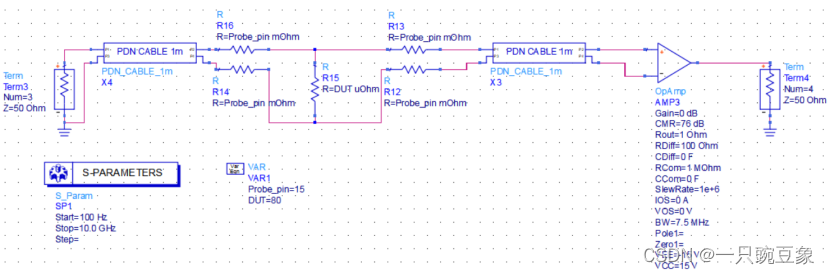

为了证明这一点,将理想的运放插入下图所示的原理图中,图中使用1米PDN电缆,并将探头接地引脚电阻设置为15mΩ。DUT设置为80μQ。CMRR从81 dB扫频到50 dB,然后移除运算放大器,以显示没有任何CMRR作为阻抗测量的一部分的误差。

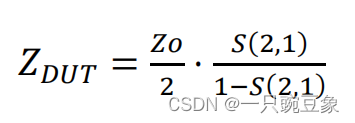

使用如下公式,绘制被测件(DUT)的2端口阻抗,并显示在图 32 中。

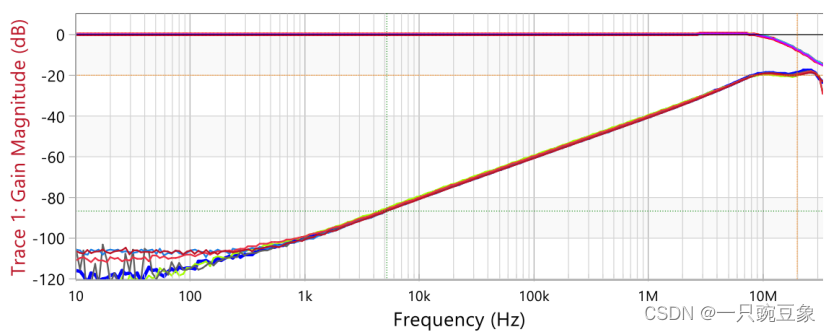

CMRR 为81 dB时,在小于1kHz的情况下,DUT 的阻抗误差为4%。而当CMRR 为 75 dB时,在小于1 kHz 时,DUT 的阻抗误差为10.5%。将CMRR 降低25 dB至50 dB,在小于1 kHz 时观察到225%的阻抗误差。最后,当移除运算放大器时,在小于1kHz时观察到 36k%的误差。这最终强调了CMRR 对精确测量这些超低目标阻抗的重要性。同样重要的是要强调,测量中的电阻可以保持恒定,但CMRR会随着频率的增加而降低,这意味着,直到一个特定的频率截止前可以有效测量一个低阻抗。

如图 33 所示,最好的 Picotest 接地隔离器远远达不到这种CMRR 要求,Picotest定制设计和制造了五个100dB CMRR 隔离器,用于此测量。5个隔离器中取增益表现最好的一个用于测量,可以观察到,带宽比其他 Picotest 地环隔离器低得多,但可以校准到约30MHz或更高,这对于低频测量来说是足够的。五个隔离器中最差的隔离器测量结果优于105dB CMRR。

本文翻译整理自DesignCon 2024中发表的“Design Simulation and Validation Challenges of a Scalable 2000 Amp Core Power Rail”。

原(英)文下载链接:

【免费】TheDesignofaScalable2000AmpCorePowerRail资源-CSDN文库