1.存储器概述

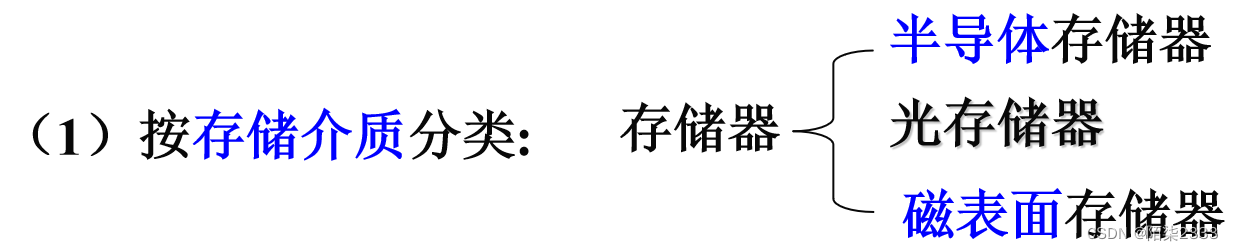

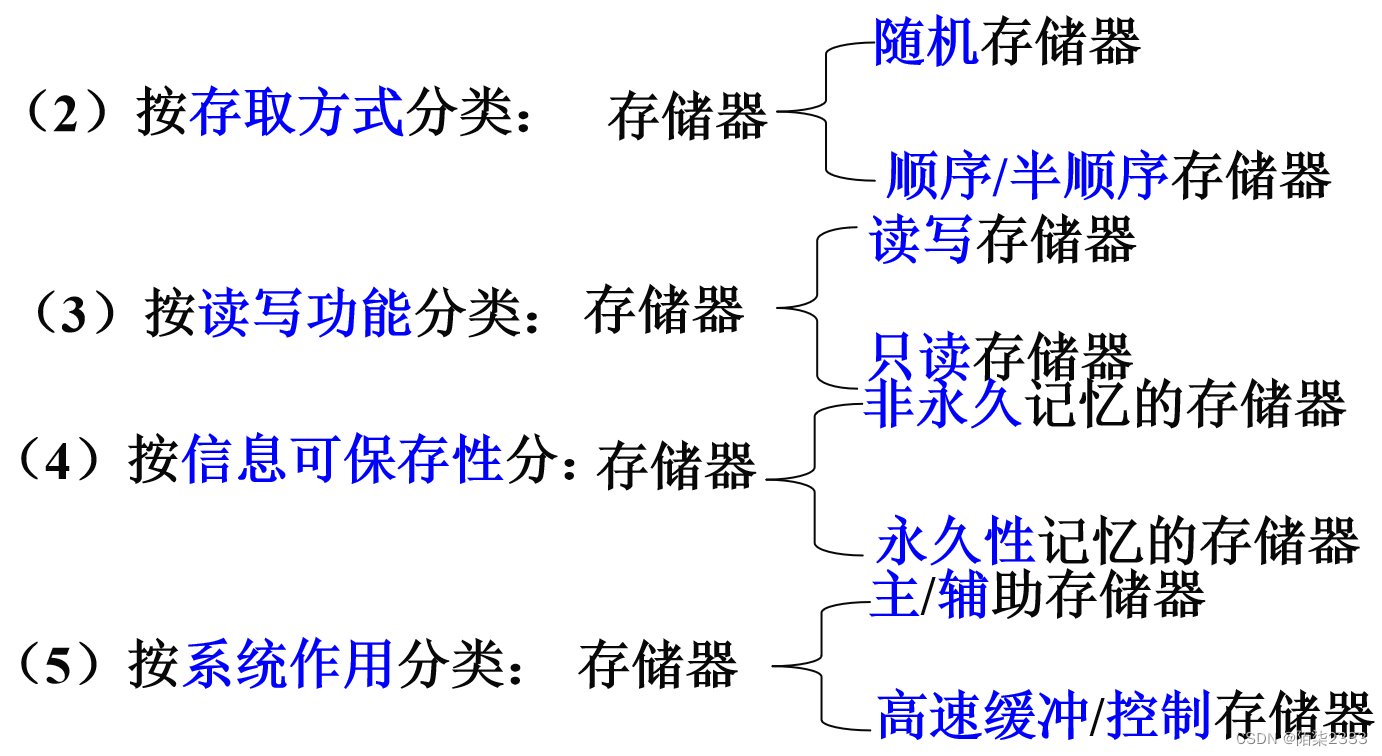

1.存储器分类

存储器:用来存储程序和数据的记忆设备。

存储介质:具有两种明显区别且稳定的物理状态,在外界的作用下,能够相互转化;一种稳定状态表示“0”,则另一种状态表示“1”。目前主要采用半导体器件和磁性材料。

存储位或存储元:最小的存储单位——一位二进制代码 存储单元:由若干个存储元组成。

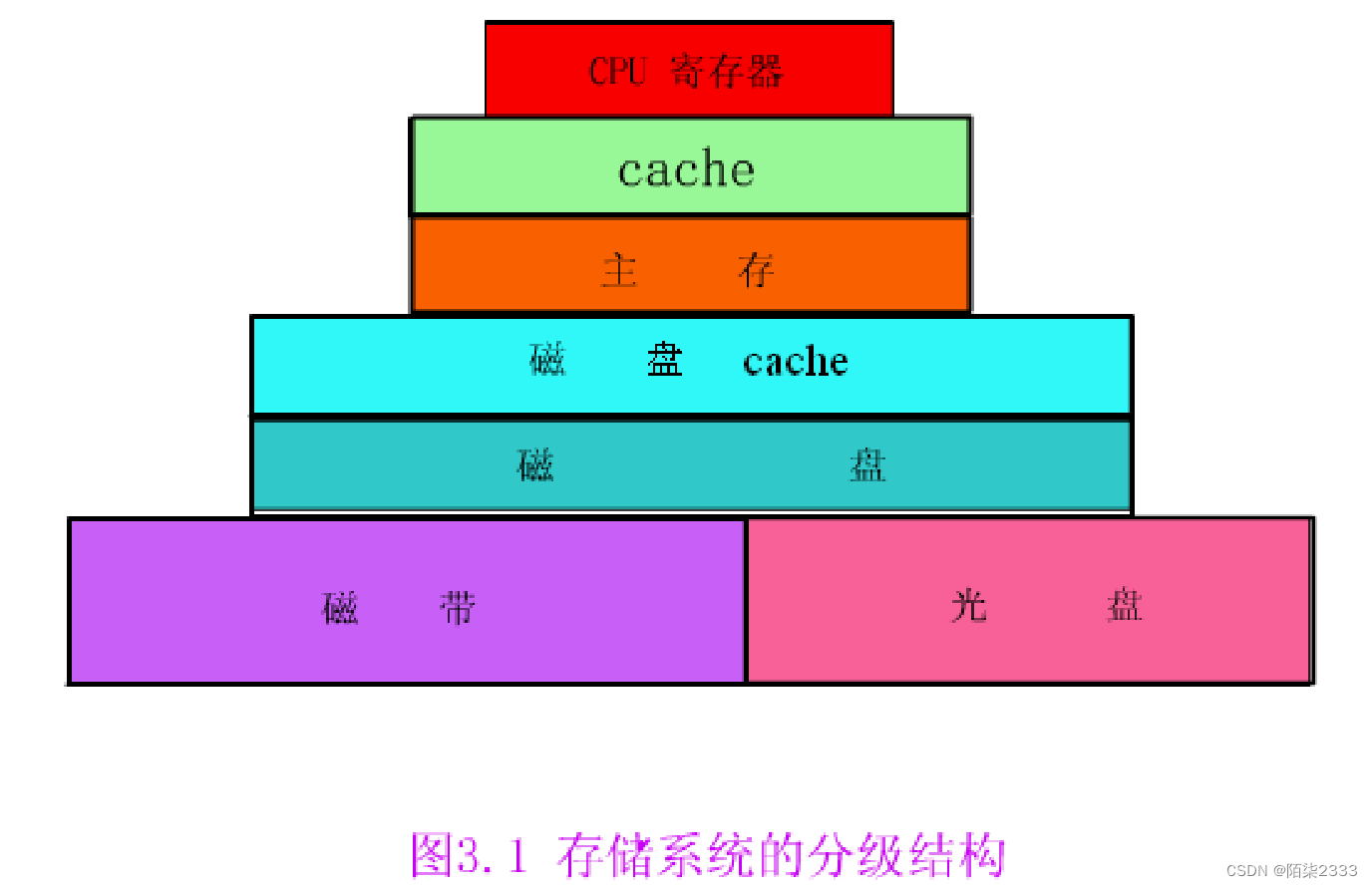

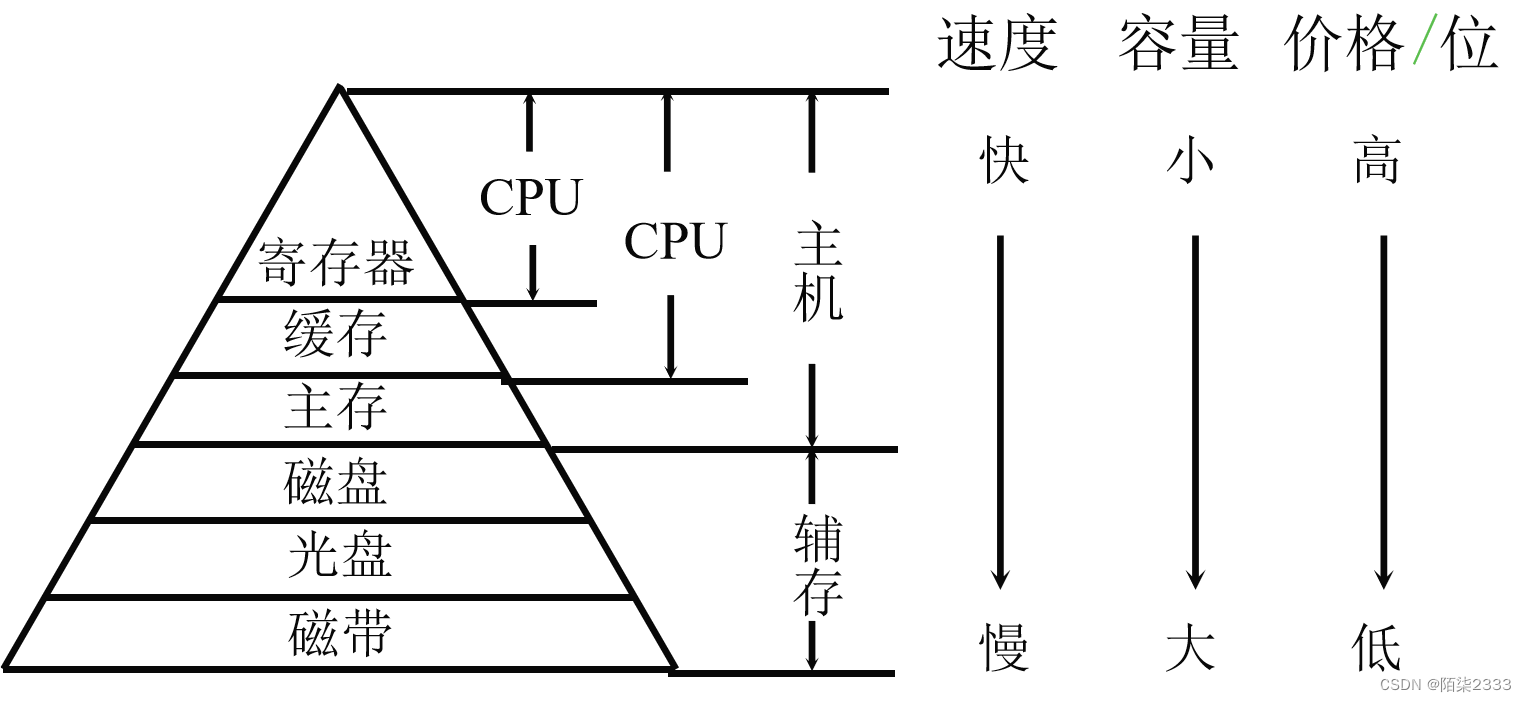

2.存储器的分级结构

对存储器要求:容量大、速度快、成本低。

多级存储器体系结构:高速缓冲存储器、主存储器和外存储器;

1.存储器三个主要特性的关系

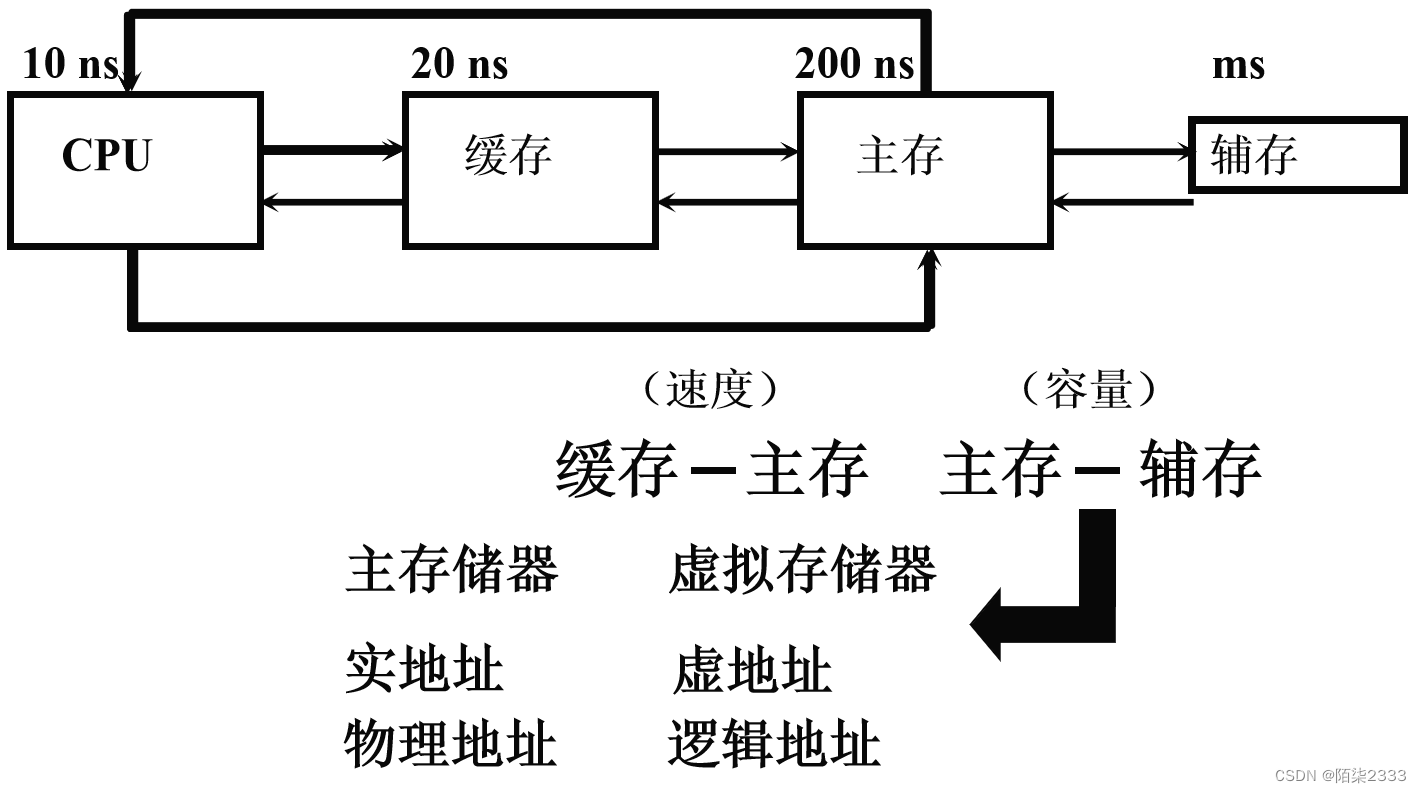

2.缓存 主存层次和主存 辅存层次

3.按CPU是否可直接访问,存储器分为

主存储器:简称“主存”,由MOS半导体存储器组成,存放处于活动状态的程序和有关数据。包括OS的常驻部分和当前在运行的程序和要处理的数据。容量在几百KB到几百MB,存取时间为几十到几百ns。

高速缓冲存储器:又称“cache”,由TTL半导体材料组成。存取时间为几ns到十几ns,容量在几KB到几百KB。存放当前正在执行程序的部分程序或数据。

外存储器:简称“外存”,大容量辅助存储器;磁表面存储器或光盘存储器;存放需联机保存但暂时不需要的程序和数据。容量从几十MB到几百GB,甚至更大。存取速度为若干ms。

其他功能的存储器:如微程序控制的控存、在显示和印刷输出设备中的字库和数据缓冲存储器。

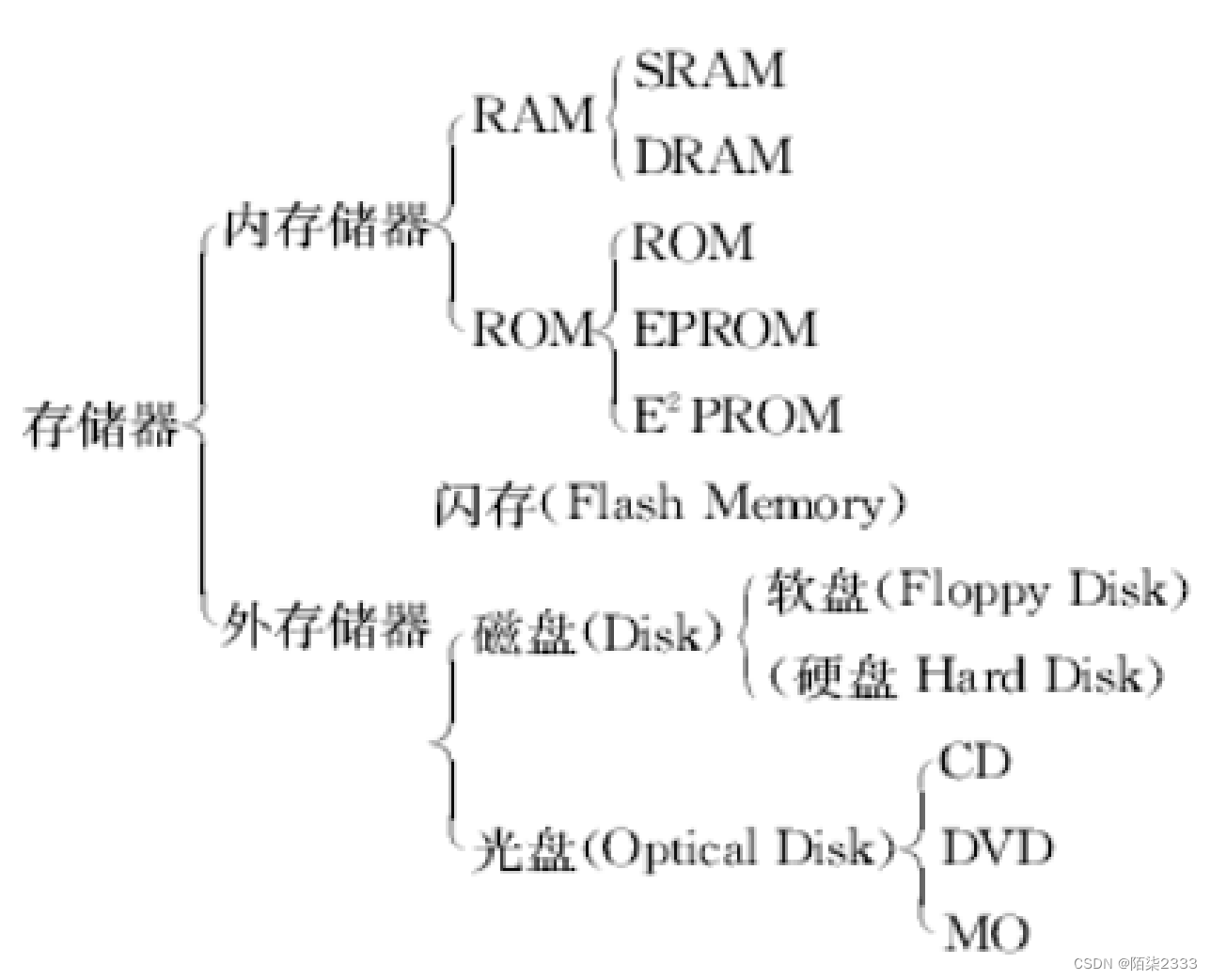

4.半导体存储器分类

TTL门电路(Transistor Transistor Logic)—由双极性晶体管组成的集成门电路,其输入级和输出极均采用了三极管,称为晶体管—晶体管逻辑门电路。

TTL存取速度快,集成度较低,功耗较大,成本较高,适于cache。

MOS电路(Metal Oxide Semiconductor)—金属性氧化物半导体电路,由MOS管(单极性场效应管)组成的集成门电路,其有三种类型:PMOS电路,NMOS电路,CMOS电路。

MOS集成度高,功耗较低,价格便宜,适于主存。

CMOS电路(Complementary Metal Oxide Semiconductor)—它是由PMOS和NMOS管组成的互补电路,其突出特点是功耗小,抗干扰能力强,稳定性好,速度快,但工艺较复杂。

3.主存储器的技术指标

3.主存储器的技术指标

主要性能指标:存储容量、存取时间、存储周期和存储器带宽。

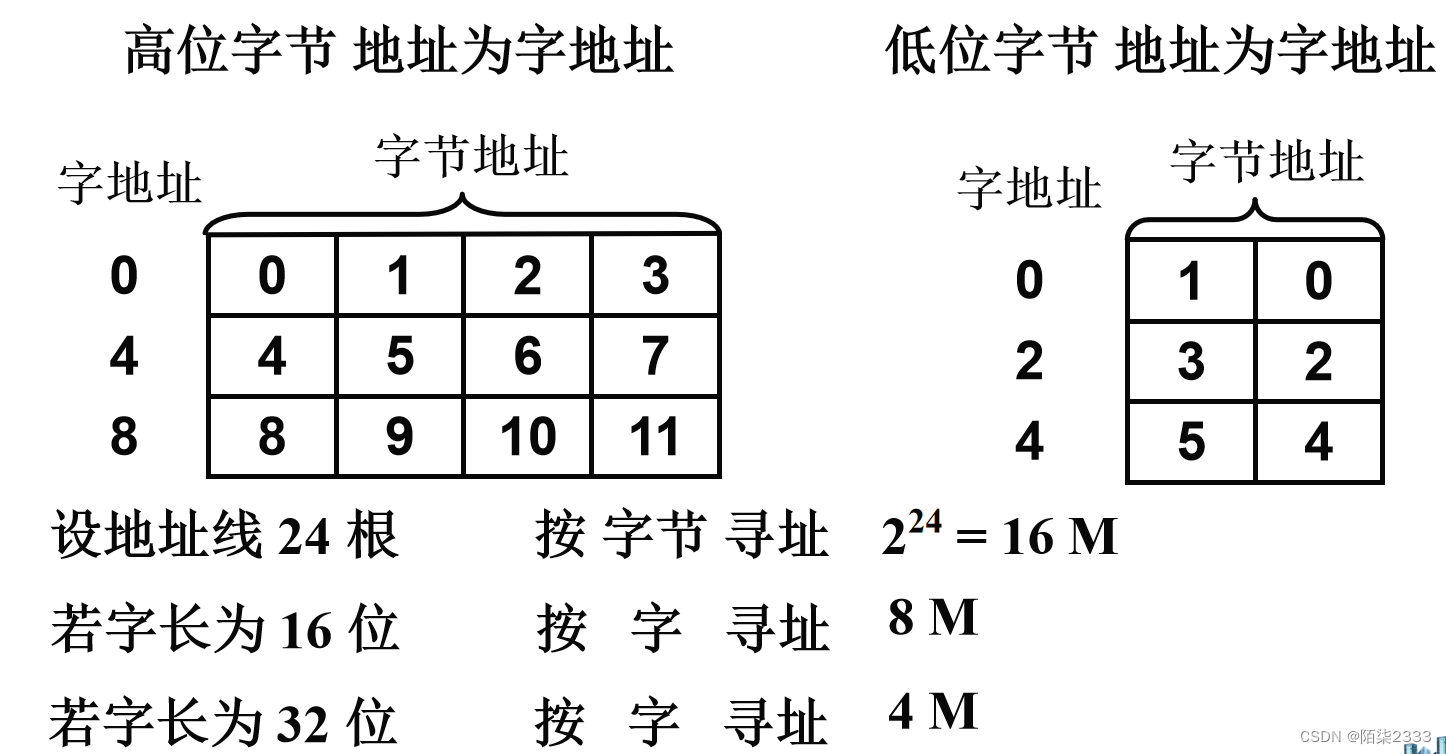

字存储单元(存放一个机器字的存储单元),相应地址为字地址

字节存储单元(存放一个字节的存储单元),相应地址为字节地址

按字寻址的计算机:计算机中可编址的最小单位是机器字

按字节寻址的计算机:计算机中可编址的最小单位是字节

一个机器字可以包含数个字节,所以一个存储单元也可包含数个能够单独编址的字节地址。

存储容量:存储器中可容纳的存储单元总数;通常用字数或字节数(B)来表示。

单位:B(Byte), KB, MB, GB, TB, PB。

存取时间:又称访问时间,从启动一次存储器操作到完成该操作所经历的时间。

存储周期:连续两次启动同一存储器操作需要的最小时间间隔。

存储周期>=存期时间

存储器带宽:单位时间存储器所存取的信息量;度量单位:位/秒、字节/秒;

可靠性:在规定的时间内,存储器无故障的概率。用平均无故障时间MTBF

功耗与集成度:耗电的多少;单个芯片存储容量;

性能/价格比:衡量存储器经济性能好坏的综合性指标。性能包括前述的各项指标。

4.主存中存储单元地址的分配

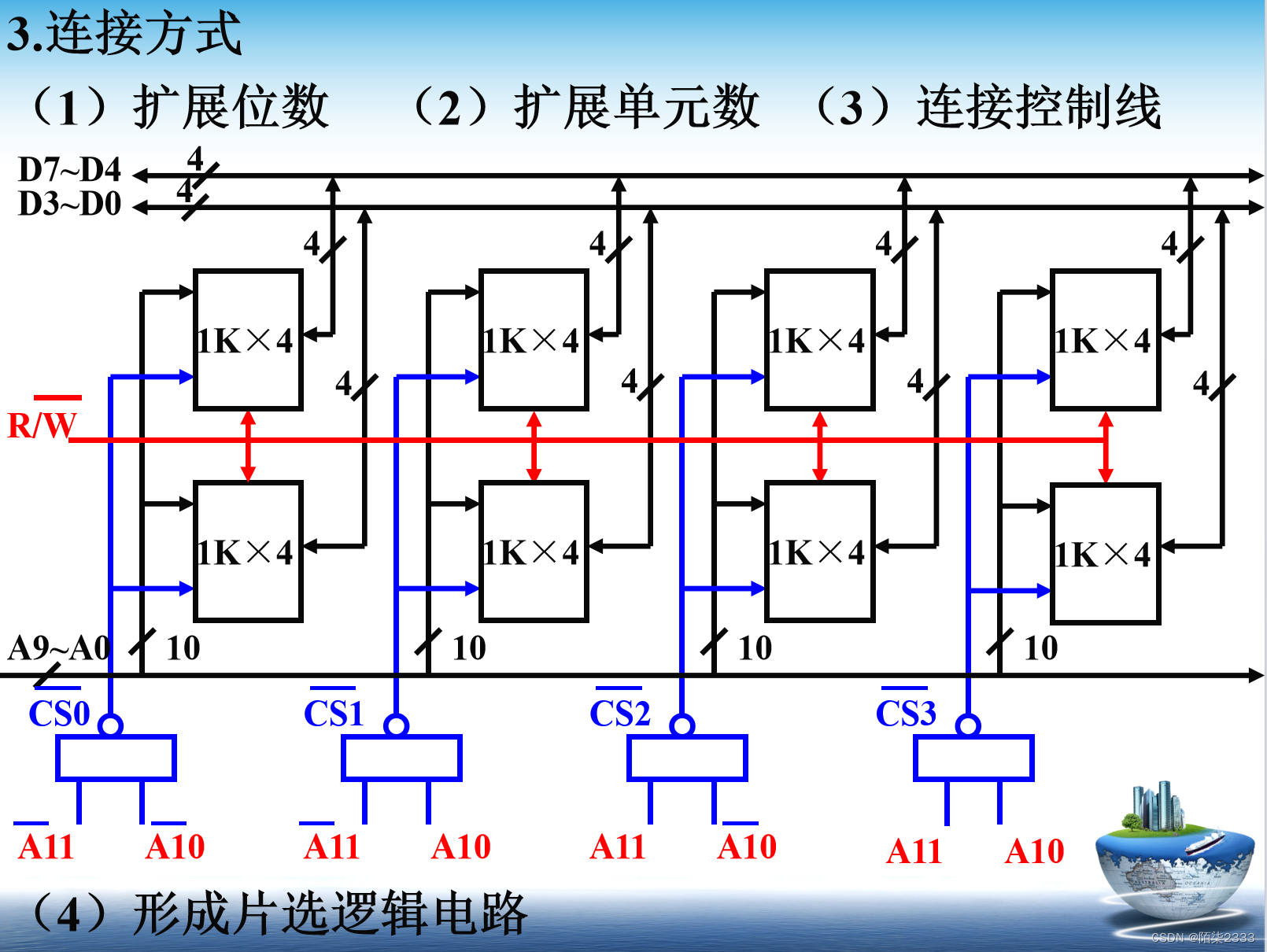

2.随机读写存储器(RAM)

RAM(Random Access Memory):存储单元的内容可随机读写。

优点:存取速度快、体积小、可靠性高、价格低廉。

缺点:断电后信息即丢失。

SRAM(静态RAM:Static RAM) :

以触发器为基本存储单元

不需要额外的刷新电路

速度快,但集成度低,功耗和价格较高

DRAM(动态RAM:Dynamic RAM):

以单个MOS管为基本存储单元

要不断进行刷新(Refresh)操作

集成度高、价格低、功耗小,但速度较SRAM慢

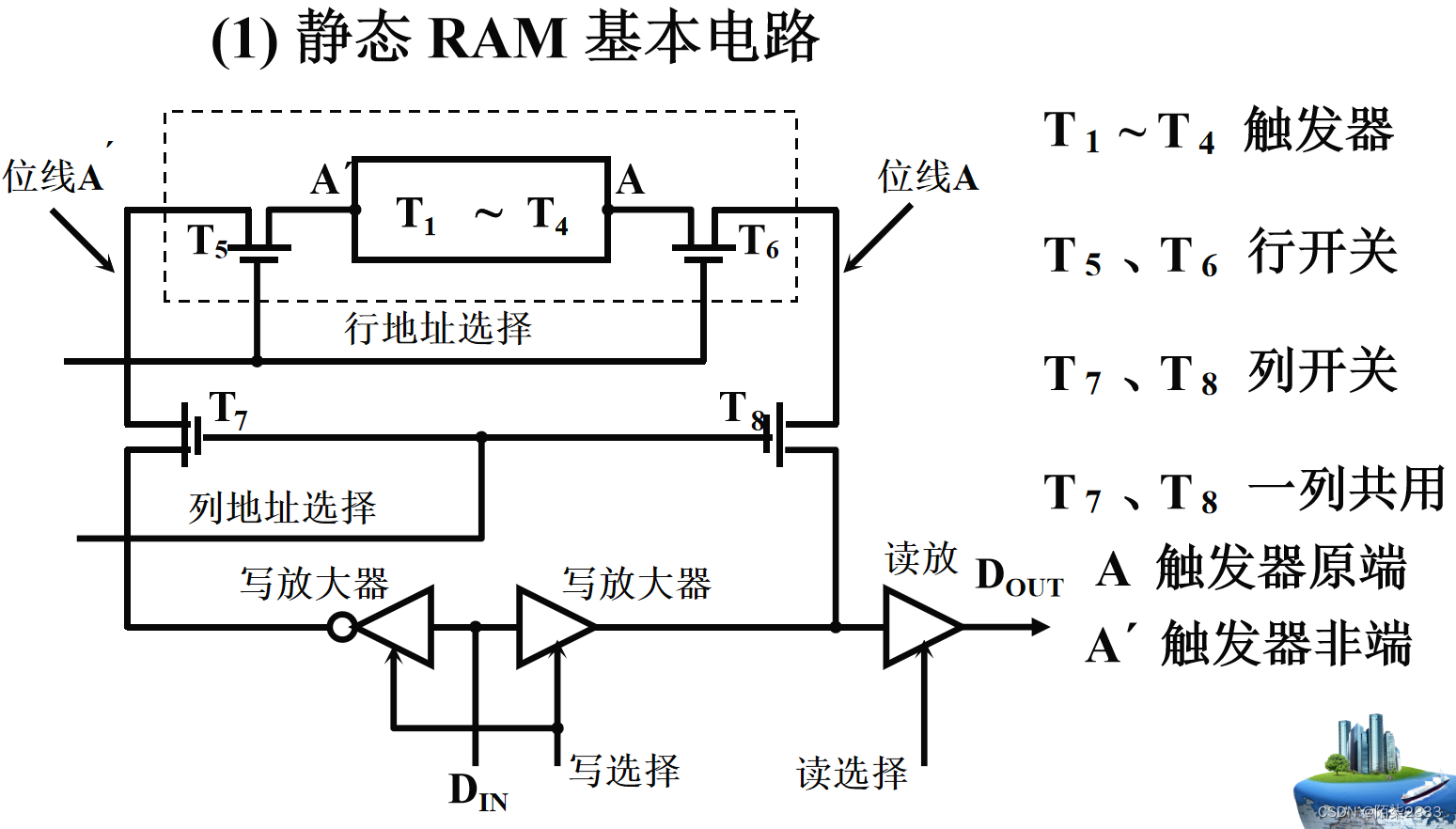

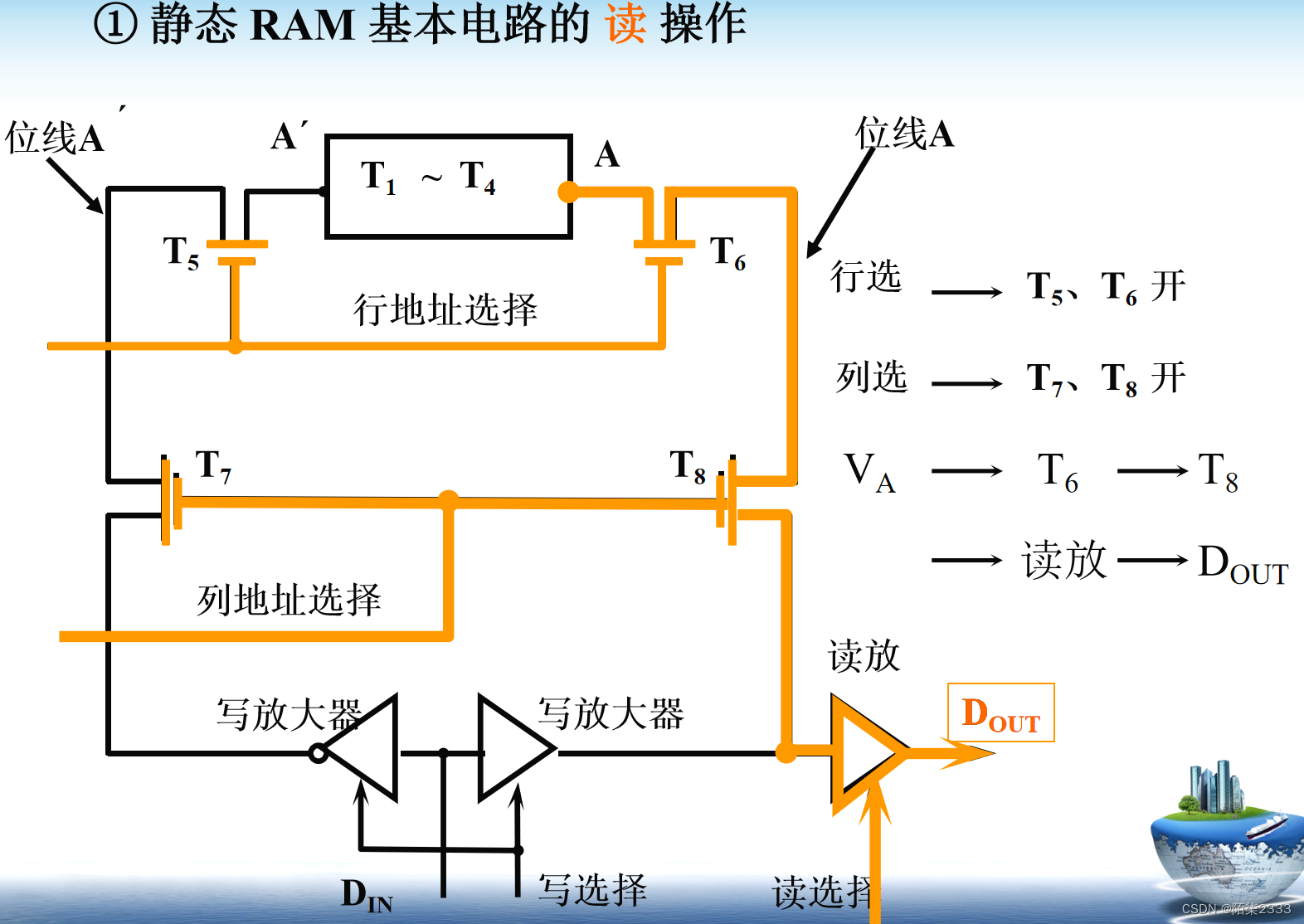

1.SRAM(Static RAM)存储器

1.基本存储元

存储器的核心和基础,用来存储一位二进制信息0或1。

以六管SRAM存储元为例解释工作原理,它是由两个MOS反相器交叉耦合而成的触发器,用来存储一位二进制代码。

2.三组信号线

地址线 ,数据线, 行线 ,列线 ,控制线。

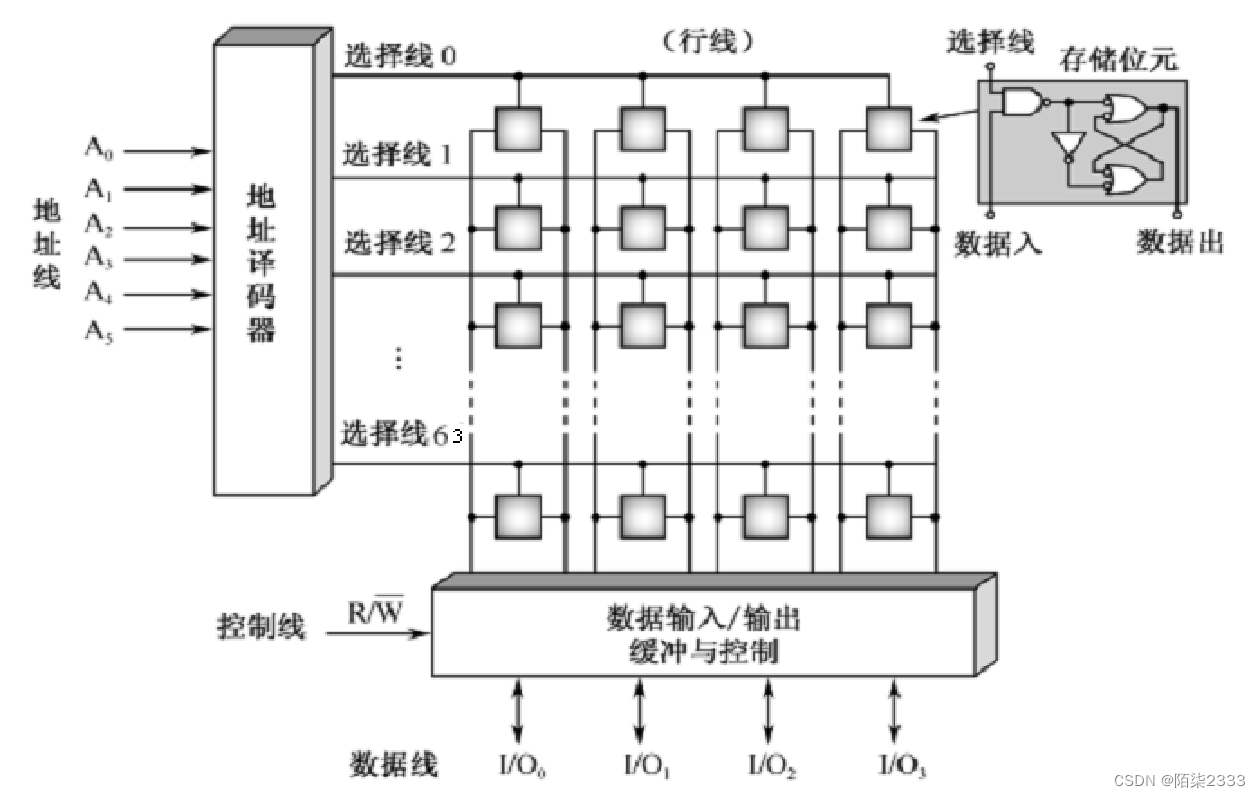

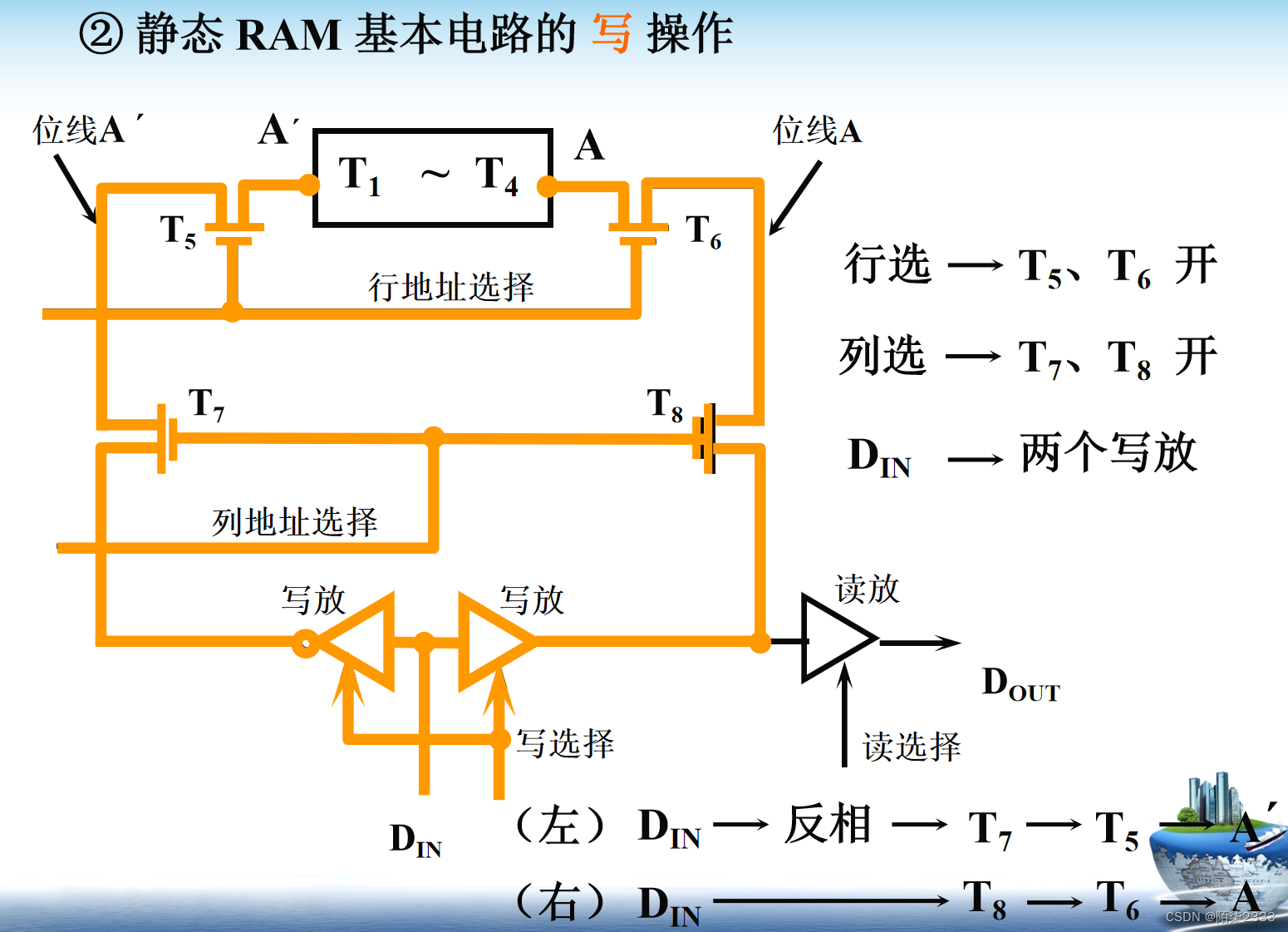

3. 静态 RAM (SRAM)

4.SRAM存储器的容量

6个开关管组成一个存储元,存储一位信息 N(=1/4/8/16/32)个存储元组成一个存储单元

存储器芯片的大量存储单元构成存储体

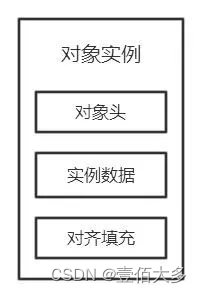

存储器芯片结构:

存储单元数×每个存储单元的数据位数=芯片的存储容量=

M=芯片地址线的个数

N=数据线的个数

例:存储结构2K×8

16K位存储容量 ,11个地址引脚 ,8个数据引脚

5.SRAM的控制信号

片选(CS*或CE*):

片选有效,才可以对芯片进行读/写操作 。无效时,数据引脚呈现高阻状态,并可降低功耗

读控制(OE*) :

芯片被选中有效,数据输出到数据引脚 。对应存储器读MEMR*

写控制(WE*) :

芯片被选中的前提下,若有效,将数据写入 。对应存储器写MEMW*

2.SRAM存储器组成

由存储体、地址译码电路、读写电路和控制电路等组成。

存储体:存储单元的集合。通常把各个字的同一位组织在一个集成片中,同一位的这些字通常排成矩阵形式。

地址译码器:把用二进制代码表示的地址转换成输出端的高电位,用来驱动相应的读写电路,以便选择所要访问的存储单元。 地址译码器的输入信息来自CPU的地址寄存器(AR)。

地址译码的两种方式:

单译码结构:地址译码器只有一个,译码器输出为字选线

双译码结构:两个地址译码器,可减少选择线条数

驱动器:一条X选择线要控制挂其上所有存储元电路,其所带的电容负载很大,为此需加驱动器。

I/O电路:处于数据总线和被选用的单元之间,用于控制被选中的单元读出或写入,并具有放大信 息作用。

片选与读/写控制电路:当需要大容量的存储器时,需把存储器片按照一定方式连接而成。在地址选择时,首先要选片,此片所连接的地址线才有效。通常用地址译码器的输出和一些控制信号来形成片选信息。

输出驱动电路:为扩展存储器容量,需将几个芯片的数据线并联使用,这同样需要驱动电路。

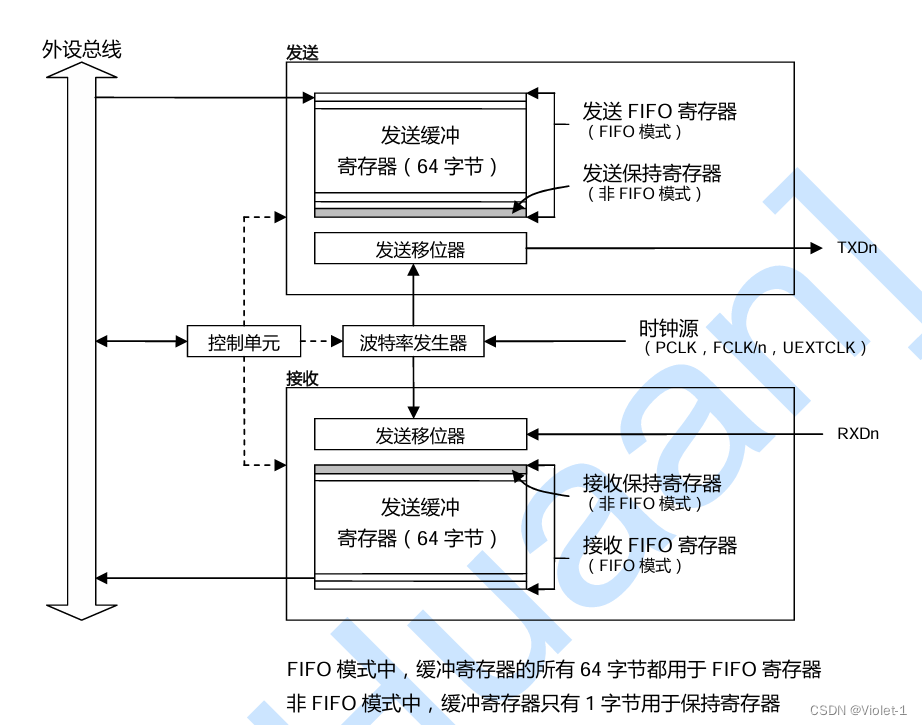

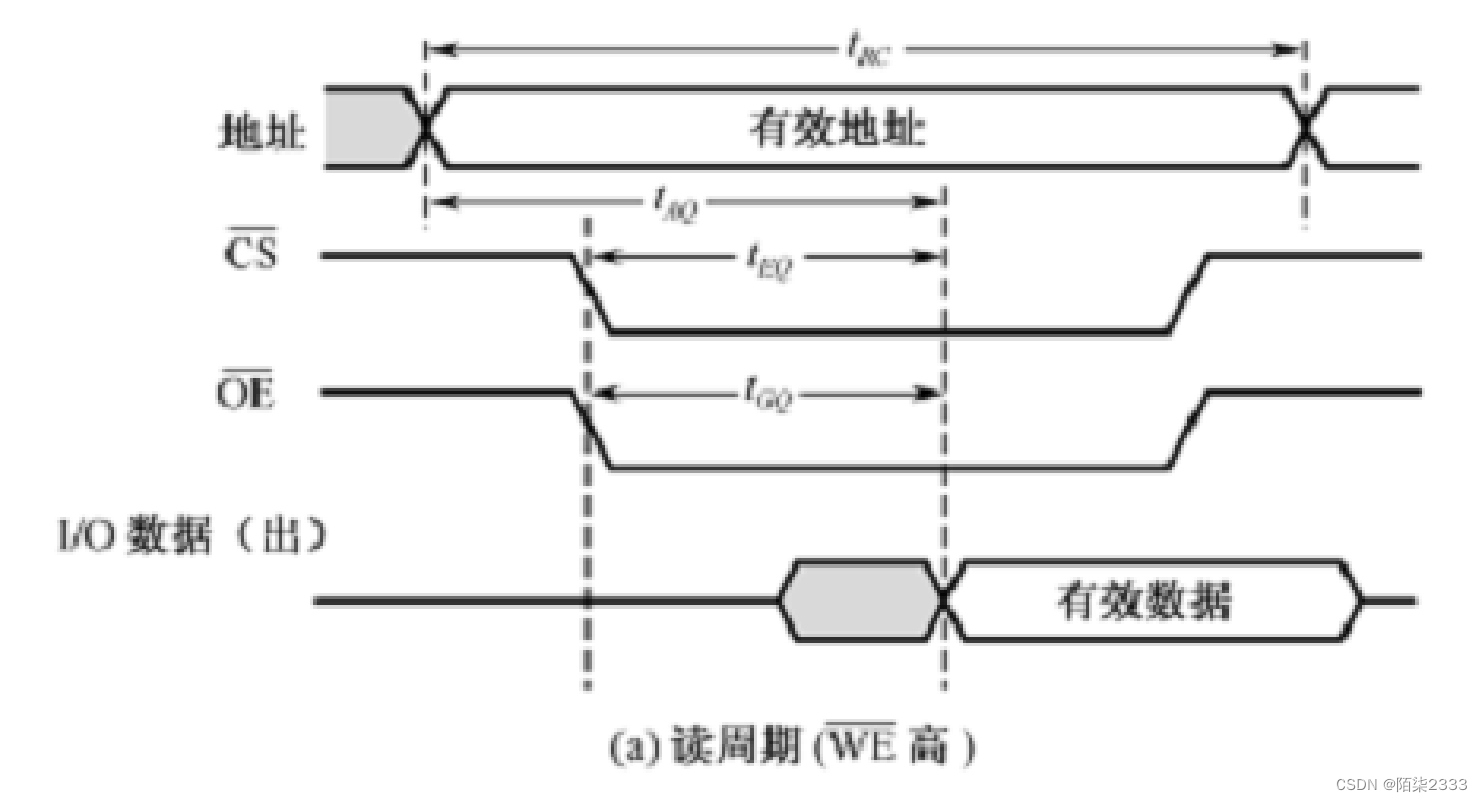

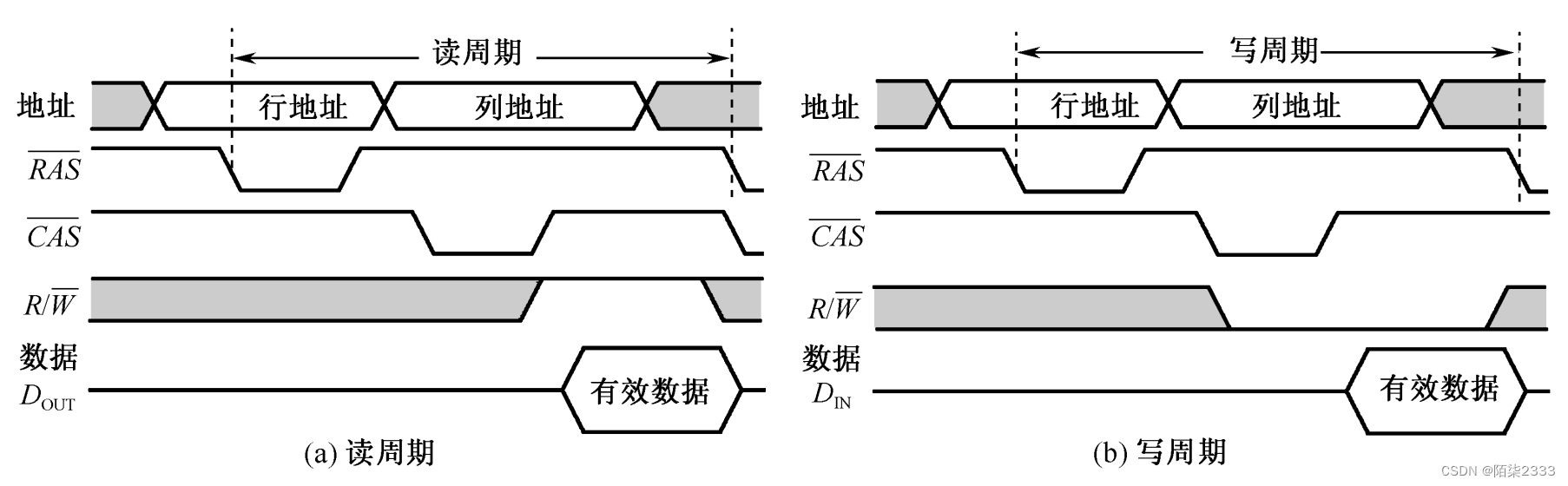

3.存储器的读写周期

读周期: 读周期与读出时间是两个不同的概念。读出时间是从给出有效地址到外部数据总线上稳定地出现所读出的数据信息所经历的时间。读周期时间则是存储片进行两次连续读操作时所必须间隔的时间,它总是大于或等于读出时间。

读周期:读出时间Taq ,读周期时间Trc

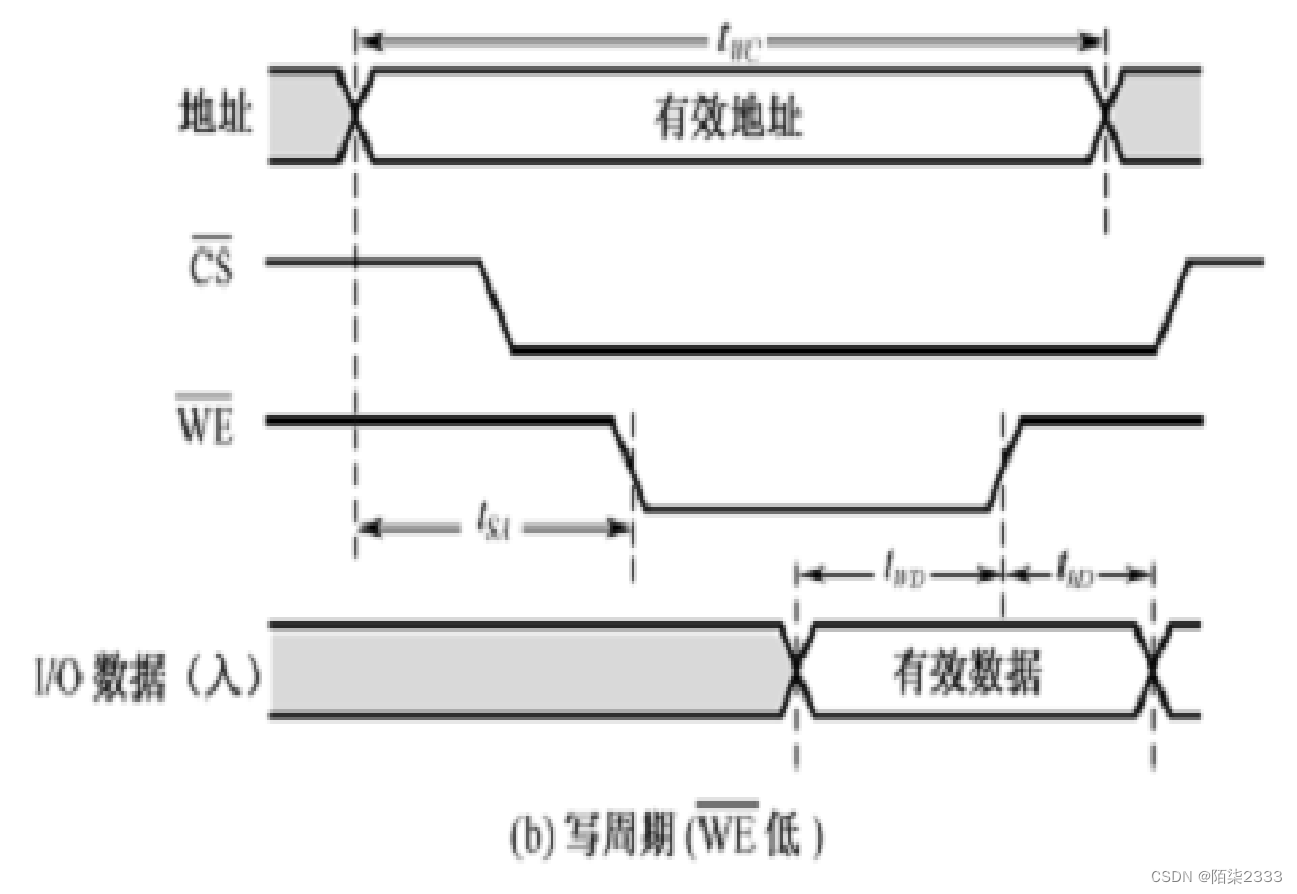

写周期:实现写操作,要求CS和WE同时有效,有效期间地址和数据信号不能变化;为了保证CS和WE变为无效前能把数据可靠的写入,数据必须提前一段时间在数据总线上稳定存在;而在WE变为高电平后再经过一段时间地址信号才允许改变。

写周期:写周期时间Twc ,写时间twd

存取周期 :读周期时间Trc=写时间twd

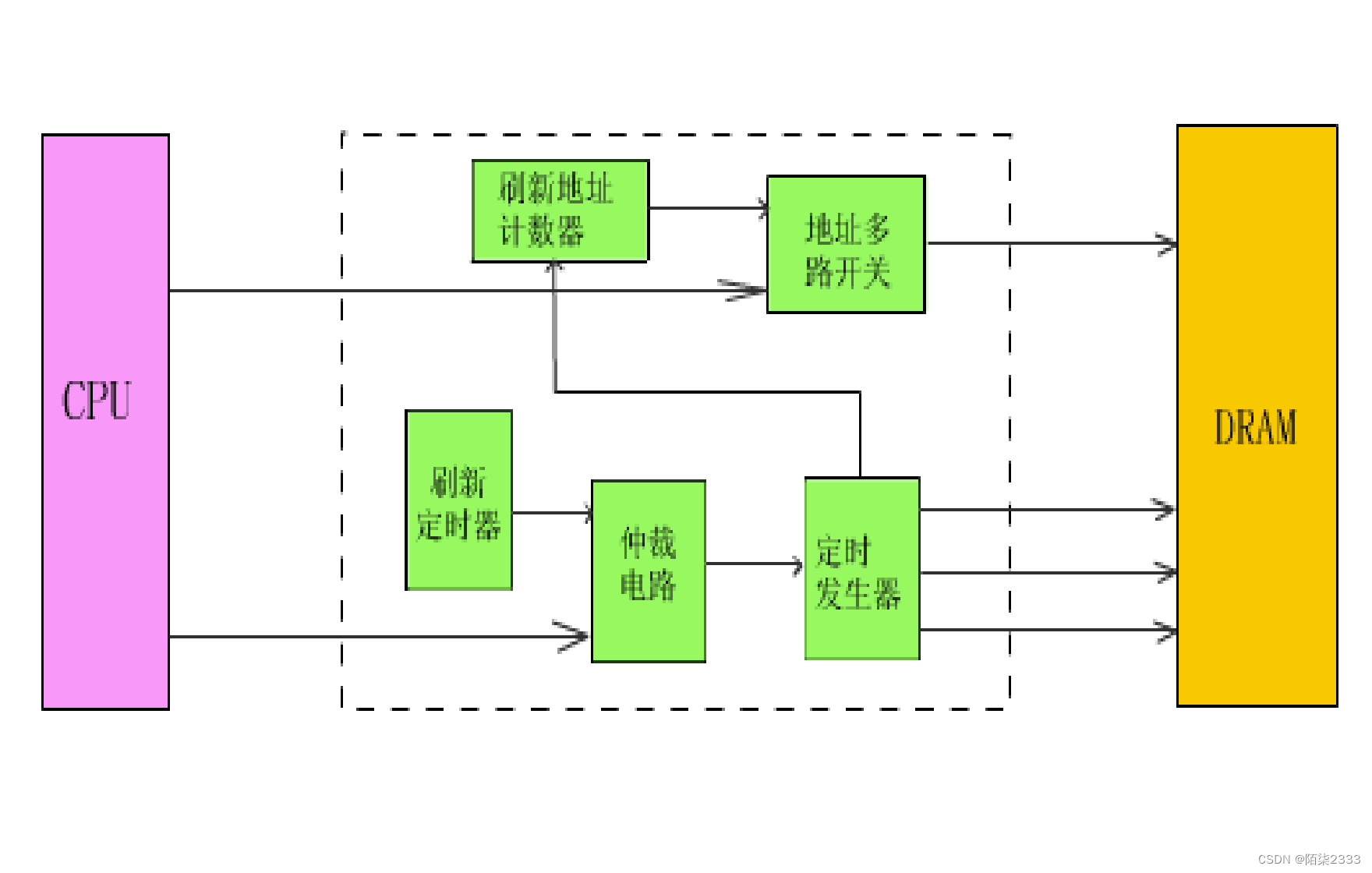

DRAM存储位元的记忆原理:

SRAM存储器的存储位元是一个触发器,它具有两个稳定的状态。而DRAM存储器的存储位元是由一个MOS晶体管和电容器组成的记忆电路

DRAM刷新需要硬件电路支持,它们集成在一个芯片上,形成DRAM控制器,是CPU和DRAM间的接口电路。

组成部分:

地址多路开关:选择分时送出行地址、列地址及刷新地址。

刷新定时器:提供刷新请求。

刷新地址计数器:采用RAS刷新时,需要刷新地址计数器。

仲裁电路:读写请求和刷新请求同时产生时,裁决谁优先。

定时发生器:向DRAM提供RAS、CAS及WE,实现读写和刷新操作。

读/写周期 :读周期、写周期的定义是从行选通信号RAS下降沿开始,到下一个RAS信号的下降沿为止的时间,也就是连续两个读周期的时间间隔。通常为控制方便,读周期和写周期时间相等。

DRAM的刷新:

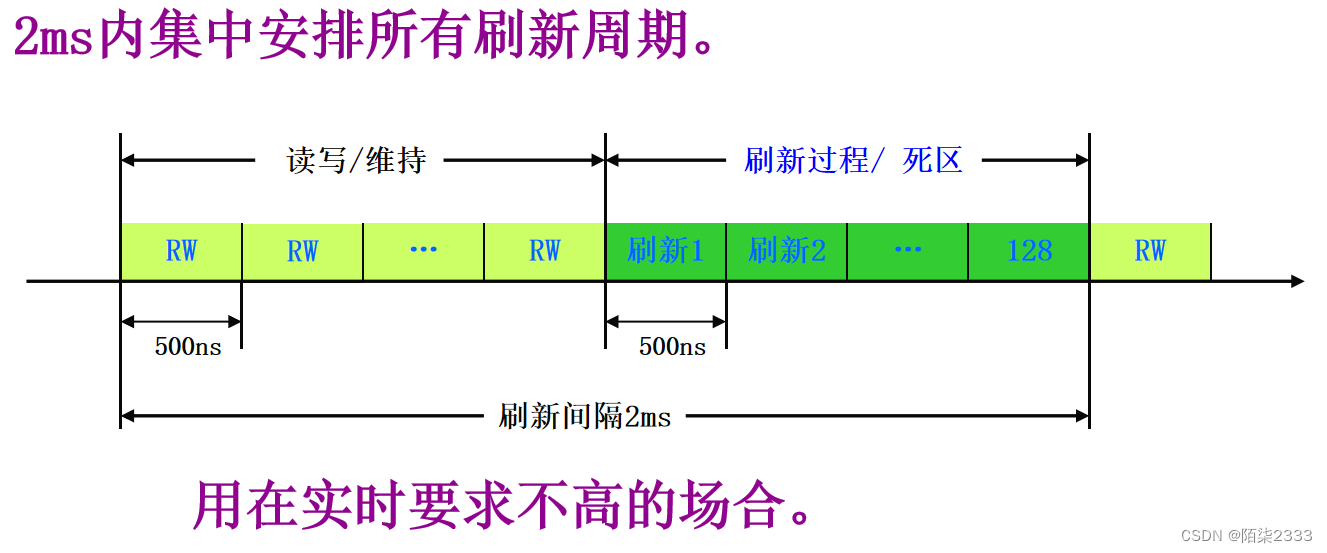

刷新周期:从上一次对整个存储器刷新结束到下一次对整个存储器全部刷新一遍为止,这一段时间间隔称为集中式或分散式。

集中刷新方式:

把刷新间隔分为两部分,前一部分进行读/写周期或维持周期,后一部分只进行刷新操作。因为刷新时期不能进行读写操作,称为死时间。本方式适用于高速存储器。

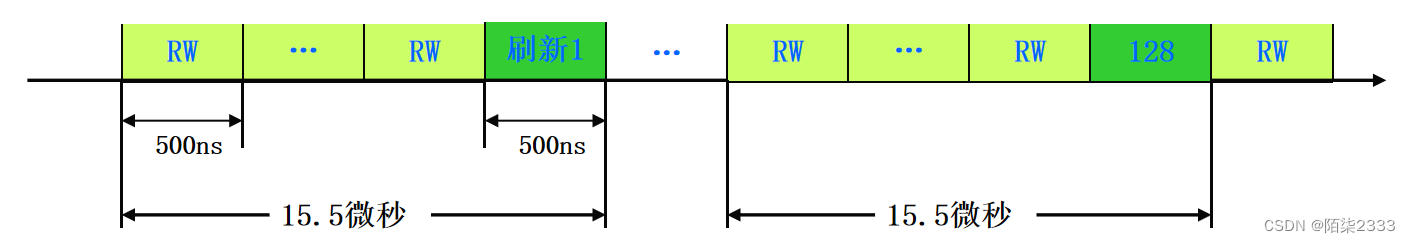

分散刷新方式:

各刷新周期分散安排在2ms内。每隔一段时间刷新一行。用在大多数计算机中。

每隔15.5微秒提一次刷新请求,刷新一行;2毫秒内刷新完所有行

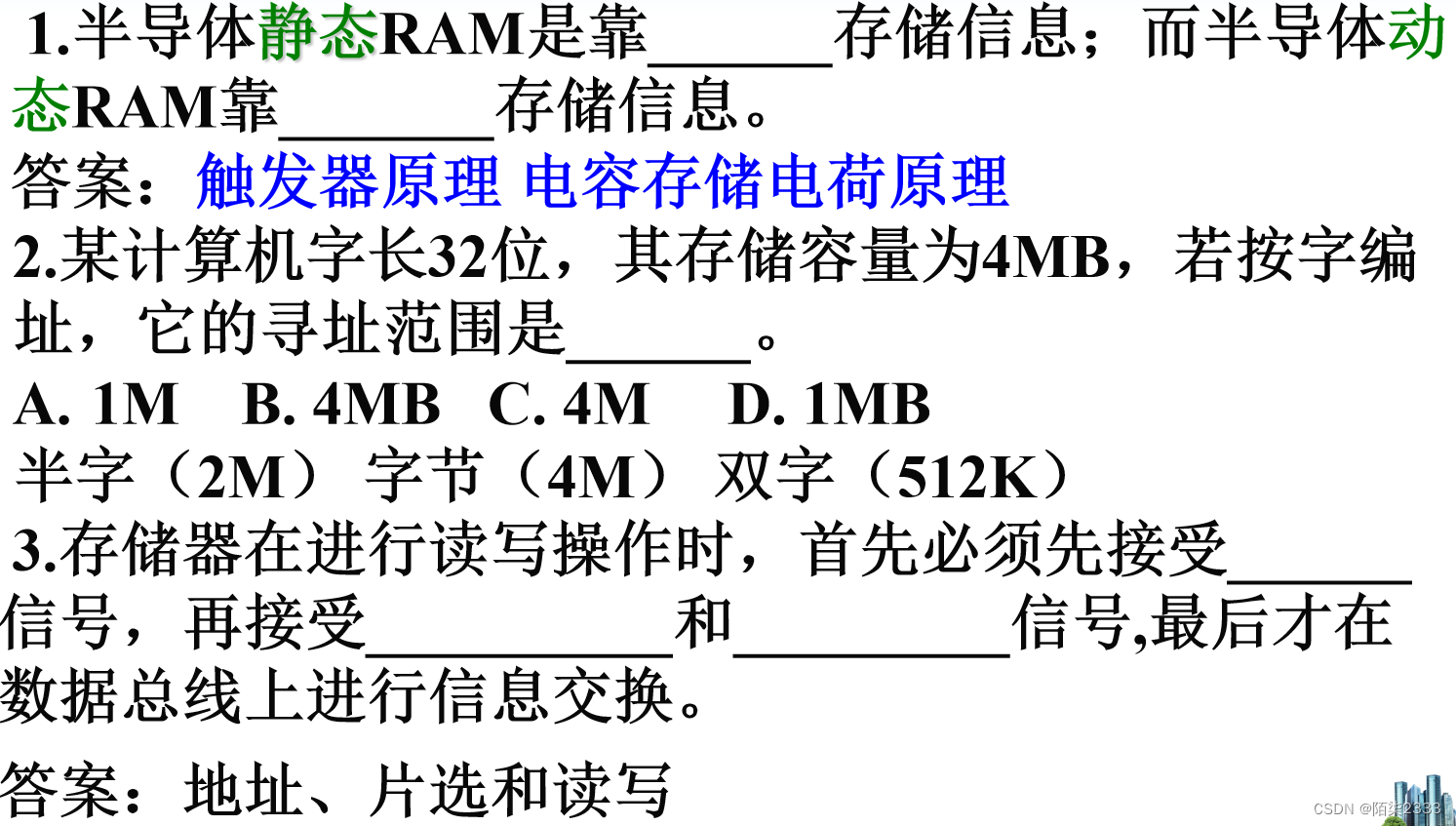

4.存储器容量的扩充

二者之间传递的信息有:地址、数据、控制信息。

存储容量扩充的方法:

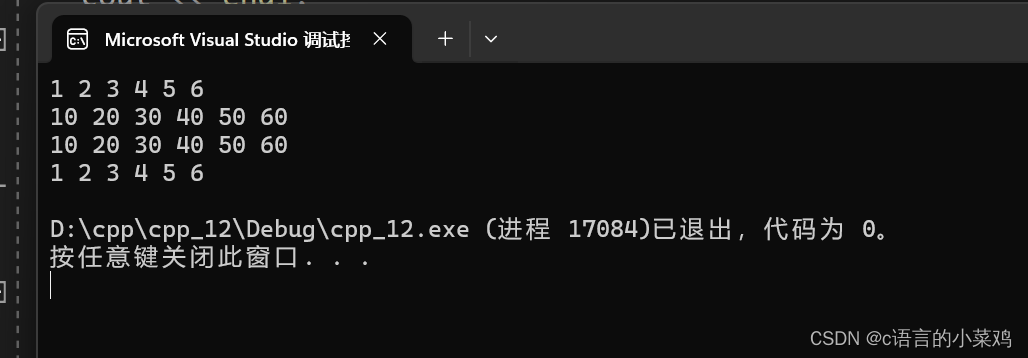

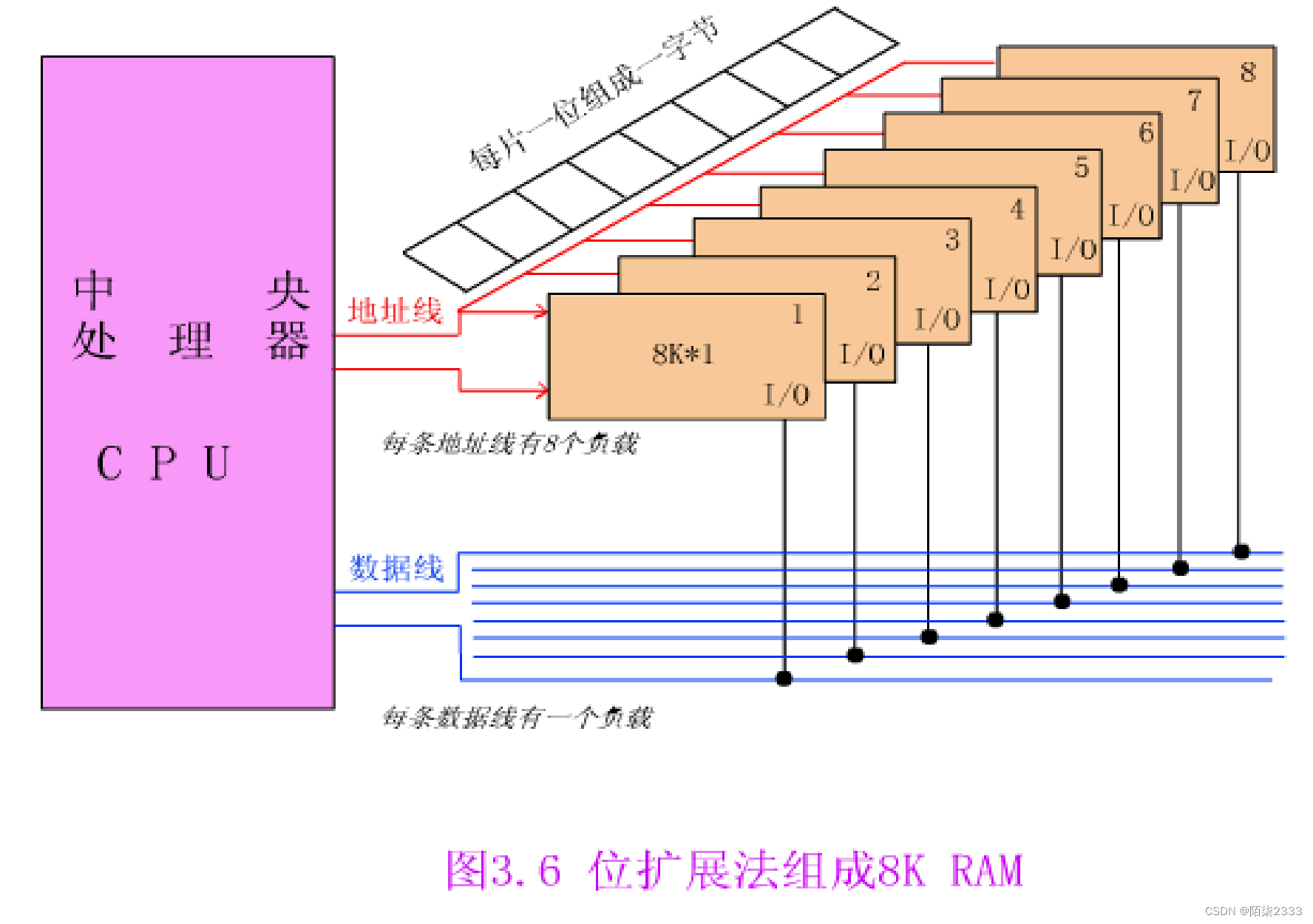

位扩展法:只加大字长,而存储器的字数与存储器芯片字数一致,即字变长,字数不变。数据线条数增加,地址线条数不变。

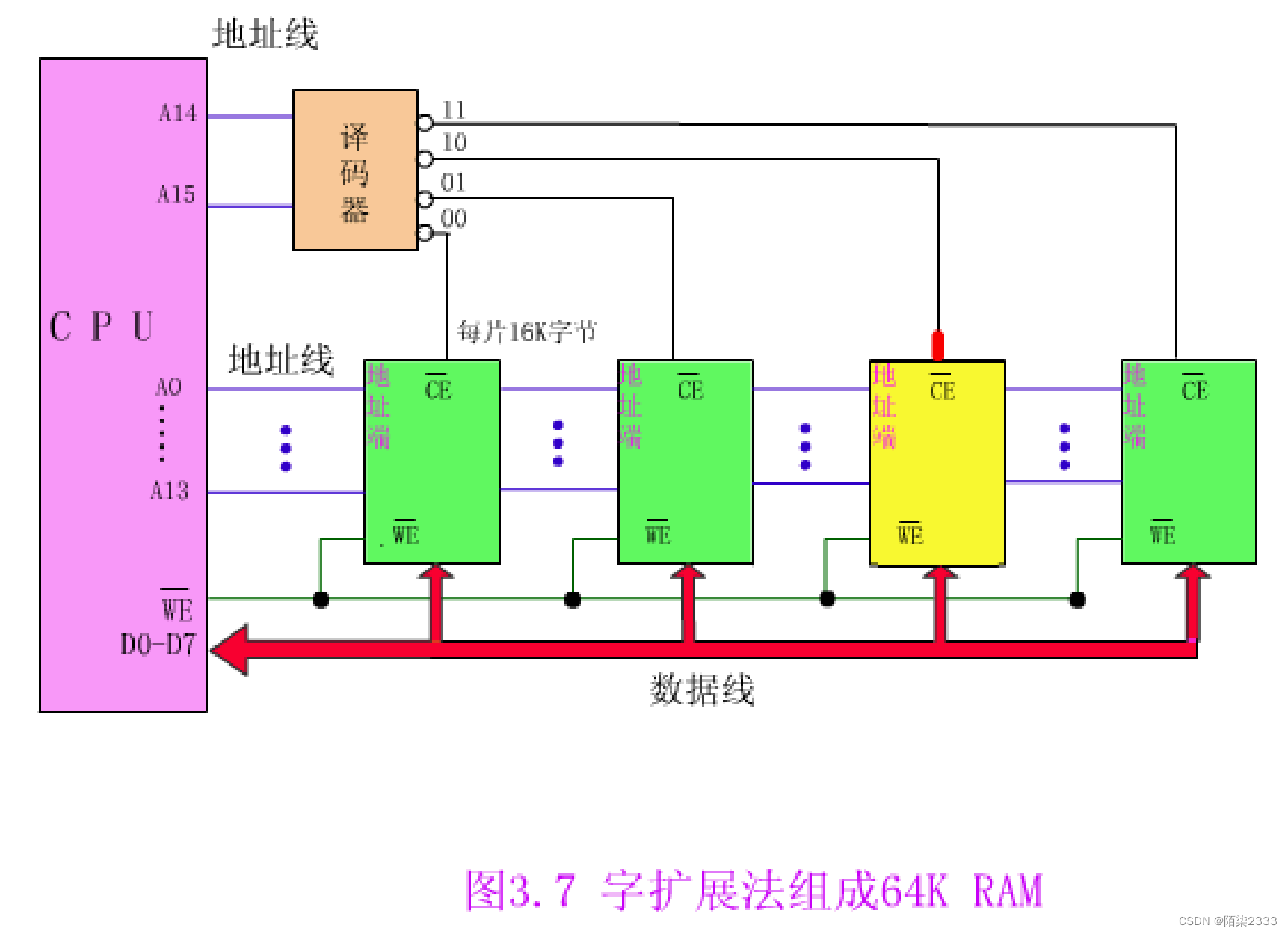

字扩展法:字数变多,字长不变,地址线增加,数据线不变; 芯片的地址线、数据线、读写控制线并联,由片选信号区分各片地址。

字位同时扩展法:需要容量M×N存储器,使用的芯片为 l ×k,则需要芯片个数为(M/l)×(N/k)

为位扩展法:

字扩展法:

字位同时扩展法:既增加存储单元的数量,也加长各单元的位数

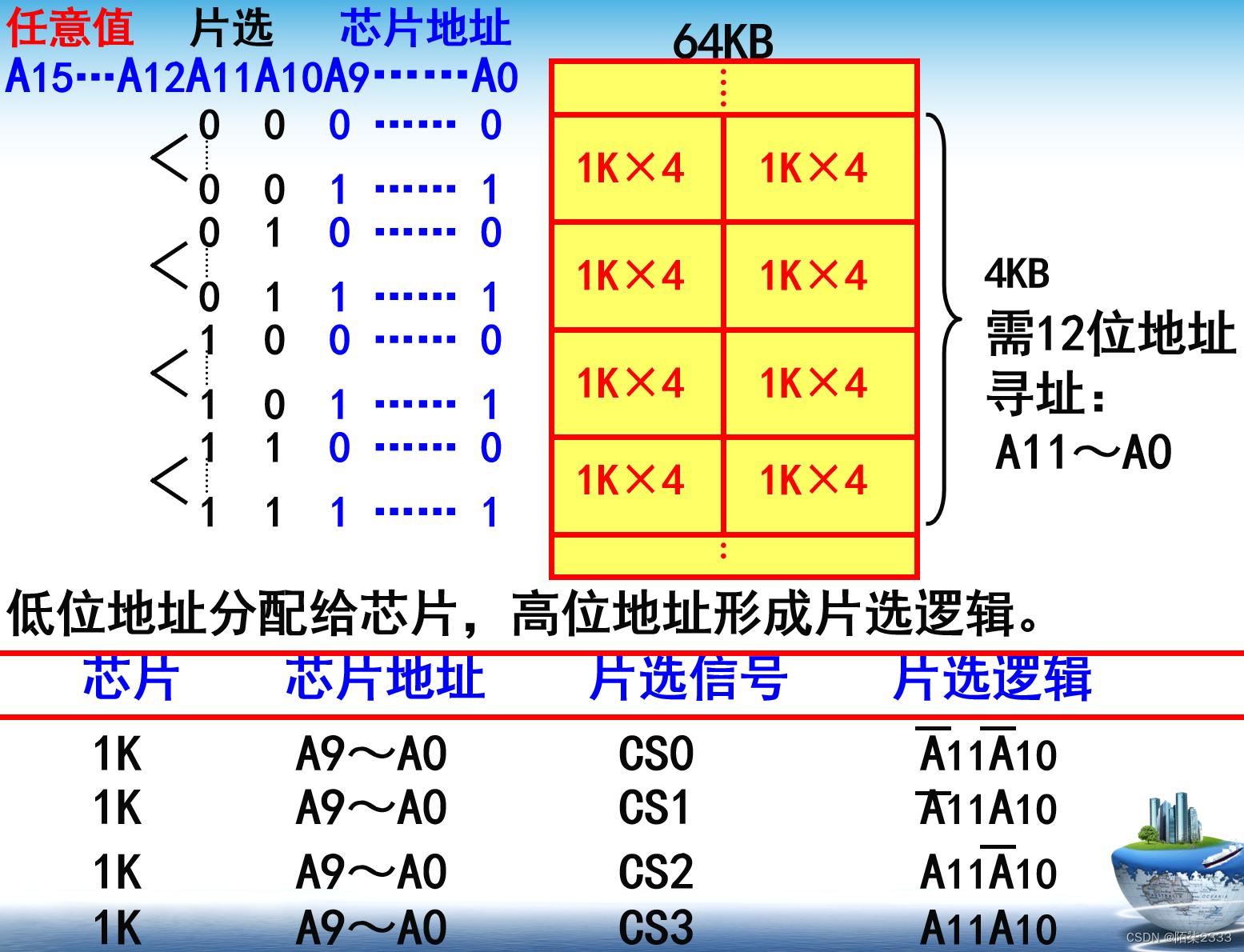

字位同时扩展:2114存储芯片1K×4扩展成2K×8存储器

存储器系统的存储容量: M×N位

使用芯片的存储容量:L×K位(L≤M,K≤N)

需要存储器芯片个数:(M×N)/(L×K)

例题:

1.利用2K×4位的存储芯片,组成16K×8位的存储器,共需要多少块芯片?

(16K×8)/(2K×4)=8×2=16

即:共需16块芯片。(既需要位扩展,又需要字扩展)

2.利用1K×4位的存储芯片,组成2K×8位的存储器,共需要芯片数:

(2K×8)/(1K×4)= 2×2=4

即:共需4块芯片。

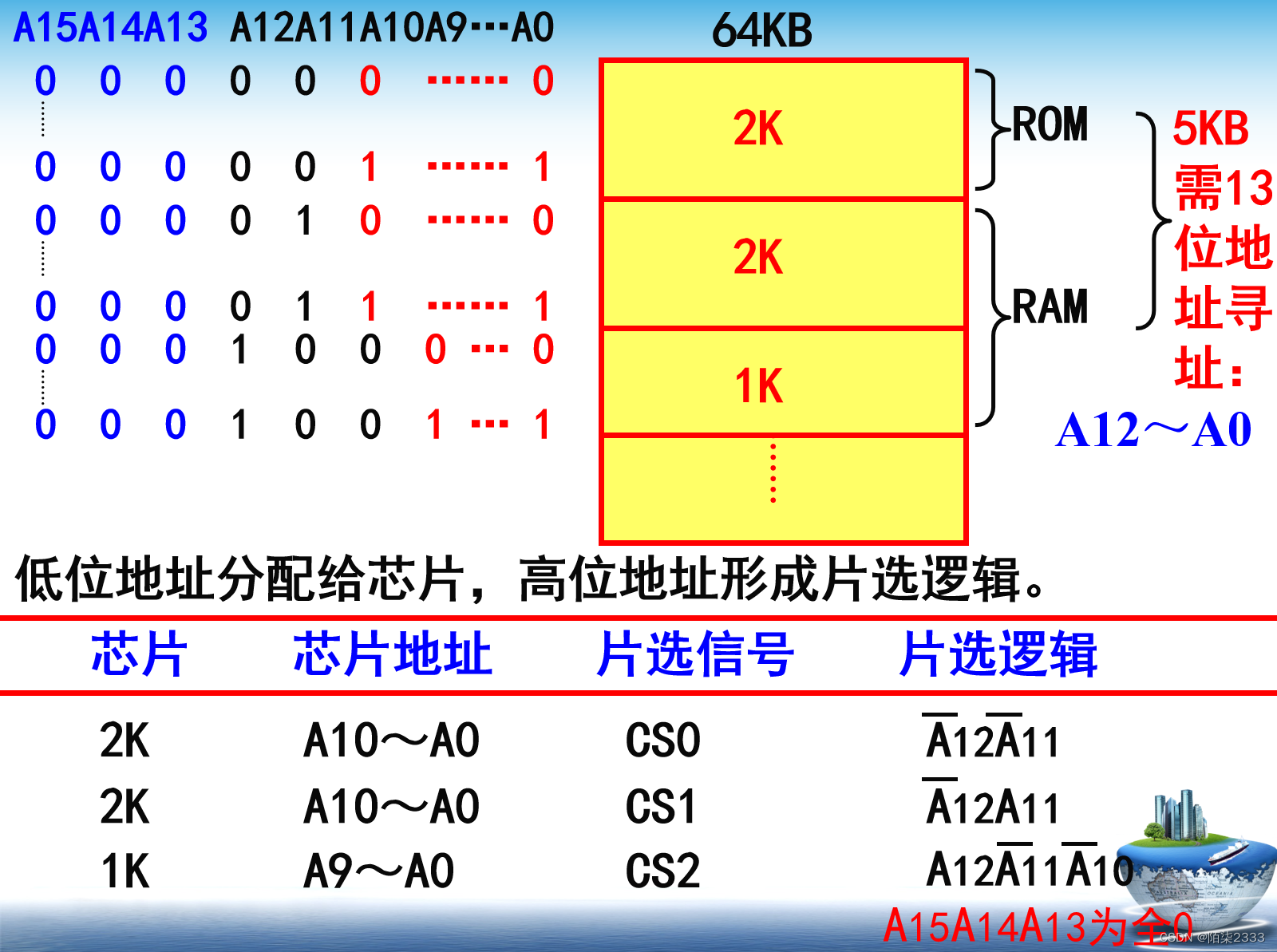

5.地址分配与片选逻辑

存储空间分配:

4KB存储器在16位地址空间(64KB)中占据任意连续区间。

某半导体存储器,按字节编址。其中,0000H~ ∼07FFH为ROM区,选用EPROM芯片(2KB/片);0800H~13FFH为RAM区,选用RAM芯片(2KB/片和1KB/片)。地址总线A15~A0(低)。给出地址分配和片选逻辑。

1.计算容量和芯片数

练习:

1、设有一个1MB容量的存储器,字长为32位,问:

(1)按字节编址,地址寄存器、数据寄存器各为多少位?编址范围为多大?

(2)按半字编址,地址寄存器、数据寄存器各为多少位?编址范围为多大?

(3)按字编址,地址寄存器、数据寄存器各为多少位?编址范围为多大?

解:

(1)按字节编址,1MB=220×8,地址寄存器为20位,数据寄存器为8位, 编址范围为00000H――-FFFFFH

(2)按半字编址,1MB=220×8=219×16,地址寄存器为19位,数据寄存器为16位, 编址范围为00000H――-7FFFFH

(3)按字编址,1MB=220×8=218×32,地址寄存器为18位,数据寄存器为32位, 编址范围为00000H――-3FFFFH

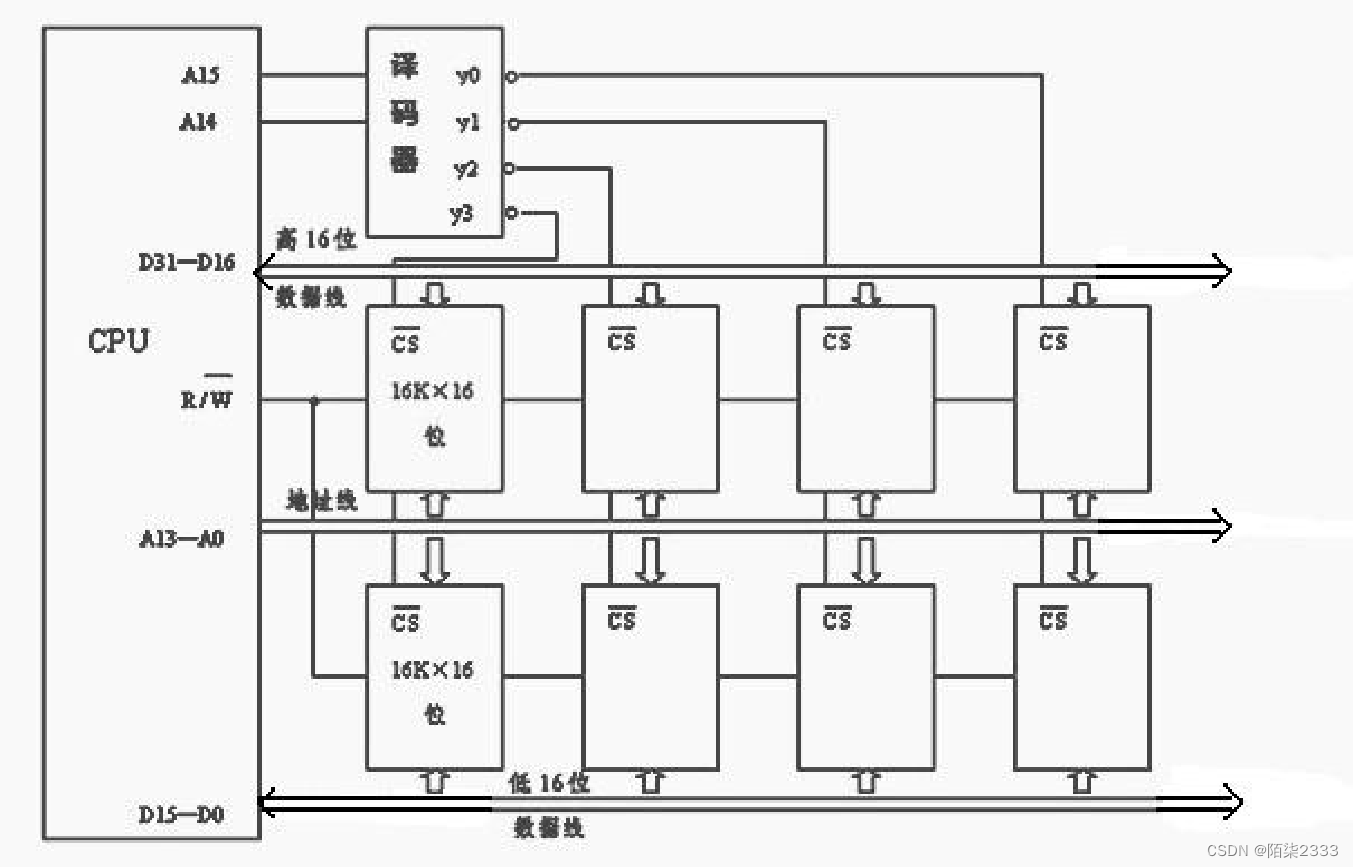

2、用16K×16位的SRAM芯片构成64K×32位的存储器。 要求:

(1)总共需要多少片SRAM芯片?地址线共需多少位?数据线共需多少位?使用何种方式的译码器?

(2)画出该芯片组成的存储器逻辑框图。

解:

(1)所需芯片总数(64K×32)÷(16K×16)= 8片,因此存储器可分为4个模块,每个模块16K×32位,地址线共需16位,数据线共需32位,各模块通过地址线A15、A14进行选片,用2:4译码器进行译码。

(2)该芯片组成的存储器逻辑框图: