目录

- 日常·唠嗑

- 一、视频效果

- 二、硬件及功能

- 1、硬件选择

- 2、功能

- 3、特点

- 未完、待续……

- 四、工程设计

- 五、板级验证

- 六、工程获取

日常·唠嗑

有2个多月没写文章了,又是老借口:“最近实在是很忙”🤣,不过说真,确实是比较忙,搞了半个月serdes,做不完的仿真😫,好几个小伙伴问东西,催更,也没时间回复。恰逢毕业季,把之前跟小马哥合作的项目更一下,供大家使用。

一、视频效果

话不多说,直接看效果

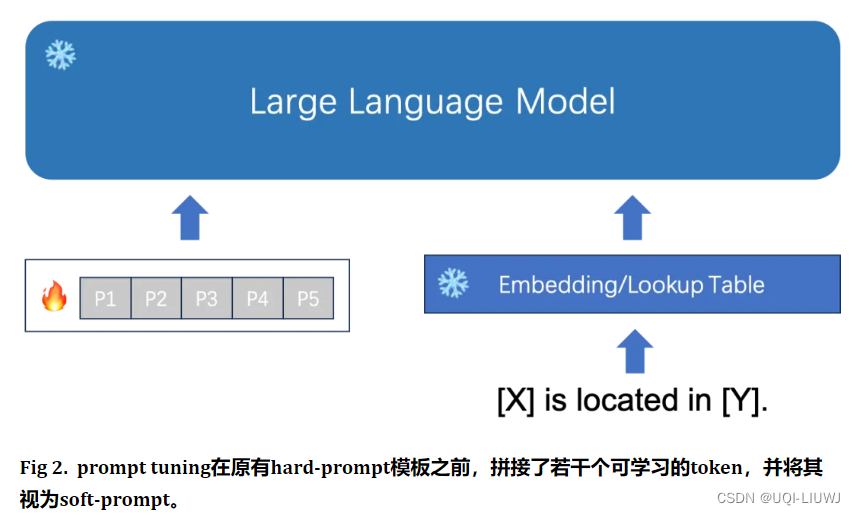

本案例采用的DDE(数字细节增强)算法,通过高斯滤波分离原图的高频信息和低频信息,利用原图和高斯滤波的差值提取细节,再将细节叠加到原始图像上,实现细节增强,增强后图像清晰度明显提高。

FPGA:图像数字细节增强算法(工程+仿真+实物,可用毕设)

二、硬件及功能

1、硬件选择

开发板Altera:EP4CE10F17C8

摄像头:OV5640

缓存数据:SDRAM

板子是自己制作的,可以提供原理图、PCB截图供大家插到论文中。

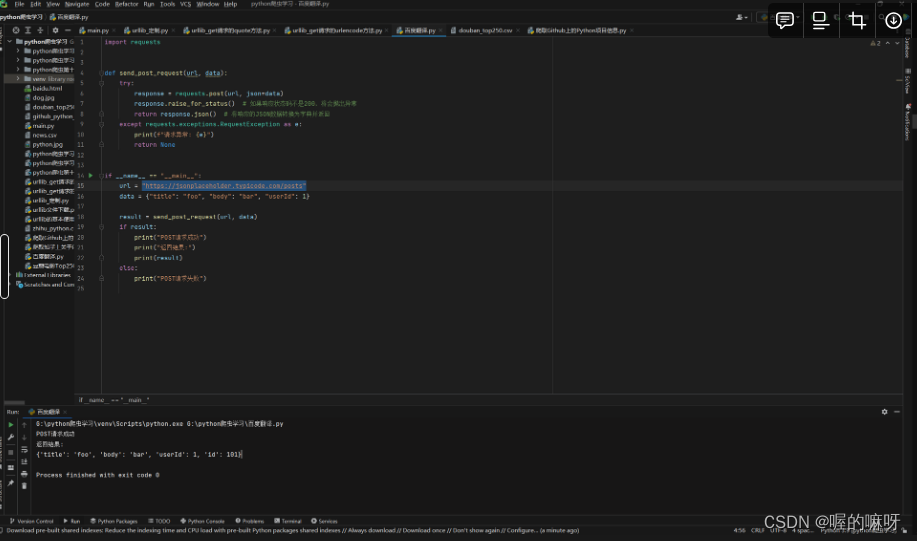

2、功能

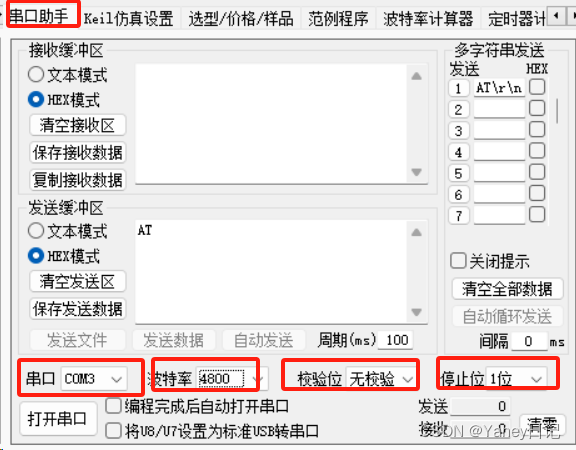

电脑上位机打开测试图像并通过串口发送给FPGA,FPGA将接收到的图像缓存在SDRAM中并从SDRAM中读出数据以产生视频源,测试视频源经过RGB转灰度、数字细节增强算法处理后实时显示在TFTLCD液晶屏上。

1.上位机通过串口发送图片给FPGA;

2.FPGA将接收到的图像缓存在SDRAM中;

3.FPGA将SDRAM中缓存的数据循环读出以产生视频流;

4.RGB转灰度算法处理;

5.图像细节增强算法处理;

6.TFTLCD液晶屏实时显示;

7.细节增强算法效果可以通过按键控制开关;

3、特点

1、全套实物(含工程资料)

2、上电即出功能效果

3、DDE数字细节增强算法(目前网上信息少,较为先进)

4、支持定制设计,将串口图片,改为摄像头实时图像

5、提供源代码工程(Verilog)

6、提供Modelsim仿真

7、提供PCB截图

8、提供文档说明&visio框图&提供售后答疑

—————————————————————————————————

未完、待续……

今天就先讲到这里,有兴趣的同学可以关注,4月9号晚上继续更新~~

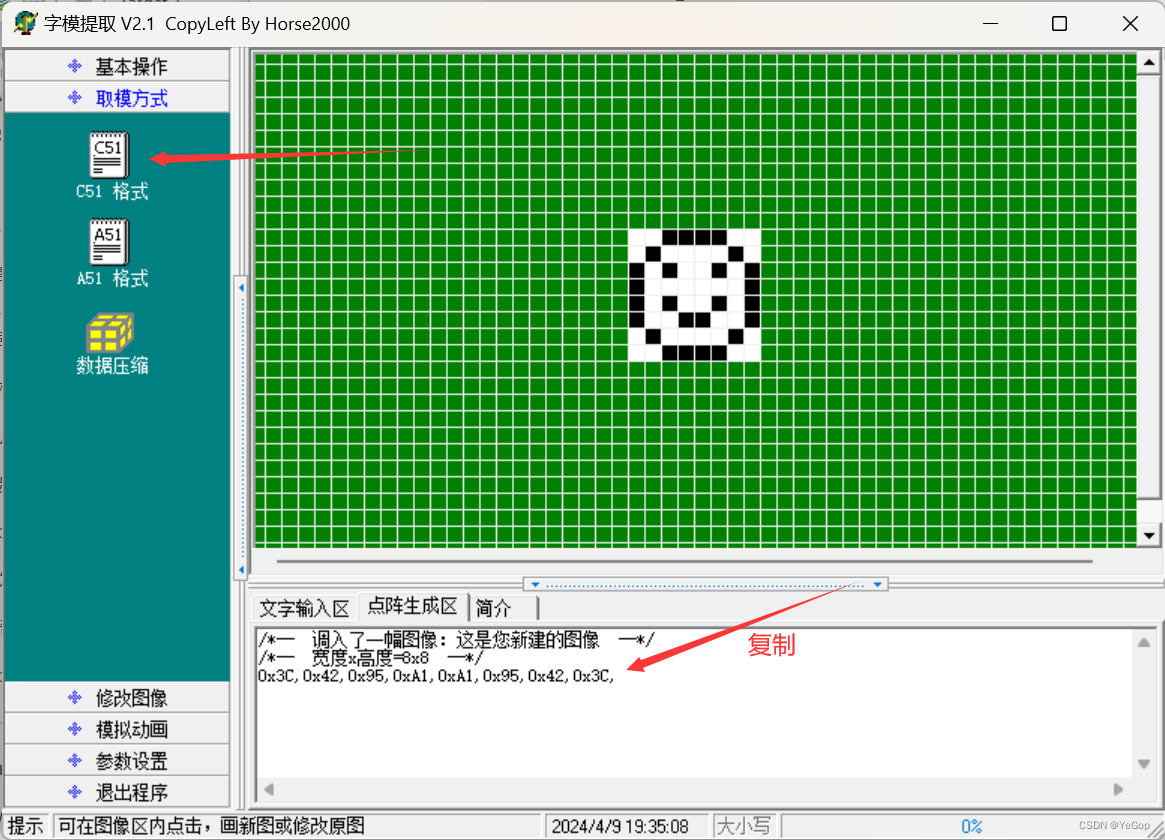

四、工程设计

五、板级验证

原图:

加载进串口:

FPGA加载到屏幕:

DDE图像细节增强:

![IntelliJ IDEA 2024.1安装与激活[破解]](https://img-blog.csdnimg.cn/direct/83568bf7104948a6ad8af14f28e9903d.png)