1、“821.2016T1(1)”,表示821真题,2016年的题,T1是 选择题/填空题/大题 的第一题,其他类似标记也是相通

2、个人小白总结自用,不一定适用于其他人,请自行甄别

3、有任何疑问,欢迎私信探讨,看到后会及时回复

选择题

- 计算机的外围设备指:主机(主机 = CPU + 内存储器)以外的设备,不止是输入输出设备,还包括外存…

- (821.07.T12)通道程序是通道控制字的有序集合

通道程序,存放在主存,由“通道控制字“组成,由”通道“执行

- 磁盘位密度总结:

①磁盘的磁道:位密度(相同的长度下所包含的bit数的多少)不同(长度从内到外越来越大,但是每一圈的bit数都是相同的,所以最终导致各个圈的位密度不同)的同心圆

②CD-ROM 的光道是:位密度相同的螺旋线

- I/O的4种控制方式:

程序查询 = 程序直接控制

DMA传输方式,外设中的数据不直接和CPU中的寄存器进行交换

DMA = Direct Memory Access = 直接存储器存取方式

CPU响应DMA的时刻是:存储周期结束

- 中断:

外部中断请求,所生成的与中断请求相对应的中断类型号是由:相关外设接口产生

访管指令(访问管理程序的指令),中断响应优先级最高

可屏蔽中断:键盘输入、磁盘寻道错中断、打印机输出中断

不可屏蔽中断:掉电中断、缺页中断、运算溢出

- RAID,磁盘冗余阵列

条带化:把数据分散到多个磁盘(408.13.T20),交叉并行读写,提高数据的存取速度,没有提高RAID的可靠性

填空题

- IO控制方式

DMA访存的3个方式:全串行方式、周期挪用、交替访存方式

DMA从CPU完全接管对总线的控制,数据交换不再通过CPU寄存器中转,而是直接IO设备和主存进行交换

通道,按工作方式分为:字节多路通道、数组多路通道、选择通道

- IO设备的2种编址方式:统一编址、独立编址

- 中断响应 – 硬件

- 中断处理 – 软件(画表写出屏蔽字,只看中断处理的优先次序)

- 中断响应的3个条件:

中断源有中断请求

CPU允许中断(即开中断状态)

CPU在一条指令执行完毕,且没有更紧迫的任务或事件

- 多级中断系统,中断服务程序内的执行顺序:删除画删除线后,就是

单级中断保护现场

和旧屏蔽字设置新的屏蔽字开中断中断处理

关中断恢复现场

和旧屏蔽字开中断

中断返回

- I/O设备和I/O 接口,只是 I/O 的硬件部分,完整的I/O 系统应该包括 I/O硬件 和 I/O软件两个部分

- 每个外设都有以一个IO接口的电路与主机连接,一个IO接口中有多个端口,一个端口对应一个地址,这样主存可以用多个地址访问一个外设

- 中断向量=中断服务程序的入口地址(易混)不等于中断向量地址

- 中断向量地址=中断类型号

是中断向量的地址,即是中断服务程序入口地址的地址

简答题

开中断,之前,必须保护现场

关中断,之后,再恢复现场

多级中断系统,中断服务程序内的执行顺序:

- 保护现场和旧屏蔽字

- 设置新的屏蔽字

- 开中断

- 中断处理

- 关中断

- 恢复现场和旧屏蔽字

- 开中断

- 中断返回

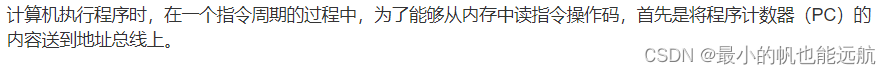

中断隐指令(王道P288)

CPU响应中断后,暂停当前的程序,是硬件的一系列操作,不是真正意义上的指令,一般有3个操作:

- 关中断,设置程序状态字寄存器PSW中的中断标志IF=0,即不允许响应其他中断;

- 保存断点和程序状态,(保存地址)将断点和程序状态保存到堆栈或特殊寄存器中。(易混)异常断点是保存当前指令的地址,因为异常处理后需要重新执行;中断的断点是保存下一条指令的指令;

- 中断服务程序寻址,通过硬件向量法或软件查询法(非硬件向量法,王道5.5小节) ,识别中断源,将对应的服务程序入口地址送给程序计数器PC。

中断处理过程(王道P288)

中断隐指令(3步)+ 中断服务程序(7步)

单重中断的中断服务程序执行顺序(408.10T21):

- 保护现场和屏蔽字

- 执行中断服务程序

- 恢复现场和屏蔽字

- 开中断

- 中断返回

多重中断,则在执行中断服务程序前后分别加:开中断、关中断

大题

- 画表,写出每一级的中断屏蔽码

只看中断处理次序

- 画图,同时请求时,画出CPU执行程序的各个中断的运行轨迹

- 先看中断响应次序最高的响应

- 再响应该屏蔽字中为0的,中断处理次序最高的响应

- 执行完再回到首次响应的中断处,看是否还有:未处理 且 屏蔽字为0

有,则:继续b)c)

无,则:执行完本中断,返回现行程序,继续执行其他:未处理 且 中断响应次序较高的中断,直到全部执行结束

- IO控制方式,CPU用于IO的时间,占整个CPU时间:

补充知识点

I/O端口的编址

| 统一编址 (只有单总线才可以) | 优点 1、不需要专门的输入/输出指令,访存指令都可以直接访问端口,程序设计灵活 2、I/O端口有较大的编址空间(因为与主存共享空间) 3、CPU读写控制逻辑电路简单(逻辑电路不需要太大的改变) | 缺点 1、I/O指令类型少,一般只能对端口进行传送操作,程序设计灵活性差 2、需要CPU提供:存储器读/写、I/O设备读/写,两组控制信号,增加CPU逻辑电路的复杂性 | 独立编址 (有专门的IO指令) |

| 缺点 1、端口占用了主存地址空间,使主存地址空间变小 2、外设寻址时间长(地址位数多,导致地址译码速度慢) | 优点 1、使用专用I/O指令,程序编制清晰 2、I/O端口的地址不占用主存地址空间 3、I/O端口地址位数少,地址译码速度快 |

I/O控制方式

| 程序查询 程序直接控制 | 程序中断 | DMA Direct Memory Access/直接存储器存取方式 | 通道控制 | |

| 数据传送 | 需要先找出1s需要查询多少次(王道P298T4/T7) | 程序控制,程序传送(软件传送) 用处理中断的时间传输数据(王道P298.T6) | 硬件控制,硬件传送 周期挪用时,每次IO控制器中的数据缓存大小1B数据消耗1个存储周期,当传送数据达到大块数据规定的量时,消耗1次中断时间(王道P298.T6) | 1、通道程序是“通道控制字”的有序集合(821.07.12) 2、CPU 查询通道的状态是通过:I/0 指令(821.05.T14) 3、一般用于大型计算机系统 |

| 中断方式 | 无 | 程序的切换--> 保存和恢复现场 | DMA不需要使用CPU内部寄存器,所以不需要保存CPU现场 除了预处理和后处理,其他时间不占用CPU资源/一个完整的DMA,只有前后需要CPU的参与 | |

| 工作特点 | CPU与I/O一直都是串行工作 | CPU与外设并行工作 传送与主程序串行工作 | CPU与外设并行工作 传送与主程序并行工作 | |

| 中断请求 | 无 | 为了传送数据 | 为了向CPU报告数据传输结束(后处理) | |

| 响应 | 指令执行周期结束后响应(除了关中断,不响应) | 存储周期结束后 = 一个总线事物完成后 每个机器周期结束均可(取指/间址/执行周期结束后均可),总线空闲时即可响应DMA请求 | ||

| 场景 | CPU控制/低速设备 | DMA控制器控制/高速设备(磁盘) | ||

| 优先级 | DMA优先级高 因为DMA数据成组传输,如果不及时处理将丢失信息 | |||

| 处理异常 | 能 | 不能,仅传送数据 | ||

| 执行 | 由硬件执行的中断隐指令和中断服务程序共同完成 | 全部硬件 | ||

| 使用CPU占比 | (见公式整理) | (见公式整理) | ||

| 其他 | CPU询问I/O接口 CPU有“原地踏步”等待现象 | 1、浮点数运算下溢直接当作机器零处理,不会引发中断 2、中断优先级 王道.P287 DMA > NMI > CPU内部异常 > INTR 硬件故障 > 软件中断 高速设备 > 低速设备(DMA > I/O设备) 输入设备 > 输出设备 实时设备 > 普通设备 | 1、DMA数据传输的3个阶段 预处理:由每个设备自己的设备驱动程序,设置本次传送的参数。I/O设备向DMA控制器发送DMA请求,DMA接口向CPU发送总线请求。 数据传送:由DMA控制器直接控制总线完成 后处理:DMA向CPU发送中断请求,CPU执行中断服务程序,做DMA结束处理 (王道.P294.T06) | |

| 联系 | 1、程序查询和程序中断,用于数据传输率低的设备(408.13.T22,并不是说适用于所有外设 DMA、通道控制方式,用于数据传输率较高的设备 | |||

DMA的工作方式 / DMA与CPU共同访存的3种方式 / DMA数据传输方法(绿书P351/王道P292)

| 全串行方式 | 周期挪用/周期窃取 | 交替访存方法/透明DMA方式 | |

| 释义 | DMA传输时,CPU停止访存,DMA传送一块数据使用完总线后,再将总线控制权交给CPU | 即DMA有请求,则可挪用一个或若干个存储周期 传送完一个数据字后,马上释放总线(单字传送方式),单个字传送完后,CPU就可以访问存储器了(在DMA周期挪用时,CPU也可以访问存储器) | 将一个CPU工作周期(机器周期)分为两个周期,一个周期DMA专用访存,另一个周期CPU专用访存 |

| 优点 | 控制简单,适合高速外设 | 即实现了IO的数据传送,又保证了CPU程序的执行,较好的发挥了主存和CPU的效率 | 适合CPU工作周期(机器周期)比主存存储周期长得多得的情况,不需要总线使用权的申请、建立和归还 |

| 缺点 | 1、DMA在访存时,CPU基本处于不工作或保持原状态 2、即使是高速外设,两个单位数据的准备间隔时间一般也是大于存储周期,所以存储器的效能未能充分发挥 | DMA每次挪用一个存储周期,都要分别申请、建立、归还总线的控制权 | 硬件逻辑复杂,且要求存储器速度快 |