文章目录

- 前言

- 一、时钟概要

- 1.1、CC

- 1.2、BUFR、BUFIO、BUFMR

- 1.3、CMT

- 1.4、BUFH

- 1.5、BUFG

- 二、时钟路由资源

- 三、CMT

前言

本文主要参考xilinx手册ug472

一、时钟概要

7系列FPGA时钟资源主要有CC、BUFR、BUFIO、BUFMR、CMT、BUFG、BUFH和GTE_COMMON

1.1、CC

“CC”,它是“Clock-Capable”即时钟功能的缩写,表示具有时钟功能的引脚,换句话说,并不是所有的引脚都可以接时钟的,有只有通过特定的引脚才能将外部时钟信号引入FPGA内部的时钟资源,这个引脚有两种,分别称之为MRCC(Multi-region clock-capable I/O)和SRCC(Single-region clock-capable I/O)。Multi-region译为多区域,Single-region译为单区域,而者的直观区别在于MRCC可以连接到BUFMR上,但SR不可以,BUFMR具有扩展功能,可以将本BANK时钟引入到其它BANK上,所以称可以连接到BUFMR的CC为MRCC。每个BANK有50个引脚,这五十个里面有两对用于SRCC,有两对用于MRCC,如下图原理图所示。它们都是差分的,如果接单端时钟则需接到“P”上,对应的“N”引脚不可用。这些信号可以连接到本bank的BUFR、BUFIO、CMT以及同侧的16个BUFG。

1.2、BUFR、BUFIO、BUFMR

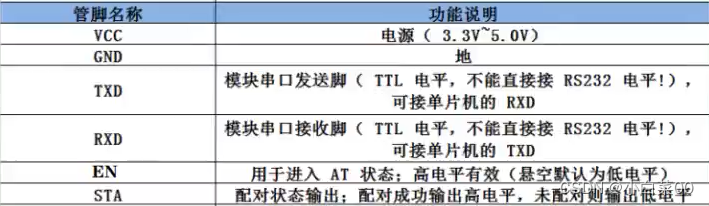

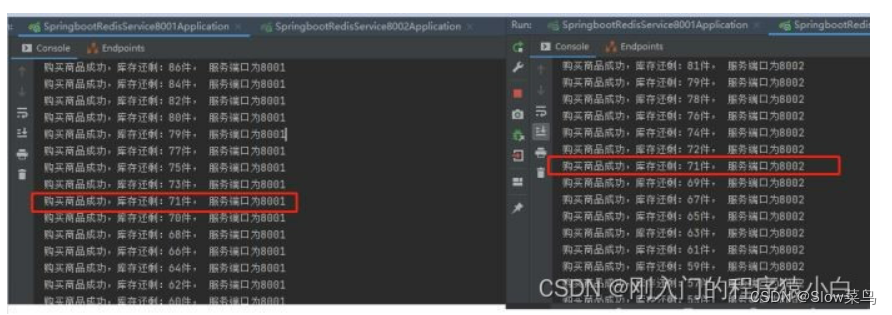

BUFR、BUFIO、BUFMR它们都位于I/O BANK,所以它们是与引脚相关的区域时钟缓冲器,可有助于实现时钟源的同步采集,串并之间的转换等等。每个有引脚的BANK都有四个BUFIO和BUFR、两个BUFMRCE。

BUFIO也是区域时钟缓冲器,它的作用是用来驱动I/O BANK里面的ILOGIC和OLOGIC,(一般会用为OSERDESE2 和ISERDESE2)。所以BUFIO适合用于采集源同步数据,但不能用来驱动任何其它资源。

BUFR区域时钟缓冲器,与BUFIO不同在于可以驱动BUFG可以驱动的同一时钟区域中的任何时钟点。如下图很好的解释了BUFIO和BUFR的区别。而且BUFR还具有分频功能,可以实现1到8倍的分频,可用于串并转换。

BUFMR还是区域时钟缓冲器,之所以只有两个是对应MRCC,因为MRCC就两个,所以BUFMR多了也没多啥用。它的作用就是扩展时钟区域,可以将某BANK的时钟引入到上下相邻的BANK中去,如下图所示,这里将MRCC直连到了BUFMR,但在实际应用情况下,MRCC需要先进过IOBUF,才可以连接到BUFMR。

1.3、CMT

在7系列FPGA中,CMT包括混合模式时钟管理器(MMCM)和锁相环(PLL)。PLL可以是MMCM的子集。

下图显示了各种时钟输入源与MMCM/PLL之间连接的高级视图。在7系列FPGA中,时钟输入连接允许多个资源为MMCM/PLL提供参考时钟。输出计数器(分频器)的数量为八个,其中一些能够输出反向时钟信号(180°相位移)。7系列FPGA的MMCM具有无限的精细相移能力,可以在任意方向上使用动态相移模式。精细相移的分辨率取决于VCO频率。可用于支持更大的时钟频率合成能力的CLKFBOUT和CLKOUT0的分数分频功能为1/8(0.125)增量。7系列FPGA还为MMCM添加了扩展频谱功能。如果不使用MMCM扩展频谱功能,则外部输入时钟上的扩展频谱将不会被滤波,从而传递到输出时钟。

1.4、BUFH

经过BUF的时钟只在本区域有效,其中H是Horizontal的缩写。每个BANK有12个BUFH,它们位于BANK的一侧,且在水平中间位置排成一列,所以下图是左右相邻两个BANK的BUFH。

如下图是一个BANK的整体,BUFH可以驱动同一BANK的所有资源,我们可以看出“上”和“下”是对称分布的,BUFH位于BANK的一侧垂直居中,中间的分割线是有12条水平时钟线,与12个BUFH相连。BUFG也是通过连接到BUFH进而通过这12条水平时钟线驱动整个BANK的逻辑资源。每个BANK资源是按照一定的规律进行排列,也就是每列有50个CLB、50个引脚、10个BRAM,它们均匀的分布在水平时钟线两侧。不同型号芯片每个BANK的资源是不一样的,但每列资源是固定的,只不过行数的多少。

1.5、BUFG

BUFG是全局时钟缓冲器,如下图所示,一列有32个,而且每个芯片都会有32个BUFG。它是我们用的最多的时钟buff,经过BUFG的时钟可以连接到任意资源上去,BUFG不仅可以实现时钟缓冲,还有时钟选择、控制等功能。

二、时钟路由资源

时钟资源包括路由资源和硬核资源,时钟架构是以全局时钟和区域时钟组合搭配而成,总体思路就是以BANK为单元组建区域时钟,以BUFG为纽带连接各个BANK,依次实现模块化的时钟架构。

下图是《ug472》提供的时钟架构图。首先我们需要了解下FPGA内部的大致结构,xilinx的FPGA逻辑资源大致可分为两个部分,一部分是I/O BANK,即下图中的“I/O Column”、“CMT Backbone”和“CMT Column”这三部分组成,这里的时钟BUF、IOBUF及I/O LOGIC的不同组合实现FPGA内部数据与外部的交互,另一部分就是以CLB和BRAM为主的资源来实现我们的逻辑功能,不同BANK可能有些其他硬核资源,例如PCIE、XADC、GTP等等。

HROW即水平时钟线,也就是在前文当中所阐述的BUFH或BUFG所走的线,时钟沿着水平中心线向两侧延伸以为其他器件提供时钟。而左右BANK对称的中心线即为“Clock Backbone”,BUFG在一定长程度上水平发布在“Clock Backbone”中间,一般来讲上部分16个BUFG时钟源来自上半部分的所有BANK,下部分16个BUFG时钟源来自下半部分的所有BANK,而他们的输出可以到整个device的任意位置。

如下图是各种BUF的大致路由概念图,其中黑点表示连接,竖线带箭头表示可驱动区域,箭头延伸出虚线框表示本BANK以外的其它BANK。BUFG可以通过水平时钟线(HROW)驱动片上任意可接时钟资源,BUFH通过HROW可以驱动本BANK的任意可接时钟资源,它们是共享HROW。BUFIO仅可驱动I/O BANK中的可接时钟资源,BUFR可驱动I/O BANK及其它逻辑资源,BUFMR可驱动多BANK的BUFIO和BUFR。

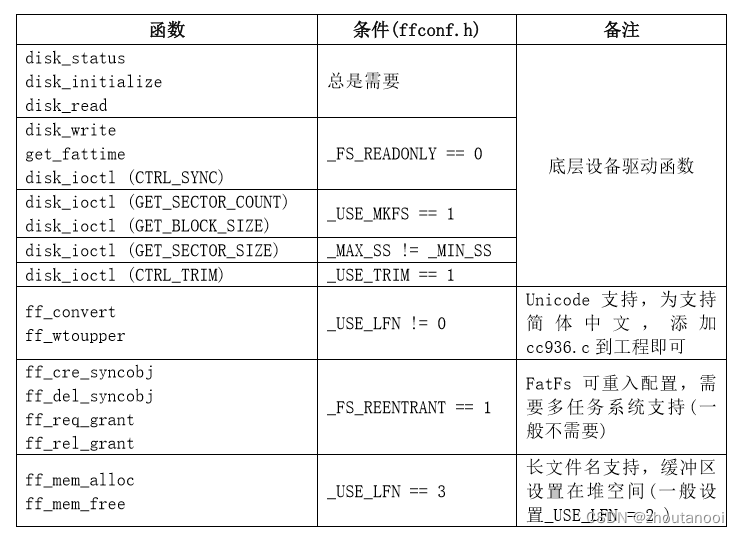

具体的时钟资源的驱动关系如下表所示:

三、CMT

每个BANK至多包含一个CMT,具体视芯片资源而定,如下图是CMT的框图,可见输入到CMT也就是PLL或MMCM的时钟可以有多种选择,甚至是本地逻辑路由,但并不建议这样搞,输出时钟会连接到BUFH或者BUFG,这些如果没有特殊要求都会自动实现的。

无论是MMCM还是PLL,其功能实现的基本原理是一致的,如下图所示是MMCM产生多个时钟的流程图。每个时钟输入都有一个可编程的计数分配器,也就是“D”,可控制对输入时钟进行分频,PFD是相位检测器,用来比较输入时钟和反馈时钟上升沿的相位和频率进而生成与两个时钟之间的相位和频率成比例的信号,这是一个上升或下降的信号,该信号驱动电荷泵(CP)和环路滤波器(LF)产生VOC的参考电压。当VCO频率过高时,PFD会激活一个下降信号,从而将电压降低,上升信号将增加电压抬高频率。VOC即压控振荡器(Voltage Controlled Oscillator),就是输出频率与输入控制电压有对应关系的振荡电路,有LC和RC压控振荡器,一般用的是RC的。MMCM原理是在VCO输出时钟的基础上可对其进行分频、相位和占空比的调整,已产生我们所需时钟。

CMT具有时钟矫正网络,可实现输出时钟频率与输入时钟频率相位一致,这就为需时钟同步的相关设计提供便利,最起码不需要在这基础上花费时间调整时钟相位,并且具有抖动滤波的功能。我们可以调用相关原语或IP核来实现相关设计。

根据上述描述可知,根据CMT产生所用时钟的原理就是首先产生VCO这个基础时钟,然后在其基础上进行分频得到我所需时钟,具体公式如下所示,其中“M”和“D”是可编程控制的,而且VCO的频率也是有限制的,在《DS181》有相关描述,如下表所示。“O”是每路输出时钟对应一个。就CMT内部而言,输出时钟频率的产生有两种情况,一种是仅适用整数除法进行频率合成,另一种是使用小数分频产生所用时钟,为什么要分这两种呢,因为用整数除法我们可以调整时钟占空比,用小数则不能调整,而这个是其内部自动选择的,我们只需知道即可。

以下为MMCM原语。

MMCME2_ADV #(.BANDWIDTH("OPTIMIZED"), // Jitter programming (OPTIMIZED, HIGH, LOW).CLKFBOUT_MULT_F(5.0), // Multiply value for all CLKOUT (2.000-64.000)..CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB (-360.000-360.000).// CLKIN_PERIOD: Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN1_PERIOD(0.0),.CLKIN2_PERIOD(0.0),// CLKOUT0_DIVIDE - CLKOUT6_DIVIDE: Divide amount for CLKOUT (1-128).CLKOUT1_DIVIDE(1),.CLKOUT2_DIVIDE(1),.CLKOUT3_DIVIDE(1),.CLKOUT4_DIVIDE(1),.CLKOUT5_DIVIDE(1),.CLKOUT6_DIVIDE(1),.CLKOUT0_DIVIDE_F(1.0), // Divide amount for CLKOUT0 (1.000-128.000).// CLKOUT0_DUTY_CYCLE - CLKOUT6_DUTY_CYCLE: Duty cycle for CLKOUT outputs (0.01-0.99)..CLKOUT0_DUTY_CYCLE(0.5),.CLKOUT1_DUTY_CYCLE(0.5),.CLKOUT2_DUTY_CYCLE(0.5),.CLKOUT3_DUTY_CYCLE(0.5),.CLKOUT4_DUTY_CYCLE(0.5),.CLKOUT5_DUTY_CYCLE(0.5),.CLKOUT6_DUTY_CYCLE(0.5),// CLKOUT0_PHASE - CLKOUT6_PHASE: Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT0_PHASE(0.0),.CLKOUT1_PHASE(0.0),.CLKOUT2_PHASE(0.0),.CLKOUT3_PHASE(0.0),.CLKOUT4_PHASE(0.0),.CLKOUT5_PHASE(0.0),.CLKOUT6_PHASE(0.0),.CLKOUT4_CASCADE("FALSE"), // Cascade CLKOUT4 counter with CLKOUT6 (FALSE, TRUE).COMPENSATION("ZHOLD"), // ZHOLD, BUF_IN, EXTERNAL, INTERNAL.DIVCLK_DIVIDE(1), // Master division value (1-106)// REF_JITTER: Reference input jitter in UI (0.000-0.999)..REF_JITTER1(0.0),.REF_JITTER2(0.0),.STARTUP_WAIT("FALSE"), // Delays DONE until MMCM is locked (FALSE, TRUE)// Spread Spectrum: Spread Spectrum Attributes.SS_EN("FALSE"), // Enables spread spectrum (FALSE, TRUE).SS_MODE("CENTER_HIGH"), // CENTER_HIGH, CENTER_LOW, DOWN_HIGH, DOWN_LOW.SS_MOD_PERIOD(10000), // Spread spectrum modulation period (ns) (VALUES)// USE_FINE_PS: Fine phase shift enable (TRUE/FALSE).CLKFBOUT_USE_FINE_PS("FALSE"),.CLKOUT0_USE_FINE_PS("FALSE"),.CLKOUT1_USE_FINE_PS("FALSE"),.CLKOUT2_USE_FINE_PS("FALSE"),.CLKOUT3_USE_FINE_PS("FALSE"),.CLKOUT4_USE_FINE_PS("FALSE"),.CLKOUT5_USE_FINE_PS("FALSE"),.CLKOUT6_USE_FINE_PS("FALSE"))MMCME2_ADV_inst (// Clock Outputs: 1-bit (each) output: User configurable clock outputs.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT0B(CLKOUT0B), // 1-bit output: Inverted CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT1B(CLKOUT1B), // 1-bit output: Inverted CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2.CLKOUT2B(CLKOUT2B), // 1-bit output: Inverted CLKOUT2.CLKOUT3(CLKOUT3), // 1-bit output: CLKOUT3.CLKOUT3B(CLKOUT3B), // 1-bit output: Inverted CLKOUT3.CLKOUT4(CLKOUT4), // 1-bit output: CLKOUT4.CLKOUT5(CLKOUT5), // 1-bit output: CLKOUT5.CLKOUT6(CLKOUT6), // 1-bit output: CLKOUT6// DRP Ports: 16-bit (each) output: Dynamic reconfiguration ports.DO(DO), // 16-bit output: DRP data.DRDY(DRDY), // 1-bit output: DRP ready// Dynamic Phase Shift Ports: 1-bit (each) output: Ports used for dynamic phase shifting of the outputs.PSDONE(PSDONE), // 1-bit output: Phase shift done// Feedback Clocks: 1-bit (each) output: Clock feedback ports.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock.CLKFBOUTB(CLKFBOUTB), // 1-bit output: Inverted CLKFBOUT// Status Ports: 1-bit (each) output: MMCM status ports.CLKFBSTOPPED(CLKFBSTOPPED), // 1-bit output: Feedback clock stopped.CLKINSTOPPED(CLKINSTOPPED), // 1-bit output: Input clock stopped.LOCKED(LOCKED), // 1-bit output: LOCK// Clock Inputs: 1-bit (each) input: Clock inputs.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock// Control Ports: 1-bit (each) input: MMCM control ports.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.PWRDWN(PWRDWN), // 1-bit input: Power-down.RST(RST), // 1-bit input: Reset// DRP Ports: 7-bit (each) input: Dynamic reconfiguration ports.DADDR(DADDR), // 7-bit input: DRP address.DCLK(DCLK), // 1-bit input: DRP clock.DEN(DEN), // 1-bit input: DRP enable.DI(DI), // 16-bit input: DRP data.DWE(DWE), // 1-bit input: DRP write enable// Dynamic Phase Shift Ports: 1-bit (each) input: Ports used for dynamic phase shifting of the outputs.PSCLK(PSCLK), // 1-bit input: Phase shift clock.PSEN(PSEN), // 1-bit input: Phase shift enable.PSINCDEC(PSINCDEC), // 1-bit input: Phase shift increment/decrement// Feedback Clocks: 1-bit (each) input: Clock feedback ports.CLKFBIN(CLKFBIN) // 1-bit input: Feedback clock);

属性参数:

1、BANDWIDTH

指定影响抖动、相位裕度和MMCM其他特性,有“HIGH”、“LOW”和“OPTIMIZED”三个选项,默认OPTIMIZED即可

2、CLKFBOUT_MULT_F

即上述的M,整数的范围是2到64,小数的最小刻度是0.125。

3、CLKFBOUT_PHASE

指定时钟反馈输出的相位偏移(以度为单位)。对反馈时钟进行移位会导致到MMCM的所有输出时钟的负相移。范围是0到360,默认是0。

4、CLKIN1/2_PERIOD

输入时钟的周期,以ns为单位,最小刻度到ps。允许范围是0.938到100ns。

5、CLKOUT[1:6]_DIVIDE和CLKOUT[0]_DIVIDE_F

确定输出频率的,也就是对VCO的分频值,范围是1到128,其中CLKOUT0可以精确到0.125,CLKOUT1到6是整数。

6、CLKOUT[0:6]_DUTY_CYCLE

以百分比的形式关联输出时钟占空比,范围是0.01到0.99

7、CLKOUT [0:6]_PHASE

输出相位,范围是-360到360,具体多少输入度数即可,但实际不一定是对应度数。

8、CLKOUT4_CASCADE

布尔值,将输出分频器(计数器)CLKOUT6级联到CLKOUT4分频器的输入中,以得到大于128的输出时钟分频器,有效地提供了16384的总分频值。

9、COMPENSATION

时钟输入补偿。 必须设置为ZHOLD。 定义MMCM反馈的配置方式。

ZHOLD:表示MMCM配置为在I / O寄存器中提供负的保持时间。

EXTERNAL:表示正在对FPGA外部的网络进行补偿。

INTERNAL:表示MMCM正在使用其自己的内部反馈路径,因此不会补偿任何延迟。

BUF_IN:表示该配置与其他补偿模式不匹配,并且不会补偿任何延迟。 如果时钟输入由BUFG / BUFH / BUFR或GTX / GTH / GTP驱动,则是这种情况。

10、SS_*

扩频相关的

11、*_USE_FINE_PS

对应的精细相移使能

端口描述:

1、CLKOUT[0:6]

这些用户可配置的时钟输出(对于MMCM为CLKOUT0至CLKOUT6,对于PLL为CLKOUT0至CLKOUT5)可以将VCO相位输出(用户可控)从1(旁路)到128分频。输入时钟和输出时钟可以为 相位对齐。

当与BUFR或BUFIO一起使用时,只有MMCM可以从时钟输出CLKOUT0至CLKOUT3直接连接到HPC。 此外,CLKOUT0至CLKOUT3可以连接到CMT主干,以级联MMCM和PLL。 类似于将MMCM和PLL从CCIO引脚驱动到相邻区域(请参见具有时钟的输入),级联使用CMT主干中可用的一些有限资源来直接在相邻区域中连接时钟资源。 同一列内级联元素之间也会产生相位偏移。

有关可能的配置,请参见MMCM和PLL使用模型。 在MMCM中,CLKOUT0和CLKFBOUT可以在小数分频模式下使用。 所有CLKOUT输出均可在非小数模式下使用,以提供静态或动态相移。 在小数模式下,仅允许固定相移。 有关更多信息,请参见静态相移模式。

2、CLKOUTB[0:3]

CLKOUT [0:3]的反相(180°相移)。 在PLL中不可用。

3、动态配置端口,暂不描述

4、PSDONE

完成相移的输出信号与PSCLK同步。 当前的相移操作完成后,将在一个时钟周期内声明PSDONE信号,以指示可以启动一个新的相移周期。 在PLL中不可用。

5、CLKFBOUT

提供反馈时钟的。

6、CLKFBOUTB

没啥用

7、CLKFBSTOPPED

状态引脚,指示反馈时钟已停止。 该信号在时钟停止的一个时钟周期内有效。 反馈时钟重新启动并且MMCM重新锁定后,信号将置为无效。 在PLL中不可用。

8、CLKINSTOPPED

状态引脚,指示输入时钟已停止。 该信号在时钟停止的一个时钟周期内有效。 时钟重新启动并达到LOCKED(锁定)或时钟切换到备用时钟输入且MMCM重新锁定后,信号将置为无效。 在PLL中不可用。

9、LOCKED

MMCM / PLL的输出,用于指示MMCM / PLL在输入引脚上何时实现了参考时钟和反馈时钟的相位和频率对准。 相位对齐在预定义的窗口内,频率匹配在预定义的PPM范围内。 MMCM上电后自动锁定,不需要额外的复位。 如果输入时钟停止,违反相位对齐(例如,输入时钟相移)或频率已更改,则在一个PFD时钟周期内将LOCKED置为无效。 解除锁定时必须复位MMCM / PLL。 在声明LOCKED之前,不应使用时钟输出。

10、CLKIN1/2

CLKIN1是主要参考时钟输入,可以由SRCC或MRCC I / O直接在同一时钟区域内驱动,SRCC或MRCC I / O可以通过垂直相邻时钟区域内的CMT主干,BUFG,BUFR,BUFH,互连(不推荐)来驱动,或直接通过 高速串行收发器。 当时钟输入来自用于级联CMT功能的另一个CMT模块时,只能使用CLKOUT [0:3]。

CLKIN2是辅助时钟输入,用于动态切换MMCM / PLL参考时钟。CLKIN2可以由SRCC或MRCC I / O直接在同一时钟区域内驱动,SRCC或MRCC I / O通过CMT主干在垂直相邻的时钟区域内进行驱动,BUFG,BUFR,BUFH,互连(不推荐),或直接通过 高速串行收发器。

11、CLKINSEL

CLKINSEL信号控制时钟输入MUX的状态,高= CLKIN1,低= CLKIN2。 时钟切换期间,MMCM / PLL必须保持在RESET状态。MMCM和PLL参考时钟可以通过使用CLKINSEL引脚动态切换。 切换是异步完成的。 时钟切换后,MMCM / PLL可能会丢失“锁定”并自动锁定到新时钟上。 因此,一旦时钟切换,则必须复位MMCM / PLL。 MMCM / PLL时钟MUX切换如图3-10所示。 CLKINSEL信号直接控制MUX。 不存在同步逻辑。