本文主要介绍以下几点:

- 什么是时钟

- 什么是外部时钟和内部时钟

- 时钟偏斜skew、时钟延迟delay和时钟抖动jitter的定义、三者的区别

- 时钟抖动、时钟偏斜、时钟延迟会引起或不会引起什么情况

- 布线方式的影响,正偏差和负偏差的好处和坏处

- 什么是同步电路

- 什么是异步电路

- 时钟域和时钟树

- FPGA的时钟资源BUFG/BUFH/BUFR/BUFIO/BUMR/MMCM/PLL

注:参考文章在文末给出

目录

- 一、时钟的定义和分类

- 二、时钟延迟、时钟偏移、时钟抖动

- 三、布线对时序的影响

- 1.布线方向的影响:正偏差

- 2.布线方向的影响:负偏差

- 四、同步时钟和异步时钟

- 五、时钟域和时钟树

- 六、FPGA时钟

- 1.总体架构

- 2.7系列FPGA的BUF资源

- (1)BUFG/BUFH/CMT

- (2)BUFR/BUFMR/BUFIO

- 3.CMT(MMCM/PLL)

- 1.MMCM

- 2.PLL

一、时钟的定义和分类

时钟是电路产生的具有周期性的脉冲信号。

外部时钟:FPGA外部产生并通过专用时钟引脚接入FPGA的时钟

内部时钟:FPGA内部生成的时钟

外部时钟是指时钟信号的来源是在FPGA芯片的外部。通常来说,外部时钟源对FPGA设计来说是必需的,因为一般FPGA芯片内部没有能够产生供内部逻辑使用的时钟信号的选频和激励电路。所以,需要在FPGA芯片的外部使用晶振以及恰当的电阻、电容、电感、三极管等器件,来搭建用于产生时钟信号的电路,并将其通过FPGA芯片的恰当物理管脚引入到FPGA内部供时序逻辑使用。

内部时钟主要有以下几种:

(1)再生时钟

以一个输入的时钟信号作为参考,在此基础上通过调整其频率和相位而产生出来的新时钟。一般为DCM、PLL、MMCM生成的时钟等。

(2)门控时钟

是由组合逻辑产生的时钟。门控时钟由组合逻辑产生,那么就会有竞争和险象,所以门控时钟信号很容易产生毛刺,而寄存器等存储单元对时钟信号的边沿都非常敏感,因此具有毛刺的时钟会造成时序逻辑的不稳定。关于门控时钟可以参考之前的文章

数字IC设计入门(二)——门控时钟_时钟门控ic设计-CSDN博客

(3)行波时钟

行波时钟通常用于低速分频时钟,即讲一个触发器的输出用作另一个触发器的书中输入。通常情况下,行波时钟是触发器的Q端输出,如果该时钟负载较小,且驱动电路能容忍的建立 / 保持时间较大,则可以像全局时钟一样可靠地工作。

如果行波时钟在行波链上各触发器的时钟之间产生较大的时间偏移,并且会超出最坏情况下的建立 / 保持时间以及组合电路延迟之和,则该时钟不能满足要求。

通常情况下,也不建议引入行波时钟,因为这样会在FPGA设计中引入新的时钟域,增加时序分析的难度,并且由于行波时钟的相位通常会滞后于原始时钟,因此后续触发器的保持时间不一定能够得到满足。

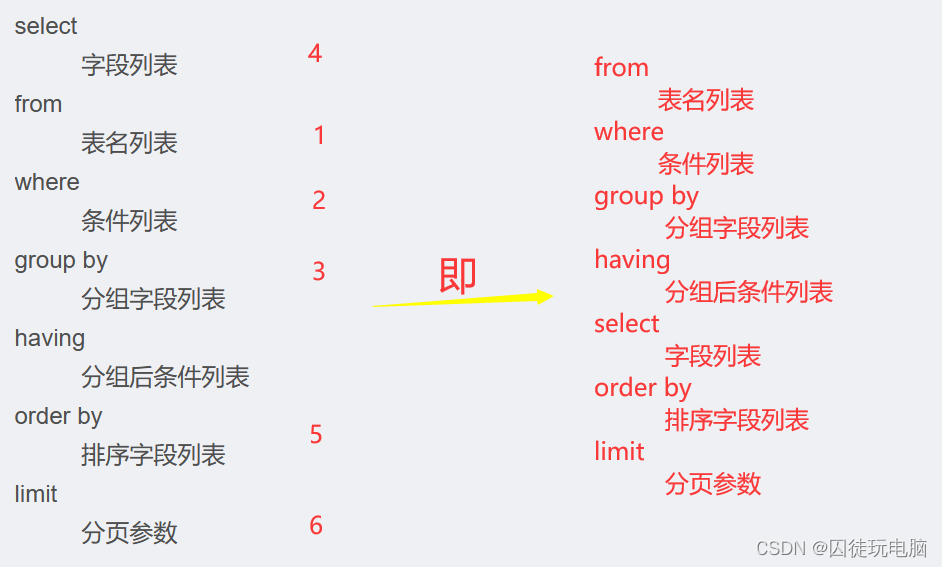

二、时钟延迟、时钟偏移、时钟抖动

- 时钟延迟是本时钟相对于源节点时钟的延迟

- 时钟偏移是同一源节点在不同终点处的不同时钟之间的偏差

- 时钟抖动是对于某一个时钟,在时钟变化边沿时,会有一定的随机性,即时钟沿向前或向后一小段时间

具体如下:

时钟偏移(clock skew):同一个时钟信号在到达分支的寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。

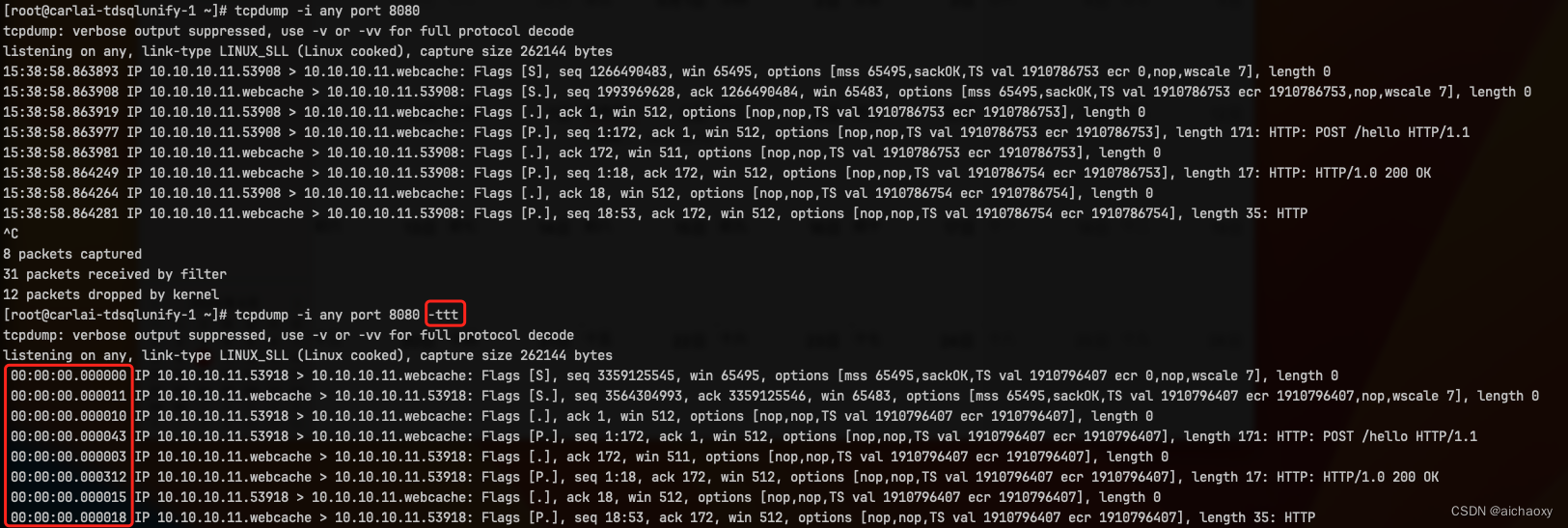

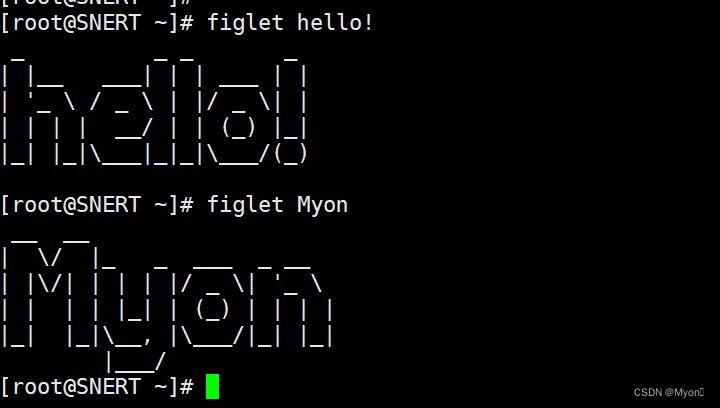

时钟抖动(clock jitter):相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动。如下图所示:

时钟偏斜发生在两个时钟信号之间,一般不会引起电路实际时钟周期的变化,只会导致时钟相位的偏移;时钟抖动可以发生在一个时钟信号自身,会引起时钟周期的变化。

三、布线对时序的影响

在同一时钟下的不同寄存器之间,由于布线长短的不同会使得时钟出现一定的偏差。

1.布线方向的影响:正偏差

若时钟布线和数据流动方向一致,则会造成skew为正,也就是说对于后续的寄存器其时钟会相对前面寄存器的时钟延迟一段时间。

这样造成的影响为:

- 更容易满足建立时间的要求,可以提高时钟频率,提高数据处理速率;

- 需要更长的保持时间

2.布线方向的影响:负偏差

若时钟布线和数据流动方向一致,则会造成skew为负,也就是说对于后续的寄存器其时钟会相对前面寄存器的时钟提前一段时间。

这样造成的影响为:

- 更容易满足保持时间要求,不容易发生竞争冒险;

- 对建立时间的要求更高,导致时钟频率不能做的很高

四、同步时钟和异步时钟

同步时钟

两个时钟之间的相位关系固定就是同步时钟,一般来说同一个MMCM或PLL产生的时钟属于同步时钟。

异步时钟

时钟之间的相位关系不是固定的,则认为其为异步时钟。两个来自不同晶振的时钟,一定是异步时钟。

此外,对于同源时钟、同时钟域时钟等下文做出了更详细的解释:

同步时钟 异步时钟概念解析

需要注意的是同步时钟≠同时钟域时钟,对于同步时钟,其下信号也可能要做CDC(跨时钟域处理)。

五、时钟域和时钟树

时钟域问题简介

时钟域:电路中由同一个时钟信号控制的区域。跨越时钟域的信号需要特别处理,才能确保传输正确。一个时钟域只能存在一个时钟信号,但是一个时钟信号最多可以对应两个时钟域,当其上升沿和下降沿分别都被一部分资源敏感的时候。

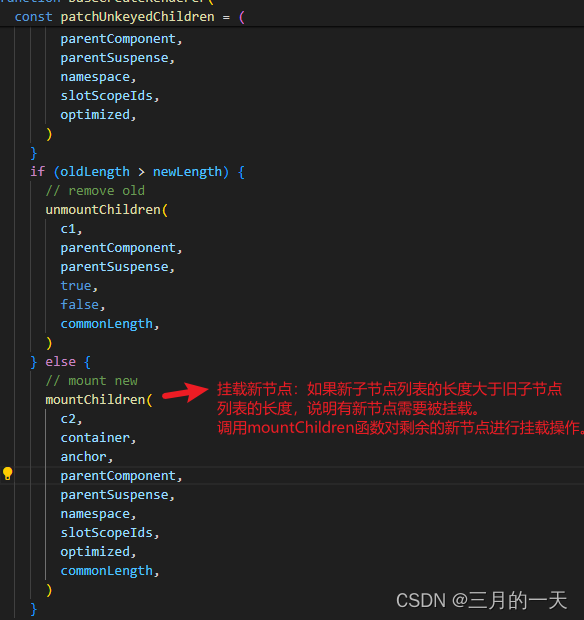

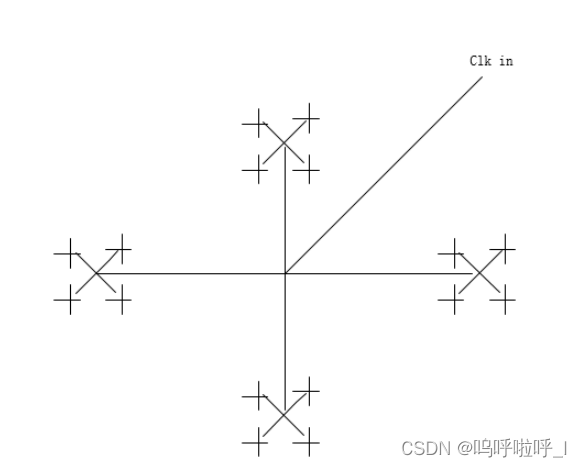

时钟树:时钟树,是个由许多缓冲单元(buffer cell)平衡搭建的网状结构,它有一个源点,一般是时钟输入端(clock input port),也有可能是design内部某一个单元输出脚(cell output pin),然后就是由一级一级的缓冲单元搭建而成,目的就是使所用终点的clock skew(一般最关心这个)、insertion delay以及transition了,满足设计要求。

上图为一个时钟树的原理结构图,时钟信号由最中间的树根引入时钟树,并经由第一级缓存扇出若干个分别送往不同的区域;在各个区域中,再采用同样的方式继续扇出并送往不同的子区域;如此往复,直到时钟信号到达最基本的触发器等资源。

可见,时钟树主要利用多级扇出的形式来达到最终的高扇出结果;而通过控制各级扇出后的布线长度尽量一致来保证时钟信号能够尽可能同时到达各个触发器,这就是时钟树工作的基本原理。

时钟树是保证时钟信号到达时钟域内不同触发器的时间差尽可能小的资源,而不是保证时钟信号到达触发器所消耗时间最短的资源。

六、FPGA时钟

1.总体架构

本文以赛灵思7系列FPGA为例,介绍FPGA的时钟资源。

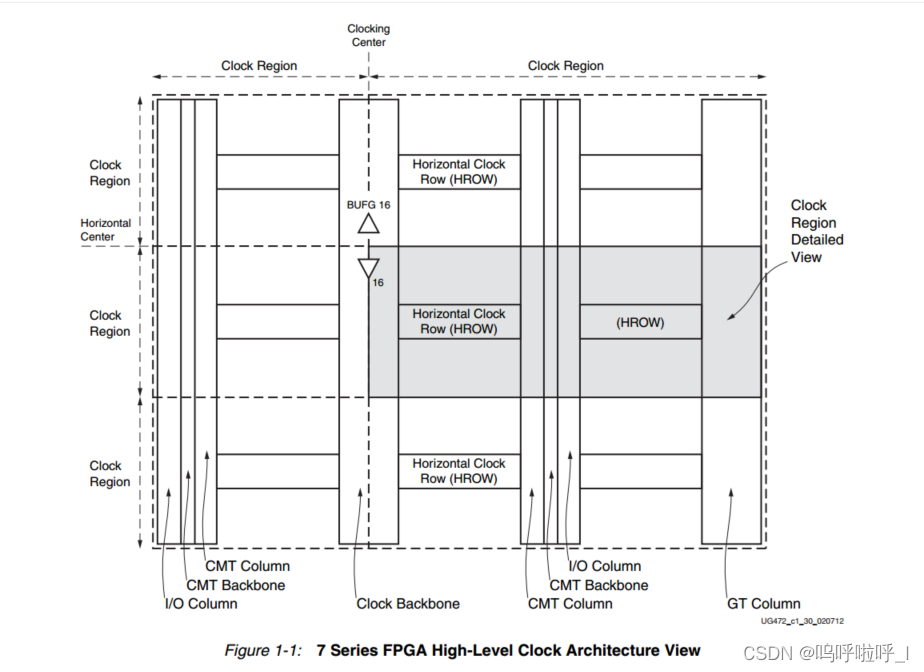

全局时钟树(Global clock tree)跨整个器件提供同步时钟。每个7系列单片设备有32条全局时钟线。

I/O和时钟域时钟树( regional clock tree)最多允许跨3个垂直相邻的时钟域,最多有24个时钟域。

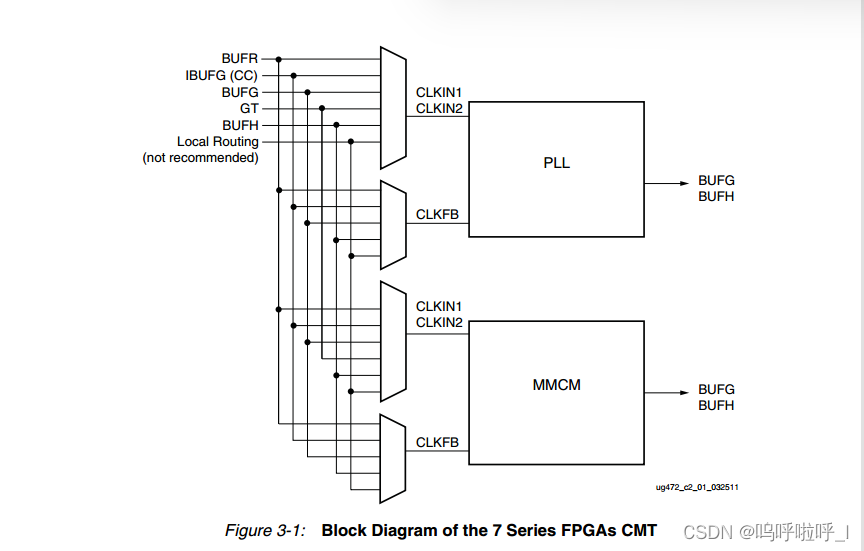

CMT(时钟管理单元)含一个混合模式时钟管理器(mixed-mode clockmanager ,MMCM)和一个锁相环(phase-locked loop,PLL) 。CMT列与I/O列相邻。

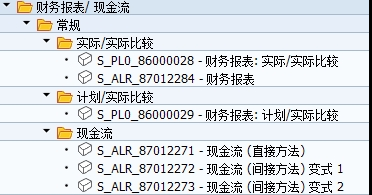

图中有一个水平时钟线HROW,把FPGA分为上半边和下半边,,上边有16个BUFG,下边有16个BUFG。垂直方向上有时钟主干Clock Backbone,将其分为左边和右边,这样就构成了很多时钟域(这里的时钟域并不是跨时钟域处理中的时钟域,二者意义不一样),图中的灰色区域代表一个时钟域。下图是时钟域的基本视图:

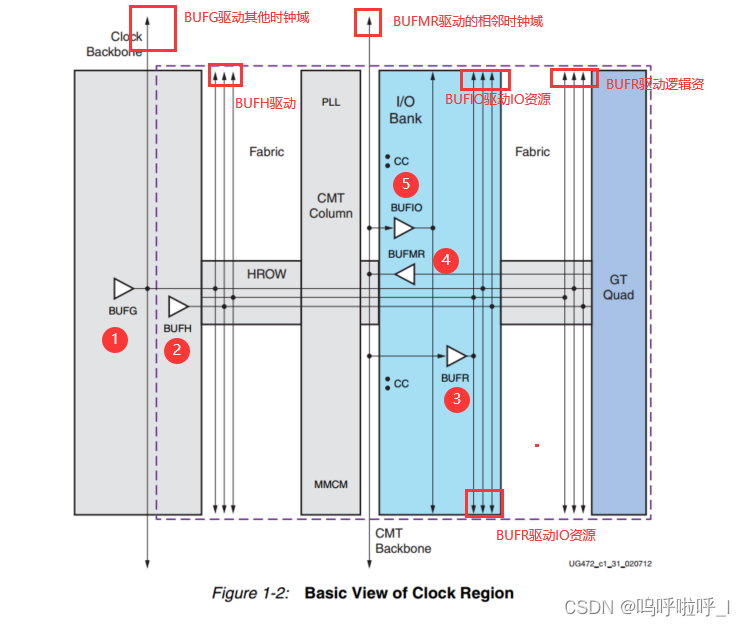

要了解具体细节,我们首先明确五个缓冲器:

- BUFG——全局时钟缓冲

- BUFH——水平时钟缓冲器

- BUFR——区域时钟缓冲器

- BUFMR——多时钟区域缓冲器

- BUFIO—— I/O时钟缓冲器

观察图中五者的位置以及连线情况,我们可以发现:

①BUFG可以通过HROW驱动到每个区域,包括未画出来的上下区域;

②BUFH通过HROW驱动到该区域的每个时钟点;BUFG和BUFH在HROW中共享路由轨迹。

③BUFIO和BUFR位于I/O银行内部,BUFR驱动I/O资源和逻辑资源;

④BUFMR支持BUFIO和BUFR的多区域链接;

⑤BUFIO只驱动I/O时钟资源;

| BUFG | 全局时钟网络 | 输入是IBUFG的输出(合而为BUFGP),位于FPGA器件的中心位置,时钟的输入可以来自FPGA的上、下、左、右的bank,也可以来自PLL或DCM,BUFGMUX通过驱动vertical spine并经vertical spine 往南北方向传播,vertical spine就相当于时钟树的树干。可以驱动所有的IO和逻辑,并且可以被Transceiver所驱动,BUFG输出到达FPGA内部的IOB/CLB、的时钟延迟和抖动最小,但是从普通引脚到全局时钟布线层有一个固有延时约10ns |

| BUFR | 区域时钟网络 | BUFR是区域时钟缓冲器,要进入区域时钟网络,必须例化BUFR。一个BUFR最多可以驱动三个相邻的时钟区域中的区域时钟。顶部和底部区域中BUFR只能连接相邻的一个时钟区域。BUFR还可以1-2-4-8分频。驱动范围只能局限在一个clock region的逻辑,但是它可以同时驱动IO和内部逻辑。BUFR可以被如下节点所驱动:所有能驱动BUFIO的节点;MMCMs clock outputs 0-3;General interconnect。BUFR相比BUFG的最大优势是skew和功耗都比较小 |

| BUFIO | IO时钟网络 | BUFIO是用来驱动I/O列内的专用时钟网络,这个专用的时钟网络独立于全局时钟资源,适合采集源同步数据。BUFIO只能由位于同一时钟区域的Clock-Capable I/O驱动。一个时钟区域有4个BUFIO,其中的2个可以驱动相邻区域的I/O时钟网络。只能驱动IO Block里面的逻辑,不能驱动CLB里面的LUT,REG等逻辑。BUFIO可以被如下节点驱动:SRCCs and MRCCs in the same clockregion;MRCCs in an adjacent clock regionusing BUFMRs;MMCMs clock outputs 0-3 driving theHPC in the same clock region |

| CMT | 时钟管理模块 | 位于FPGA中间竖排,就是PLL和DCM |

| BUFH | 水平时钟缓冲 | 每一个HCLK列(水平时钟线)左右两边各有16个水平时钟缓冲BUFH驱动左右逻辑资源 |

| IBUFG | 输入全局缓冲 | 与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUFG 单元,否则在布局布线时会报错。 IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和 SSTL等多种格式的IO标准。输入全局缓冲有MRCC SECC。其中,SRCC能驱动相同的bank,MRCC能驱动相同、上下bank |

| IBUFGDS | IBUFG差分形式 | 当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准 |

| BUFGCE | 带有时钟使能端的全局缓冲 | 有一个输入I、一个使能端CE和一个输出端O。只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出 |

| BUFGMUX | 全局时钟选择缓冲 | 有I0和I1两个输入,一个控制端S,一个输出端O。当S为低电平时输出时钟为I0,反之为I1。需要指出的是BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系 |

| BUFGDLL | 全局缓冲延迟锁相环 | 相当于BUFG与DLL的结合。BUFGDLL在早期设计中经常使用,用以完成全局时钟的同步和驱动等功能。随着数字时钟管理单元(DCM)的日益完善,目前BUFGDLL的应用已经逐渐被DCM所取代 |

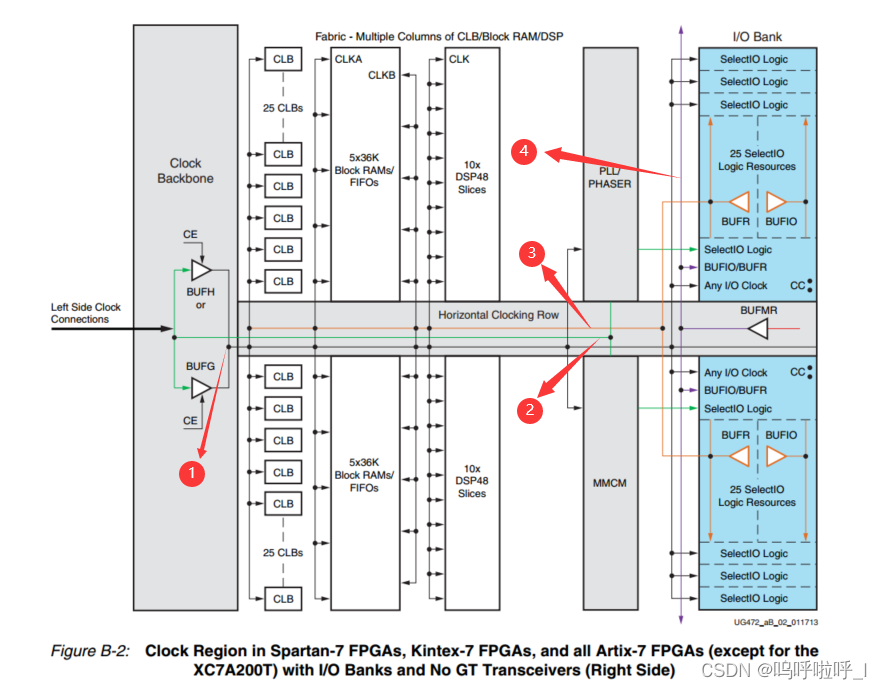

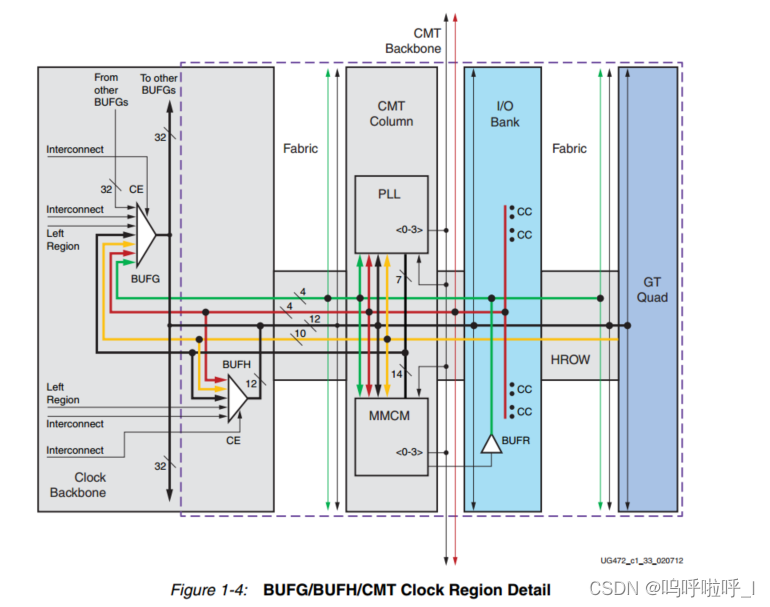

每个时钟域详细结构如下图:

每个FPGA最多包含有24个时钟域。一个时钟区域总是包含50个CLB(上下各25个),10个36K大小的Block RAM(除非5个Block RAM被PCIe的集成块取代),20个DSP片,12个BUFH,1个CMT以及中间一个水平时钟线HROW。每个时钟域最多支持12个全局时钟线。

我们主要看图中的四条线:

①标注的①号黑线由BUFG和BUFH共同驱动,通过观察其连接关系(这条线到达的区域),可知其能够驱动逻辑资源(CLB、RAM、DSP)、MMCM、PLL以及IO时钟资源;

②标注的绿线其表示PLL/MMCM可以驱动BUFG、BUFH、以及IO资源;

③标注的橙色前表示BUFR可以驱动逻辑资源以及IO资源,而BUFIO可以驱动IO资源;

④标注的紫线表示BUFMR可以驱动垂直相邻的其他时钟域以及本时钟域的BUFR和BUFIO;

2.7系列FPGA的BUF资源

(1)BUFG/BUFH/CMT

1.BUFG

从图中可以看出,BUFG的时钟驱动可以由其他时钟域的BUFG(From other BUFGS)驱动,也可以由互连线(Interconnect)、左侧时钟域(Lefr Region)、PLL/MMCM(黑线)、GT(黄线)、CC(输入时钟管脚,红线)、BUFR(绿线)驱动;

2.BUFH

BUFH可以由互连线(Interconnect)、左侧时钟域(Lefr Region)、CC(输入时钟管脚,红线)、PLL/MMCM(黑线)、GT(黄线)驱动;

3.CMT(MMCM/PLL)

CMT可以有BUFG(黑线)、BUFH(黑线)、GT(黄线)、CC(输入时钟管脚,红线)、BUFR(绿线)驱动。CMT可以使用CMT主干驱动相邻区域中的其他CMT,但有限制。同样,CC可以在相同的限制下驱动相邻区域的CMT。

来自一个区域的时钟源可以驱动其所在区域的时钟缓冲资源,也可以驱动水平相邻区域的时钟缓冲资源。CMT、时钟功能引脚CC和串行收发器可以通过BUFH将时钟驱动到水平相邻区域,也可以连接到设备的相同顶部/底部的BUFG。

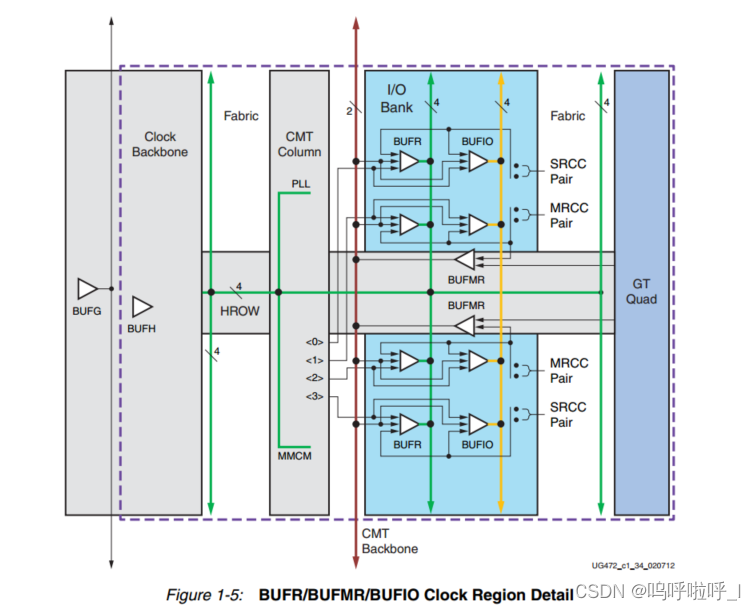

(2)BUFR/BUFMR/BUFIO

每个I/O bank包含4个BUFIO和4个BUFR。

SRCC:单区域时钟输入管脚

MRCC:多区域时钟输入管脚

SRCC进入BUFIO后驱动本IO Bank中的IO管脚;进入BUFR驱动区域时钟网络;

MRCC除了可以驱动BUFR和BUFIO外,还可以驱动BUFMR连接相邻的时钟域;

同时GT的时钟驱动可以通过BUFMR驱动BUFR和BUFIO;

MMCM[3:0]输出具有通往BUFR和BUFIO的专用高性能差分路径。这个特性也被称为高性能时钟(HPC)。

3.CMT(MMCM/PLL)

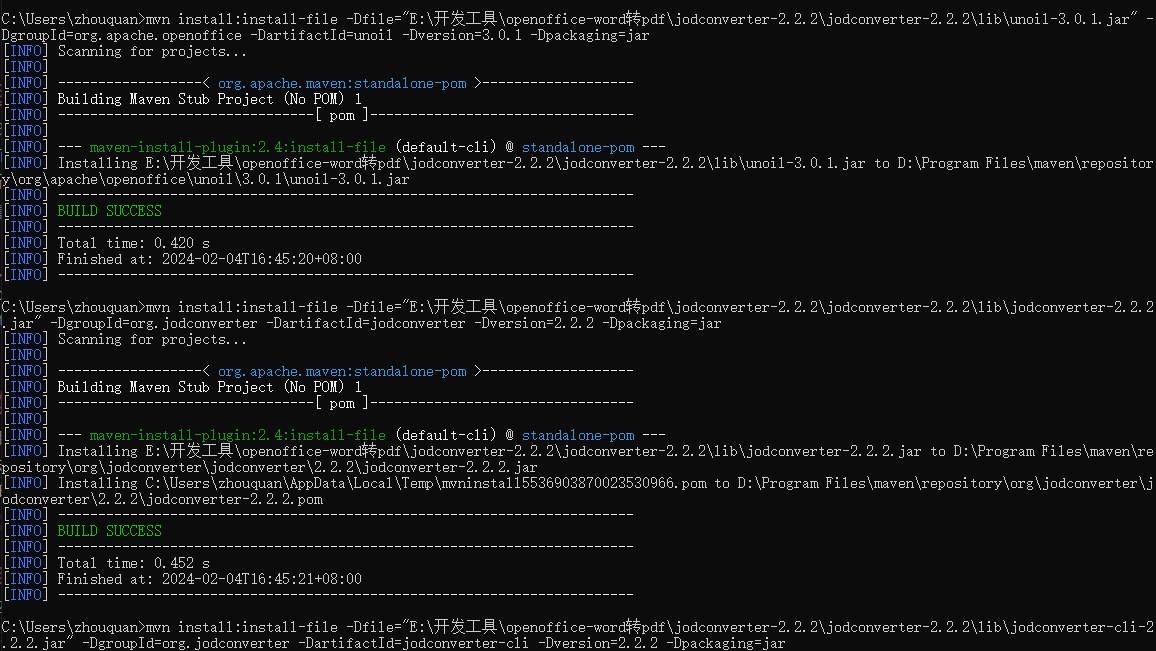

7系列fpga中的PLL是MMCM功能的一个子集,它基于MMCM,而不一定基于以前的PLL设计。

1.MMCM

输入多路复用器从IBUFG、BUFG、BUFR、BUFH、GT(仅限CLKIN)或互连(不推荐)中选择参考时钟和反馈时钟。每个时钟输入都有一个可编程计数器分频器(D)。

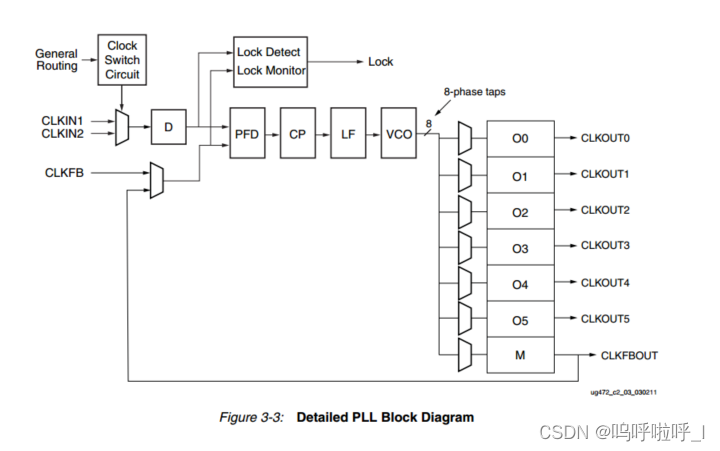

相频检测器(PFD)比较输入(参考)时钟和反馈时钟上升沿的相位和频率。PFD用于产生与两个时钟之间的相位和频率成比例的信号。该信号驱动电荷泵(CP)和环路滤波器(LF)产生一个参考电压到VCO。

PFD产生一个向上或向下的信号到电荷泵和环路滤波器,以确定压控振荡器是否应该在更高或更低的频率下工作。当压控振荡器工作在过高的频率时,PFD会激活一个下降信号,导致控制电压降低,从而降低压控振荡器的工作频率。当压控振荡器工作在过低的频率时,上信号会增加电压。

VCO产生8个输出相位和1个可变相位,用于精细相移。每个输出相位都可以选择作为输出计数器的参考时钟。每个计数器可以独立编程为一个给定的客户设计。还提供了一个特殊的计数器M。该计数器控制MMCM和锁相环的反馈时钟,允许广泛的频率合成。除了整数除输出计数器之外,MMCM还为CLKOUT0和CLKFBOUT添加了一个小数计数器(PLL不具有)。

MMCM具有7路输出,并且前四路还可以输出180度相位差的时钟。此外。第一路输出的时钟还支持小数分频,输出频率范围更大;并且其反馈也有一个小数分频器。

2.PLL

PLL的输出只有六路,并且不具备反相输出。此外也不具备小数分频的功能。

下面给出7系列FPGA时钟资源PDF的链接:

7 Series FPGAs Clocking Resources User Guide

参考文章如下:

非理想时钟的偏差

时钟信号知识点全解析

时钟简介 时钟信号