目录

1. 概述

2. Simulation with AXI VIP

2.1 axi_vip_pkg

2.2 design_1_axi_vip_0_0_pkg

2.3 参数指定

3. 实例化注意事项

3.1 名称对应关系

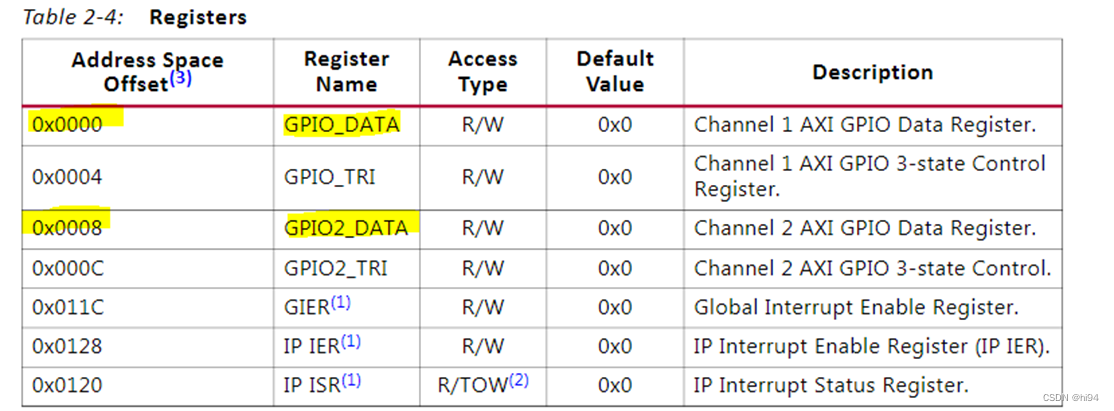

3.2 寄存器地址

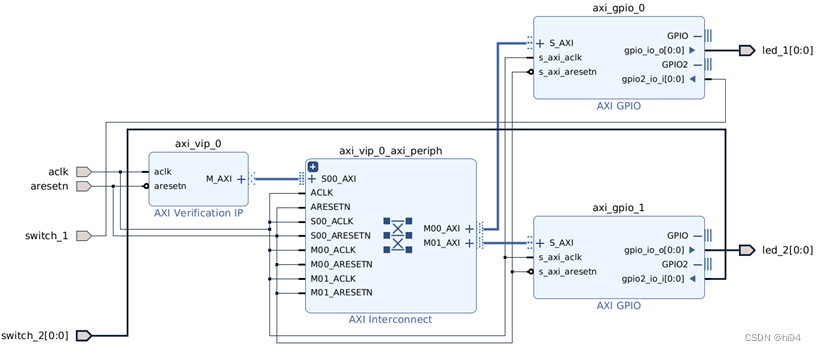

3.3 block design

1. 概述

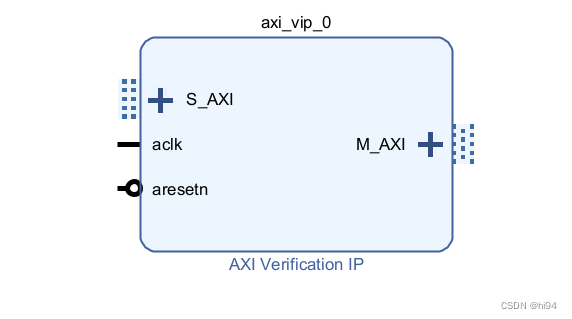

AXI Verification IP(AXI VIP)是一种用于验证AXI总线协议的仿真工具,可帮助开发人员在设计阶段发现和解决潜在的硬件设计问题。通过使用AXI VIP,用户可以在仿真环境中模拟AXI总线的行为,验证设计的正确性和性能。

它只是一个仿真IP,不会被综合到最终的硬件中。

2. Simulation with AXI VIP

首先需要导入两个SystemVerilog包。类似于python中的导入。两者都用于导入代码中定义的函数、参数、类等,以便在当前文件中使用。

在SystemVerilog中,包是一种封装数据类型、任务和函数的机制,通常用于在不同的模块间共享。而Python的模块和包是文件和文件夹的集合,用于组织和重用代码。

import axi_vip_pkg::*; // 系统自带:<loc>/Vivado/2022.1/data/xilinx_vip/hdl/axi_vip_pkg.sv

import design_1_axi_vip_0_0_pkg::*; //在工程目录中

我在注释中标注了包的具体位置,可以查看该包的具体行为。

2.1 axi_vip_pkg

定义了一个名为 axi_mst_agent 的SystemVerilog类,继承自 xil_agent。

宏定义:AXI_PARAM_DECL 是一个宏定义。

类扩展:axi_mst_agent 类通过 AXI_PARAM_DECL 宏应用这些参数,并扩展了 xil_agent 类。

组件实例化:

monitor:用于监控AXI总线上的事务。

wr_driver:用于驱动AXI总线上的写操作。

rd_driver:用于驱动AXI总线上的读操作。

构造函数:new 函数是类的构造函数,用于创建 axi_mst_agent 实例。它初始化了监控器、写驱动器、读驱动器,并将虚拟接口与代理关联起来。

虚拟接口:axi_vip_if 是一个虚拟接口,它允许 axi_mst_agent 与AXI总线的物理信号进行交互。

代理设置:vif_proxy 是一个代理,用于将虚拟接口的操作映射到物理接口。这允许在仿真环境中模拟实际的硬件行为。

<axi_vip_pkg.sv> 中定义的 axi_mst_agent 类,继承自xil_agent`define AXI_PARAM_DECL #( //宏定义int C_AXI_PROTOCOL=0,C_AXI_ADDR_WIDTH=32, C_AXI_WDATA_WIDTH=32,C_AXI_RDATA_WIDTH=32,C_AXI_WID_WIDTH=0,…)class axi_mst_agent `AXI_PARAM_DECL extends xil_agent;axi_monitor `AXI_PARAM_ORDER monitor;axi_mst_wr_driver `AXI_PARAM_ORDER wr_driver;…function new (string name = "unnamed_axi_mst_agent",virtual interface axi_vip_if `AXI_PARAM_ORDER vif);super.new(name); //调用其基类的构造函数this.monitor = new($sformatf("%s_monitor",name));this.wr_driver = new($sformatf("%s_wr_driver",name));this.rd_driver = new($sformatf("%s_rd_driver",name));this.vif_proxy = new($sformatf("%s_vif",name));this.vif_proxy.assign_vi(vif);this.set_vif(this.vif_proxy);endfunction : new // axi_mst_agent类构造函数

…

endclass : axi_mst_agent

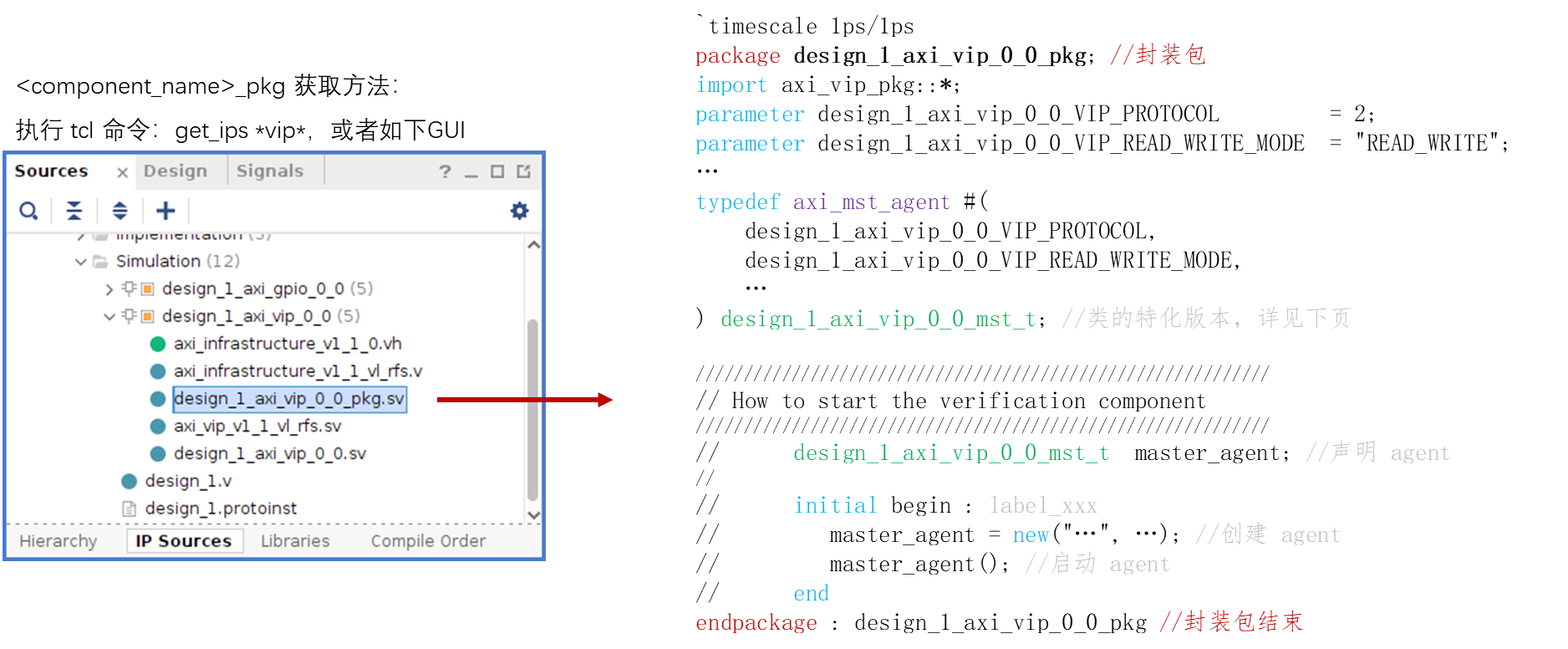

2.2 design_1_axi_vip_0_0_pkg

定义了一个封装包,其中包含了一些参数和类型定义,用于配置和实例化AXI VIP组件。

首先,在package中定义了一些参数,如VIP_PROTOCOL和VIP_READ_WRITE_MODE,用于指定AXI VIP的协议和读写模式。

然后,通过typedef关键字定义了一个名为design_1_axi_vip_0_0_mst_t的类型,该类型是axi_mst_agent类的特化版本,根据之前定义的参数进行特化。

启动验证组件的示例代码:

首先声明了一个名为master_agent的design_1_axi_vip_0_0_mst_t类型的对象,然后在initial块中创建并启动了这个agent。通过实例化和启动这个agent,可以开始对AXI VIP进行仿真测试。最后,使用endpackage关键字结束了这个封装包的定义。

2.3 参数指定

SystemVerilog中,类并不直接支持像C++或Java中的模板化(泛型)编程,但它允许你创建参数化的类,这些参数通过顺序指定。如下:

// <component_name>_pkgparameter design_1_axi_vip_0_0_VIP_PROTOCOL = 2;

parameter design_1_axi_vip_0_0_VIP_READ_WRITE_MODE = "READ_WRITE";

parameter design_1_axi_vip_0_0_VIP_INTERFACE_MODE = 0;

parameter design_1_axi_vip_0_0_VIP_ADDR_WIDTH = 32;

parameter design_1_axi_vip_0_0_VIP_DATA_WIDTH = 32;

…typedef axi_mst_agent #(design_1_axi_vip_0_0_VIP_PROTOCOL, design_1_axi_vip_0_0_VIP_ADDR_WIDTH,design_1_axi_vip_0_0_VIP_DATA_WIDTH,design_1_axi_vip_0_0_VIP_DATA_WIDTH,design_1_axi_vip_0_0_VIP_ID_WIDTH,…

) design_1_axi_vip_0_0_mst_t;

3. 实例化注意事项

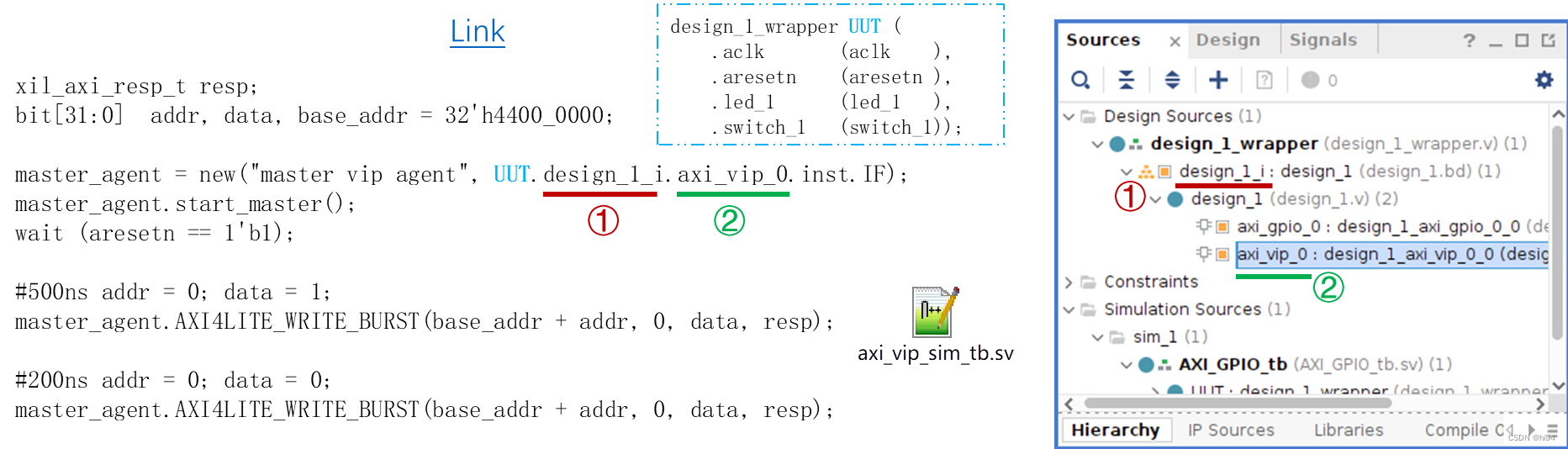

3.1 名称对应关系

3.2 寄存器地址

3.3 block design