文章目录

- 前言

- 一、模块接口

- 二、IP模块与ARP模块之间的联系

- 三、整体协议栈仿真

- 总结:

前言

目前除了巨帧处理逻辑之外,所有的准备工作都已经结束了,先进行整体的功能验证。

一、模块接口

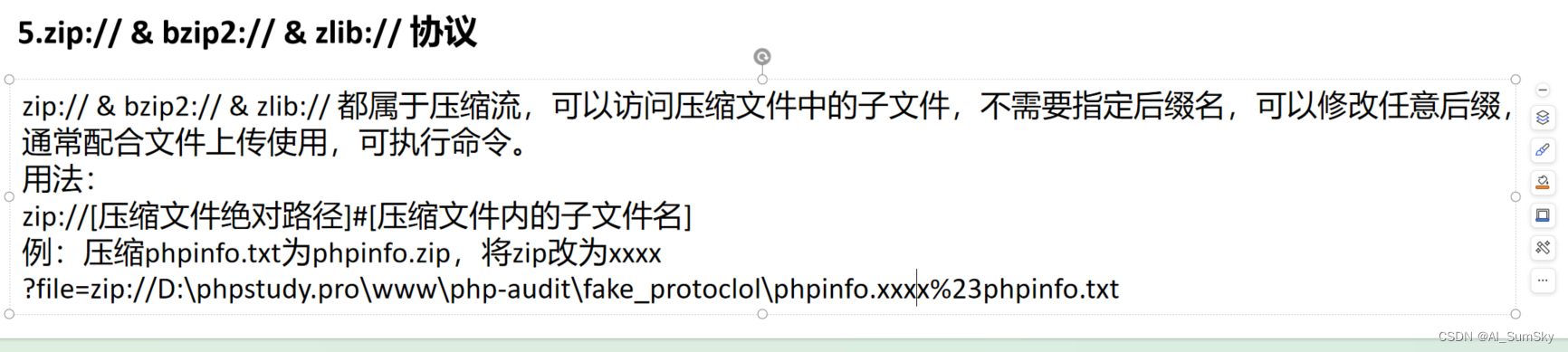

所有模块接口皆采用AXIS数据流的形式,其中包括一个用户自定义信号axis_ip_user,该信号当中存有数据的长度信息,我进行了统一的修改,该长度信息全部是指数据当中的字节长度,所以在处理数据的时候,需要考虑将字节长度信息转化为传输周期长度,即64bit的数量(一拍时钟传输64bit)。

以IP_TX模块为例,r_pkt_byte_len表示数据当中的字节数目,w_ip_64bit_len 表示64bit数据的长度。转化过程也很简单,字节长度右移3位即可,然后判断一下低3位是否为零,不为领则需要多加一个时钟周期进行传输。

assign w_ip_64bit_len = r_pkt_byte_len[2:0] == 0 ? (r_pkt_byte_len >> 3): (r_pkt_byte_len >> 3) + 1 ;

二、IP模块与ARP模块之间的联系

当IP层收到上层的数据包后,就会根据当前的目的IP向ARP发送一个MAC查找,当找到对应MAC地址后就会开始传输数据,但如果没有找到,那么就会先把数据存下来,然后触发ARP请求,通知ARP发送模块发送一个ARP请求,当获取到相应的NAC地址后,整个协议栈开始正常工作。

整个FPGA也可以在上电的时候进行一次主动ARP移获取对端主机的MAC地址,而且电脑在FPGA上电后也会进行主动ARP,此时FPGA也会获取到主机的MAC信息的。

//当有数据要发送时,进行MAC查询

always @(posedge i_clk or posedge i_rst)beginif(i_rst)ro_seek_ip <= 'd0;elsero_seek_ip <= r_dynamic_dst_ip;

endalways @(posedge i_clk or posedge i_rst)beginif(i_rst)ro_seek_ip_valid <= 'd0;else if((s_axis_upper_valid && !rs_axis_upper_valid) || (r_get_mac_faild))ro_seek_ip_valid <= 'd1;elsero_seek_ip_valid <= 'd0;

end//获得查询结果

always @(posedge i_clk or posedge i_rst)beginif(i_rst)ri_seek_mac <= 'd0;else if(i_seek_mac_valid)ri_seek_mac <= i_seek_mac;elseri_seek_mac <= ri_seek_mac;

end//当查询结果为48'hffffffffffff时,说明没有该IP对应的MAC,需要触发一次arp请求

always @(posedge i_clk or posedge i_rst)beginif(i_rst)r_get_mac_faild <= 'd0;else if(i_seek_mac_valid && (&i_seek_mac))r_get_mac_faild <= 'd1;else if(i_seek_mac_valid && !(&i_seek_mac))r_get_mac_faild <= 'd0;elser_get_mac_faild <= r_get_mac_faild;

endalways @(posedge i_clk or posedge i_rst)beginif(i_rst)ro_arp_active <= 'd0;else if(r_get_mac_faild && !r_get_mac_faild_1d)ro_arp_active <= 'd1;elsero_arp_active <= 'd0;

endalways @(posedge i_clk or posedge i_rst)beginif(i_rst)ro_arp_active_dst_ip <= 'd0;else if(r_get_mac_faild && !r_get_mac_faild_1d)ro_arp_active_dst_ip <= ro_seek_ip;elsero_arp_active_dst_ip <= ro_arp_active_dst_ip;

end

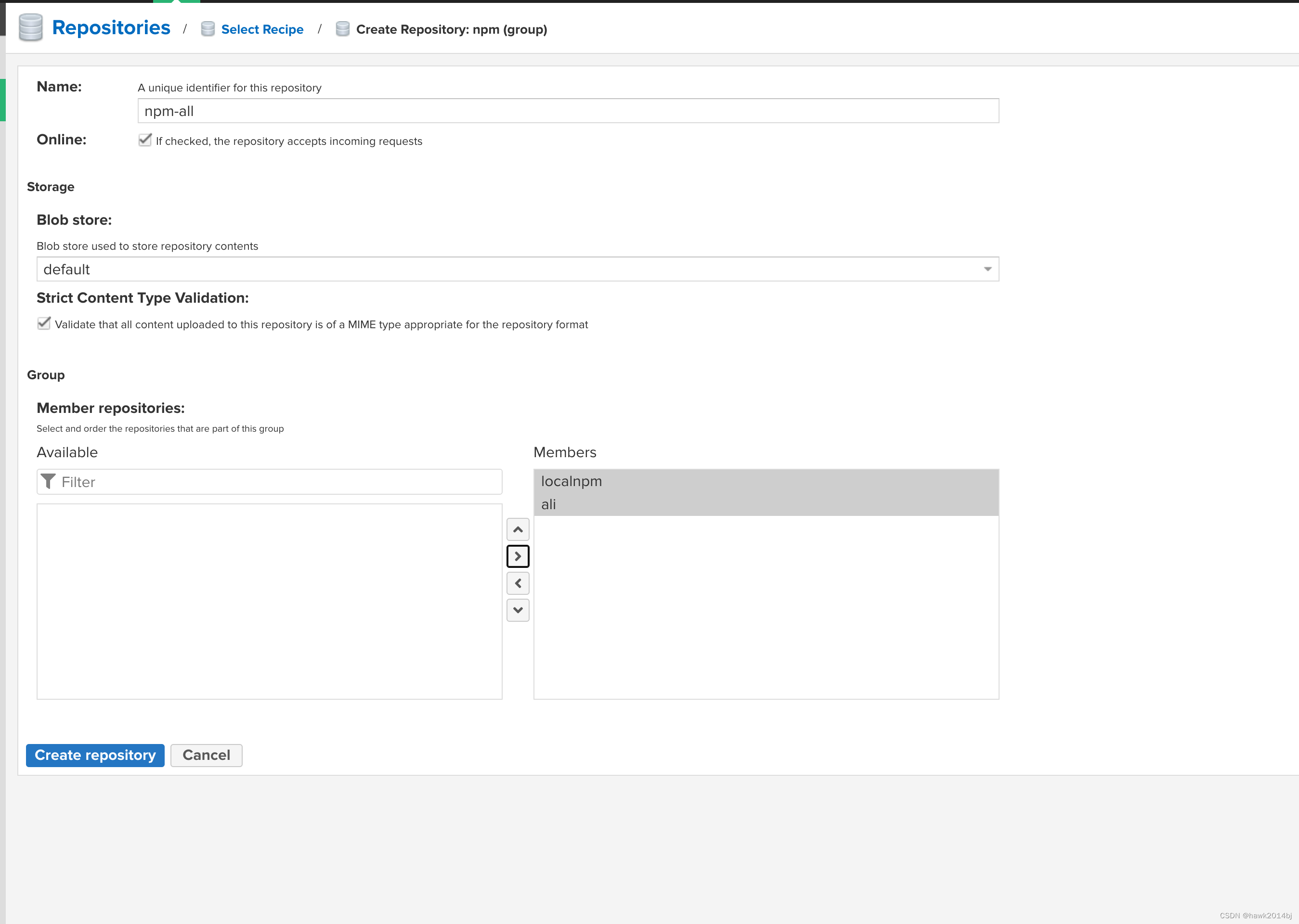

三、整体协议栈仿真

我们只看发送的原始数据,和最终接收的数据。

UDP发送端,先发送了俩个数据,此时IP层会发现没有MAC地址信息,所以会通知上层暂停,开始进行ARP请求,直到获得目的MAC后,UDP层开始继续发送数据。

对于接收端而言,接收到的UDP数据包是连续的,对发端对比,数据无误。

总结:

完整工程参考:https://github.com/shun6-6/Ten_gig_eth_design