名称:基于FPGA的数字密码锁电路Verilog代码Quartus仿真(文末获取)

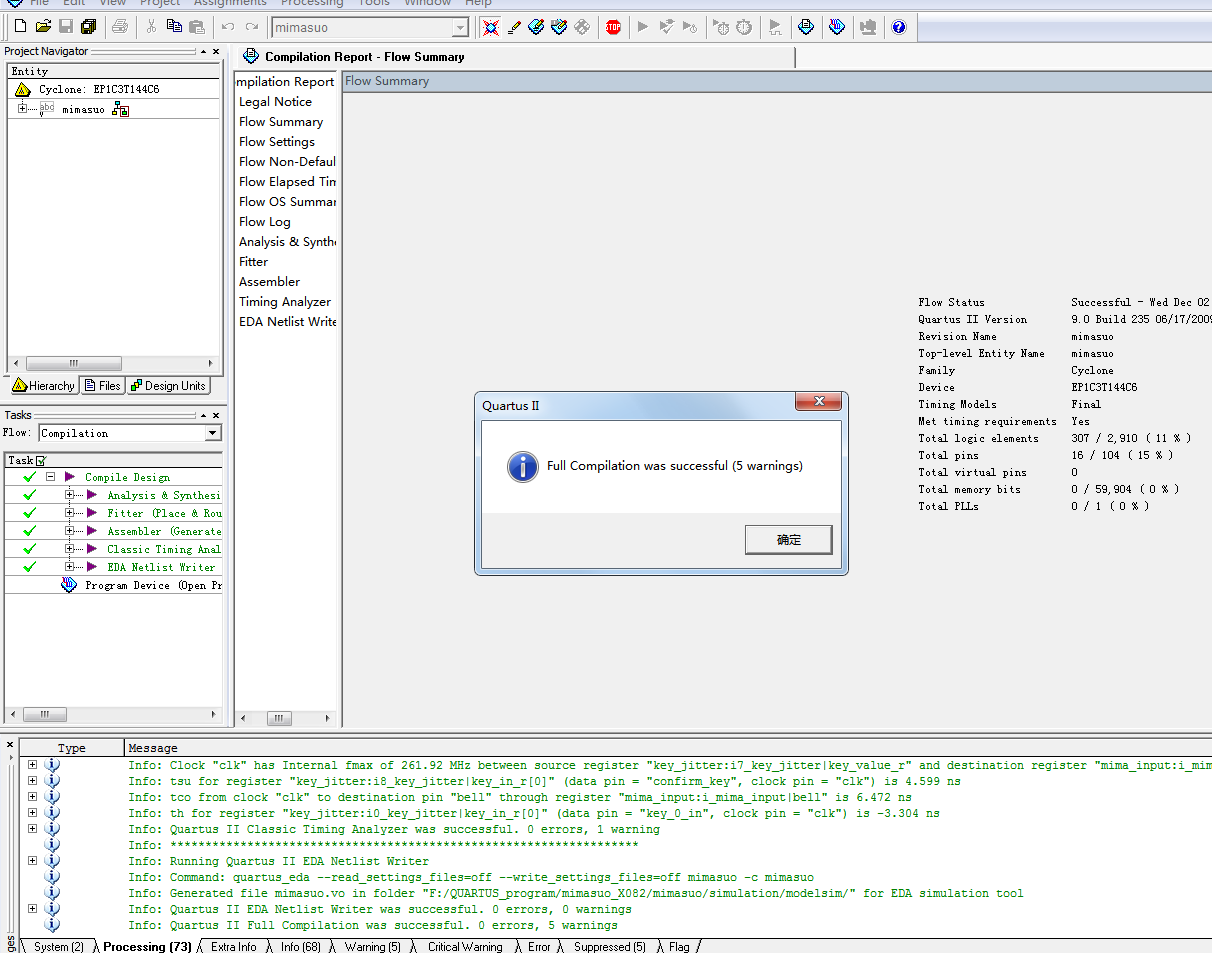

软件:Quartus

语言:Verilog

代码功能:

数字密码锁电路的设计

1.设计任务:设计并制作数字密码锁电路

2.设计要求

1.用EDA实训仪的I/设备和PLD志片实现故字密码锁电路的设计

2.数字码锁具有8只输入数字,用EDA实仪上的电平开关作为8位数字输入的组合

3.当输入的数字符合电路中设定的数字时(和密码对)在EDA实训仪上用一只八段

数码管显示0表示输入整砂正确,如果输入的密码是错误的,则显示F

4.数字码锁又能允许接收三次错误的密码数字输入,超过三次的错误密码数字后电路不再接牧密码数字入,并用喇叭发出报警音响

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. 管脚分配

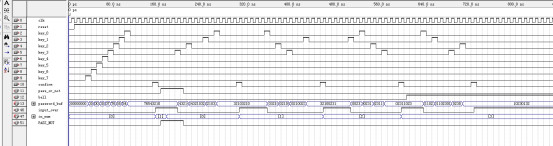

6. Vwf文件

7. 仿真图

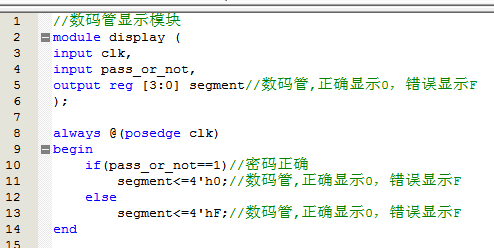

部分代码展示:

module mimasuo( input clk,//时钟 input reset,//复位,按下低电平 input key_0_in,//数字按键0~7 input key_1_in,//数字按键0~7 input key_2_in,//数字按键0~7 input key_3_in,//数字按键0~7 input key_4_in,//数字按键0~7 input key_5_in,//数字按键0~7 input key_6_in,//数字按键0~7 input key_7_in,//数字按键0~7 input confirm_key,//确认按键,代表密码输入完成,按下低电平 output bell,//报警 //结果在数码管中显示 output [3:0] segment//数码管 ); wire key_0; wire key_1; wire key_2; wire key_3; wire key_4; wire key_5; wire key_6; wire key_7; wire confirm; wire pass_or_not;//1表示正确,0表示错误 //输入按键消抖 key_jitter i0_key_jitter( . clkin(clk), . key_in(key_0_in),//输入 . key_negedge(key_0)//消抖后按键 ); key_jitter i1_key_jitter( . clkin(clk), . key_in(key_1_in),//输入 . key_negedge(key_1)//消抖后按键 ); key_jitter i2_key_jitter( . clkin(clk), . key_in(key_2_in),//输入 . key_negedge(key_2)//消抖后按键 ); key_jitter i3_key_jitter( . clkin(clk), . key_in(key_3_in),//输入 . key_negedge(key_3)//消抖后按键 ); key_jitter i4_key_jitter( . clkin(clk), . key_in(key_4_in),//输入 . key_negedge(key_4)//消抖后按键 ); key_jitter i5_key_jitter( . clkin(clk), . key_in(key_5_in),//输入 . key_negedge(key_5)//消抖后按键 ); key_jitter i6_key_jitter( . clkin(clk), . key_in(key_6_in),//输入 . key_negedge(key_6)//消抖后按键 );

源代码

扫描文章末尾的公众号二维码