文章目录

- 第一章:感知机的局限性

- 1.1 异或门的挑战

- 1.2 线性与非线性问题

- 第二章:多层感知机

- 2.1 已有门电路的组合

- 2.2 实现异或门

- 第三章:从与非门到计算机

文章文上下两节

- 从简单逻辑到复杂计算:感知机的进化与其在现代深度学习和人工智能中的应用(上)

- 从简单逻辑到复杂计算:感知机的进化与其在现代深度学习和人工智能中的应用(下)

第一章:感知机的局限性

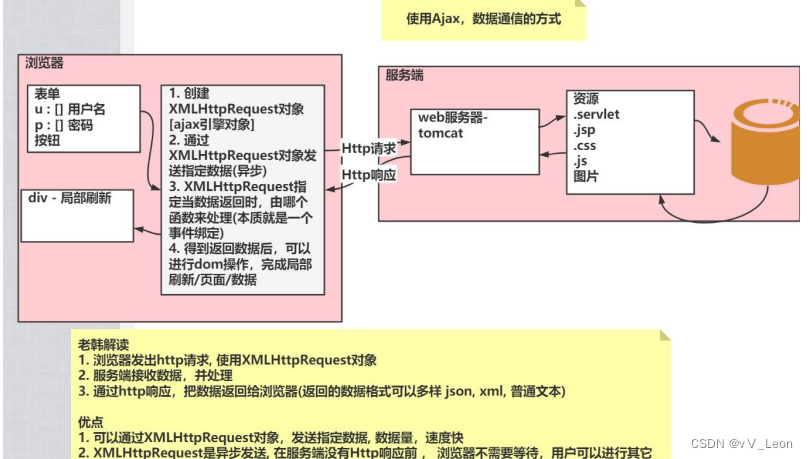

在前几章中,我们已经看到了感知机如何有效地实现基本的逻辑门,如与门、与非门和或门。然而,当我们尝试用感知机实现更复杂的逻辑门,例如异或门(XOR gate),我们遇到了一些困难。本章将探讨感知机的这些局限性,并解释为什么它们存在。

1.1 异或门的挑战

异或门是一种逻辑电路,只有当其中一个输入为1时,输出才为1。这种操作在逻辑中被称为"异或"(XOR),意味着两个输入不同时才为真。以下是异或门的真值表,展示了其输出行为:

实际上,用基本的单层感知机模型无法实现这个异或门。为什么可以用感知机实现与门和或门,但不能实现异或门呢?我们可以通过画图来探索这一问题。

假设我们试图使用以下感知机公式来模拟或门的行为,其参数为 b = − 0.5 b=−0.5 b=−0.5, w 1 = 1.0 w_1=1.0 w1=1.0, w 2 = 1.0 w_2=1.0 w2=1.0

y = { 0 if ( − 0.5 + x 1 + x 2 ≤ 0 ) 1 if ( − 0.5 + x 1 + x 2 > 0 ) y = \begin{cases} 0 & \text{if } (-0.5 + x_1 + x_2 \leq 0) \\ 1 & \text{if } (-0.5 + x_1 + x_2 > 0) \end{cases} y={01if (−0.5+x1+x2≤0)if (−0.5+x1+x2>0)

这个感知机会产生一个决策边界,如下图所示,这条直线将输入空间分为两部分:一部分输出0,另一部分输出1。下面的直线即为 − 0.5 + x 1 + x 2 = 0 −0.5+x_1+x_2=0 −0.5+x1+x2=0,灰色区域是感知机输出0的区域,这个区域与或门的性质一致。对于或门,当输入为 (0,0) 时输出为 0;而当输入为 (1,0),(0,1),或 (1,1) 时,输出为 1。下图显示了这些点和决策边界,其中圆圈表示输出0,三角形表示输出1。

如果我们尝试使用类似的方法来解决异或问题,我们会发现没有单条直线能完美地分离输出为1和输出为0的点。以下是异或操作的可视化,显示了无法仅用一条直线来分割输出1和输出0的区域。

这说明基本的单层感知机无法处理异或问题,这是因为异或是一个非线性问题,而单层感知机只能解决线性可分问题。这展示了单层感知机的一个主要局限性:它无法解决非线性问题。

1.2 线性与非线性问题

在上面我们看到,无论如何尝试,用一条直线都无法完美地区分所有的○和△符号。这突显出了单层感知机处理复杂逻辑函数,如异或(XOR)函数的局限性。

异或门的输出不能通过单层感知机处理,因为它要求非线性的决策边界。如下图所示,一个可能的解决方案是使用曲线来分隔输出为1和输出为0的区域。这样的曲线无法通过单层感知机来实现,因为单层感知机的决策边界总是线性的(即由直线描述)。

在机器学习中,线性空间和非线性空间的区别极为关键。线性模型,如单层感知机,只能解决线性可分问题,即那些可以通过一个平面或直线分隔的问题。然而,许多实际问题,如异或问题,是非线性的,需要通过更复杂的模型如多层感知机来解决。

第二章:多层感知机

感知机不能表示异或门让人深感遗憾,但也无需悲观。实际上,感知机的绝妙之处在于它可以“叠加层”(通过叠加层来表示异或门是本节的要点)。这里,我们暂且不考虑叠加层具体是指什么,先从其他视角来思考一下异或门的问题。

2.1 已有门电路的组合

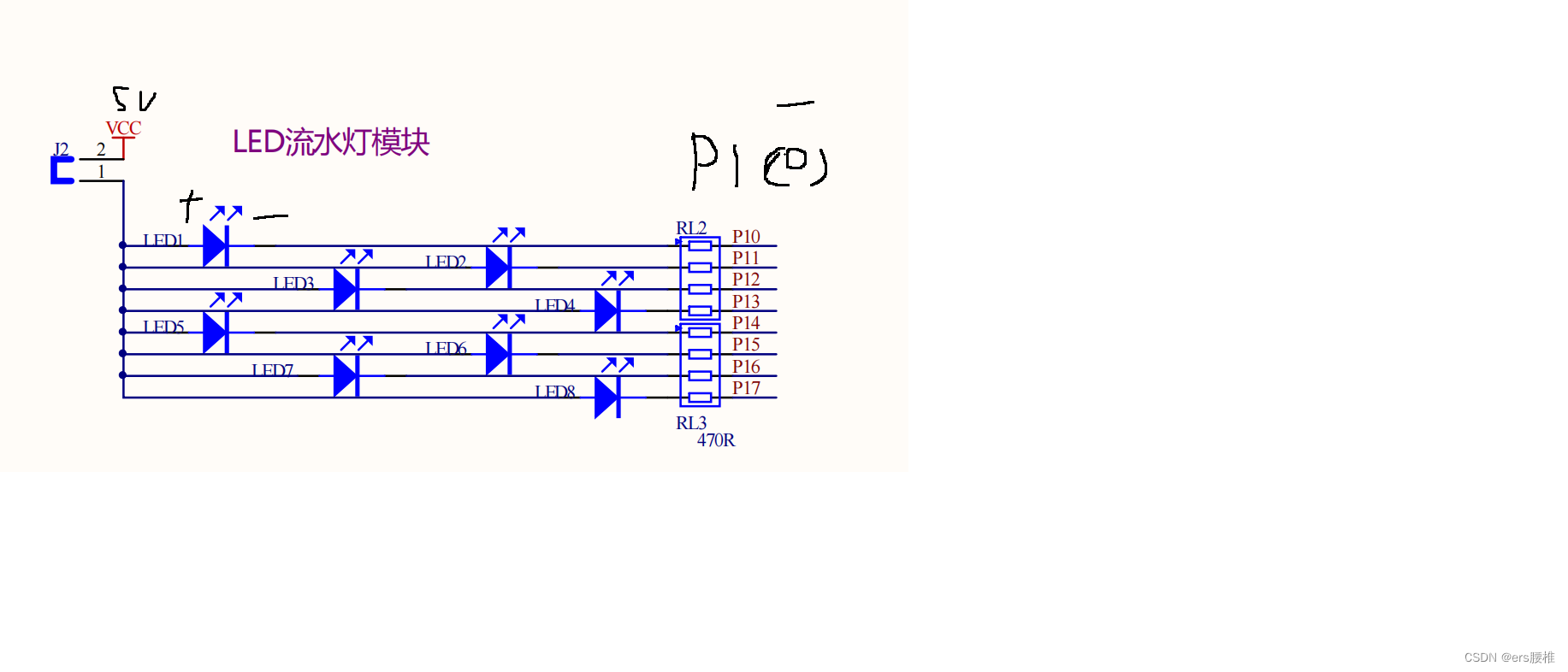

异或门的制作方法有很多,其中之一就是组合我们前面做好的与门、与非门、或门进行配置。下图展示了与门、与非门、或门的符号表示。图中与非门前端的圆圈表示反转输出的意思。

要实现异或门的话,需要如何配置与门、与非门和或门呢?

严格地讲,感知机的局限性应该描述为“单层感知机无法表示异或门”或者“单层感知机无法分离非线性空间”。但通过组合感知机(叠加层)就可以实现异或门。

异或门可以通过下图所示的配置来实现。这里, x 1 x_1 x1 和 x 2 x_2 x2 表示输入信号, y y y 表示输出信号。 x 1 x_1 x1 和 x 2 x_2 x2 是与非门和或门的输入,而与非门和或门的输出则是与门的输入。

这里把 s 1 s_1 s1 作为与非门的输出,把 s 2 s_2 s2 作为或门的输出,填入真值表中。结果如下图所示,观察 x 1 x_1 x1、 x 2 x_2 x2、 y y y,可以发现确实符合异或门的输出。

2.2 实现异或门

下面我们试着用Python来实现异或门。使用之前定义的AND函数、NAND函数、OR函数,可以像下面这样实现。

def XOR(x1, x2):s1 = NAND(x1, x2)s2 = OR(x1, x2)y = AND(s1, s2)return y

这个XOR函数会输出预期的结果。

XOR(0, 0)输出 0XOR(1, 0)输出 1XOR(0, 1)输出 1XOR(1, 1)输出 0

这样,异或门的实现就完成了。下面我们试着用感知机的表示方法(明确地显示神经元)来表示这个异或门,结果如下图所示。异或门是一种多层结构的神经网络。这里,将最左边的一列称为第0层,中间的一列称为第1层,最右边的一列称为第2层。

上图中的感知机总共由3层构成,但是因为拥有权重的层实质上只有2层(第0层和第1层之间,第1层和第2层之间),所以称为“2层感知机”。不过,有的文献认为上图的感知机是由3层构成的,因而将其称为“3层感知机”。

在上图所示的2层感知机中,先在第0层和第1层的神经元之间进行信号的传送和接收,然后在第1层和第2层之间进行信号的传送和接收,具体如下所示:

- 第0层的两个神经元接收输入信号,并将信号发送至第1层的神经元。

- 第1层的神经元将信号发送至第2层的神经元,第2层的神经元输出 y y y。

这种2层感知机的运行过程可以比作流水线的组装作业。第1段(第1层)的工人对传送过来的零件进行加工,完成后再传送给第2段(第2层)的工人。第2层的工人对第1层的工人传过来的零件进行加工,完成这个零件后出货(输出)。

像这样,在异或门的感知机中,工人之间不断进行零件的传送。通过这样的结构(2层结构),感知机得以实现异或门。这可以解释为“单层感知机无法表示的东西,通过增加一层就可以解决”。也就是说,通过叠加层(加深层),感知机能进行更加灵活的表示。

第三章:从与非门到计算机

多层感知机展示了其在实现复杂电路方面的强大能力,不仅限于基本逻辑门,如与门或或门,甚至可以扩展到更复杂的功能,例如加法器和编码器。这些设备通常需要多步骤的逻辑处理,通过感知机模型,我们可以构建这些复杂的逻辑函数。

计算机与感知机的相似性

感知机的基本工作原理 —— 接收输入,处理数据后输出结果 —— 在很大程度上模仿了计算机的操作。这种简单的对比帮助我们理解,即使是最复杂的计算机系统,其核心也依赖于基础的逻辑处理单元。

与非门的强大作用

在数字电路设计中,与非门的重要性不容小觑。事实上,仅仅使用与非门,就可以构建任何其他的逻辑门,进而实现完整的计算机处理能力。这种从简到繁的能力展示了感知机在逻辑设计中的潜力。

感知机与计算机架构

尽管理论上两层感知机就足以模拟任何计算功能,实际上要通过这种方式实现一个高效的计算机架构是非常困难的。例如,创建一个使用激活函数的多层感知机来精确模拟ALU或CPU的行为,这在理论上是可行的,但在实践中可能需要极其复杂的网络结构和精细的权重调整。

分阶段实现的逻辑复杂性

在实际的硬件设计中,构建一个计算机通常涉及多个阶段,每个阶段完成特定功能的组件,如逻辑门、加法器、算术逻辑单元(ALU),最终组合成完整的CPU。这种分阶段的方法可以为感知机的实用应用提供框架,即通过分层逐步增加网络的复杂性来逼近所需的功能。

总结

尽管多层感知机理论上可以模拟复杂的计算机系统,但实际应用中,它们更常见于模拟具体功能或处理特定类型的数据。感知机的这种适用性和灵活性,使其在现代计算和机器学习领域中成为了一个宝贵的工具。同时,了解感知机如何模拟基本计算机操作也对深入理解计算机运作和优化现有技术架构提供了洞见。

上一节:从简单逻辑到复杂计算:感知机的进化与其在现代深度学习和人工智能中的应用(上)