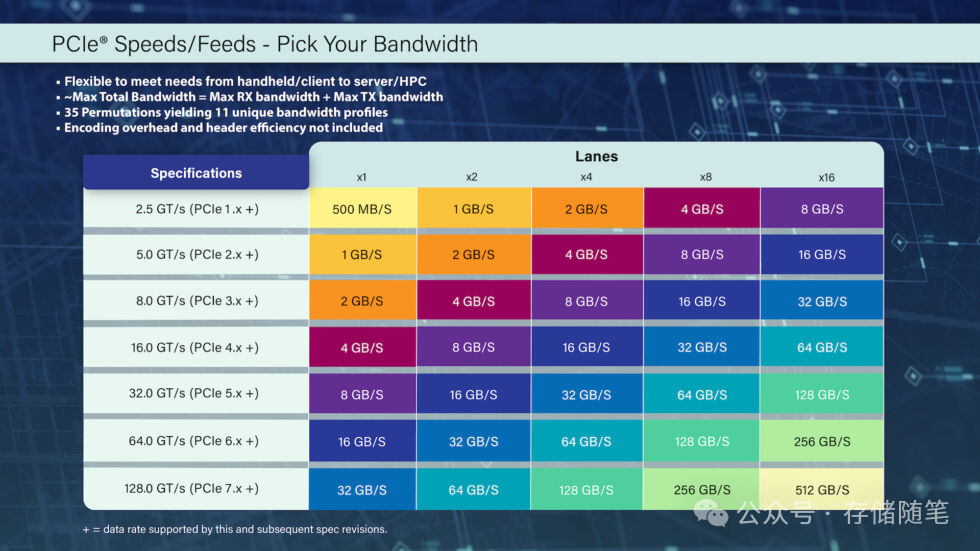

作为业界广泛采用的高速串行点对点互联标准,PCIe自诞生以来历经多次迭代升级,现已成为CPU、GPU、FPGA、SSD等计算设备间不可或缺的互连桥梁。PCIe 7.0标准更是将数据传输速率提升至令人惊叹的32 GB/s(每通道)。

然而,面对数据爆炸式增长与延迟敏感型应用的需求,PCIe面临多项挑战。尽管PCIe 7.0的带宽较上一代翻倍,但面对未来TB/s级别的数据传输需求,仍有可能捉襟见肘。尽管PCIe协议优化了延迟表现,但在大规模数据中心内部,距离延长与互连层级增加会导致延迟累积。随着数据速率提升,互连功耗问题日益突出,对整体能效与散热设计构成挑战。

扩展阅读:

-

CXL与PCIe世界的尽头|你相信光吗?

-

PCIe 7.0|不要太卷,劝你先躺平

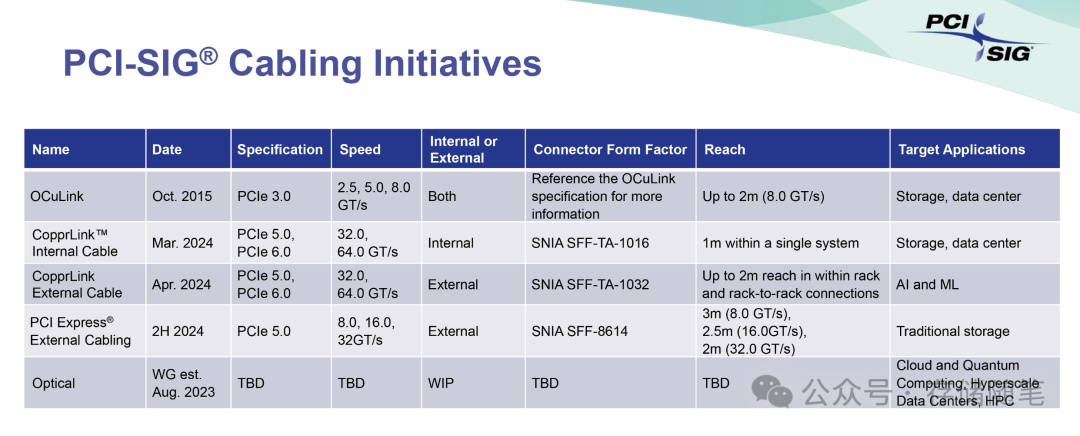

随着PCI Express (PCIe) 线缆应用领域的不断扩大,PCI-SIG持续跟进行业需求,致力于开发高速线缆解决方案。近日,PCI-SIG宣布正式发布CopprLink内部及外部电缆规范。CopprLink电缆规范支持32.0 GT/s和64.0 GT/s的信号传输速度,并采用了由SNIA维护的成熟行业标准连接器外形尺寸。

PCI-SIG主席兼主席Al Yanes表示:“CopprLink电缆规范无缝集成了PCIe布线与PCIe电气基础规范,提供了更长的通道范围和拓扑灵活性。CopprLink电缆旨在与相同的连接器外形尺寸一同进化,为未来的PCIe技术世代扩展规模,并满足新兴应用的需求。电气工作组已经开始针对128.0 GT/s的PCIe 7.0技术进行CopprLink电缆的前瞻研究,彰显了PCI-SIG对CopprLink电缆规范的承诺。”

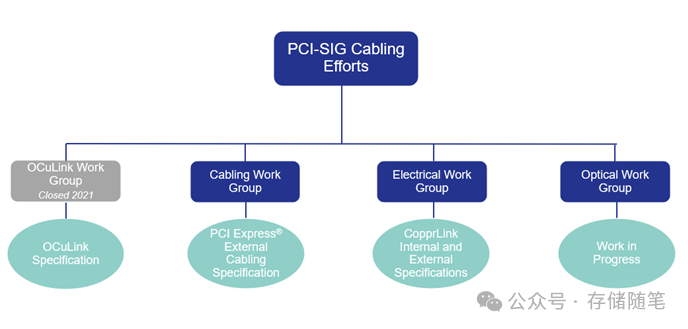

自2003年起,PCI-SIG启动了Cabling Work Group(线缆工作组),旨在定义外部线缆组件及其连接器的要求,以促进2.5 GT/s下PCIe链路的可扩展性。Cabling Work Group一直与PCI Express Base Specification(PCIe基础规范)并行发展,不断更新规范。2015年,为了标准化内部和外部PCIe线缆连接的平台架构,创建了OCuLink Workgroup,旨在支持2.5、5.0和8.0 GT/s速率。

然而,随着PCIe基础规范的迅速发展,OCuLink Workgroup面临挑战,难以跟上步伐满足新平台需求,最终于2021年关闭。尽管如此,PCI-SIG成员仍可查阅OCuLink规范,市面上也有OCuLink解决方案在售。同年,鉴于PCIe 5.0及更高版本技术的行业需求变化,PCI-SIG认识到开发更符合行业需求的线缆新标准的重要性。

PCI-SIG正从多个方面应对行业线缆需求,遵循“按需选择速度与带宽”的理念,确保行业可根据应用需求选择最合适的PCIe技术解决方案。目前,线缆相关工作在三个不同的工作组中进行:电气工作组(EWG)、线缆工作组(CWG)和光学工作组(OWG)。其中,近期发布的CopprLink线缆内部和外部规范由EWG内的一个子工作组负责制定。

CopprLink线缆(内部和外部)专为PCIe 5.0和6.0技术设计,分别提供32.0 GT/s和64.0 GT/s的信号传输速度,采用SNIA维护的行业标准形式因子连接器,便于快速采纳、缩短上市时间并降低成本。CopprLink线缆将沿用同一形式因子面向未来带宽升级,推动PCIe线缆技术进入新纪元,尤其适用于数据中心服务器、存储、网络、加速器等领域中对延迟敏感的下一代应用。

CopprLink内部电缆规范特点:

-

支持PCIe 5.0和6.0技术,信号传输速率为32.0 GT/s和64.0 GT/s。

-

包含SNIA SFF-TA-1016连接器外形尺寸。

-

在单一系统内的最大可达距离为1米。

-

实现方案实例包括主板至扩展卡、主板至背板、芯片间以及在封闭式服务器平台节点中的扩展卡至背板连接。

-

目标应用集中在存储和数据中心计算节点上。

CopprLink外部电缆规范特点:

-

同样支持PCIe 5.0和6.0技术,信号传输速率为32.0 GT/s和64.0 GT/s。

-

包含SNIA SFF-TA-1032连接器外形尺寸。

-

在机架间连接的最大可达距离为2米。

-

实现方案实例包括CPU至存储、CPU至内存、CPU至加速器,以及在分散式服务器平台节点中的加速器网络。

-

目标应用特别关注存储和数据中心AI/ML应用场景。

CopprLink线缆设计之初就考虑了对未来PCIe技术的支持。随着PCIe线缆技术向CopprLink内部和外部线缆的演进,确保了PCIe技术紧跟市场需求前沿。电气工作组已着手为PCIe 7.0架构(128.0 GT/s)的CopprLink线缆进行路径探索,体现了PCI-SIG对CopprLink规范的承诺。

CopprLink内部和外部线缆与PCI-SIG光学工作组正在开发的光学PCIe互连不是直接相关。两者预计将是互补关系。光学PCIe尚处于探索阶段,旨在支持多种光学技术,且PCI-SIG也在考虑开发特定的光学形式因子,包括可插拔光收发器、板载光学、共封装光学和光学I/O。

扩展阅读:CXL与PCIe世界的尽头|你相信光吗?

除了CopprLink线缆,PCI-SIG的线缆工作组还在基于已广泛使用的SNIA SFF-8614连接器(通常用于存储应用,被称为“MiniSAS-HD”)开发新的外部线缆规范。这一努力独立于CopprLink线缆和光学工作组的倡议,旨在为存储应用提供替代Serial Attached SCSI (SAS)或Serial Advanced Technology Attachment (SATA)协议的解决方案。完成的5.0外部线缆规范将支持PCIe三个连续代的速度(8.0、16.0、32.0 GT/s),使PCIe技术成为企业市场中远程存储替代方案中的最快选择。

PCI-SIG的多项线缆计划相辅相成,针对不同应用场景提供特定优势。通过综合考虑各种PCIe线缆努力,可以看出PCI-SIG旨在通过多样化的技术方案满足广泛的行业需求,推动PCIe技术在不同领域的广泛应用和持续发展。

参考文献:https://pcisig.com/blog/

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

-

Backblaze发布2024 Q1硬盘故障质量报告

-

深度剖析:大容量QLC SSD为何遭疯抢?

-

SSD突然掉电,是谁保护了用户数据?

-

漫谈HAMR硬盘的可靠性

-

万物皆可计算|下一个风口:近内存计算

-

SSD数据错误如何修复?

-

CXL与PCIe世界的尽头|你相信光吗?

-

全景剖析SSD SLC Cache缓存设计原理

-

存储革新:下一代低功耗PCM相变存储器

-

3D DRAM虽困难重重,最快明年到来

-

字节跳动入局存储内存SCM

-

解读“CFMS中国闪存市场峰会”存储技术看点

-

首个业内DNA存储技术规范发布

-

如何突破SSD容量提升的瓶颈?

-

固态存储是未来|浅析SSD架构的演进与创新技术

-

论文解读:NAND闪存中读电压和LDPC纠错码的高效设计

-

华为新发布磁电存储“王炸”,到底是什么?

-

SSD LDPC软错误探测方案解读

-

关于SSD LDPC纠错能力的基础探究

-

存储系统如何规避数据静默错误?

-

PCIe P2P DMA全景解读

-

深度解读NVMe计算存储协议

-

对于超低延迟SSD,IO调度器已经过时了吗?

-

浅析CXL P2P DMA加速数据传输的原理

-

NVMe over CXL技术如何加速Host与SSD数据传输?

-

浅析LDPC软解码对SSD延迟的影响

-

为什么QLC NAND才是ZNS SSD最大的赢家?

-

SSD在AI发展中的关键作用:从高速缓存到数据湖

-

浅析不同NAND架构的差异与影响

-

SSD基础架构与NAND IO并发问题探讨

-

字节跳动ZNS SSD应用案例解析

-

CXL崛起:2024启航,2025年开启新时代

-

NVMe SSD:ZNS与FDP对决,你选谁?

-

浅析PCI配置空间

-

浅析PCIe系统性能

-

存储随笔《NVMe专题》大合集及PDF版正式发布!

如果您也想针对存储行业分享自己的想法和经验,诚挚欢迎您的大作。

投稿邮箱:Memory_logger@163.com (投稿就有惊喜哦~)

《存储随笔》自媒体矩阵

更多存储随笔科普视频讲解,请移步B站账号:

如您有任何的建议与指正,敬请在文章底部留言,感谢您不吝指教!如有相关合作意向,请后台私信,小编会尽快给您取得联系,谢谢!

![论文分享[cvpr2018]Non-local Neural Networks非局部神经网络](https://img-blog.csdnimg.cn/direct/690a833bf8324c1f943891fa2c0c00d4.png)