在本文中将展示描述了AXI从设备(slave)AXI BRAM Controller IP核与Xilinx AXI Interconnect之间的读时序关系。

1 Single Read

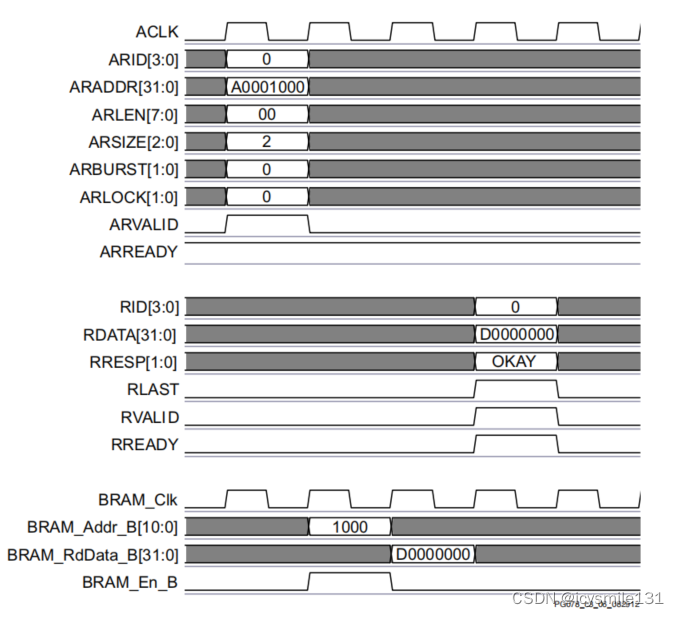

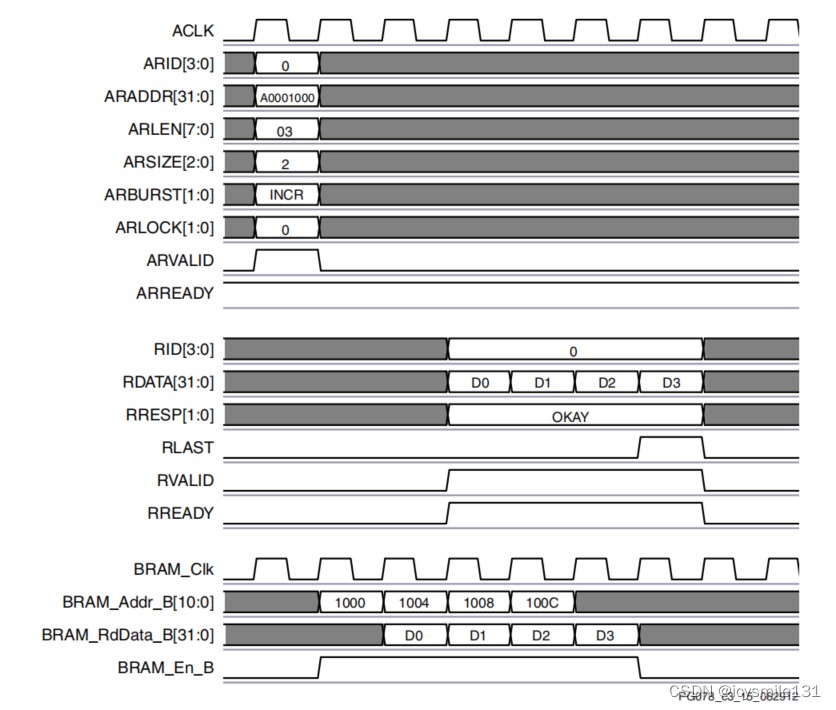

图1展示了一个从32位BRAM(Block RAM)进行AXI单次读取操作的时序示例。

图1 AXI 单次读时序图

在该时序中,需要注意的信号有:

(1)ARREADY信号

AXI读地址通道(AR Channel)上的ARREADY信号是一个注册输出信号,它默认是高电平断言(即置高)。AXI BRAM Controller可以在ARVALID信号首次有效的同一时钟周期内接受读取地址。当ARVALID和ARREADY信号都被断言时,AXI BRAM Controller将读取地址寄存器化(即存储)。

(2)读取地址流水线

AXI BRAM Controller内部有一个读取地址流水线(通常有两级深度)。当流水线满时(即已经有两个地址等待处理),AXI BRAM Controller会清除ARREADY信号,直到流水线中的地址数量减少,再次回到非满状态。

(3)RREADY信号

如果主设备可以立即接受数据,它可以在同一时钟周期内断言RREADY信号。当主设备在AXI总线上断言RREADY信号时,AXI BRAM Controller会否定(即置低)RVALID信号。这表示主设备已经准备好接收数据,并且BRAM Controller会在下一个时钟周期提供数据。

(4)RVALID和RLAST信号

对于单次读取事务,AXI BRAM Controller会在与RVALID信号相同的时钟周期内断言RLAST信号。RLAST信号表示这是单次读取操作中的最后一个数据项。在burst读取操作中,RLAST信号会在burst中的最后一个数据项时被断言。

在AXI读取事务中,读取数据总是在读取地址握手之后传输。AXI BRAM Controller不会断言RVALID信号,直到在同一时钟周期内ARVALID和ARREADY信号都被断言。换句话说,AXI BRAM Controller不支持提前访问,也没有内部缓存能力。

在AXI协议中,地址通道(AR通道)和数据通道(R通道)是分开的,这使得地址和数据可以独立地进行传输和处理。

2 Read Bursting

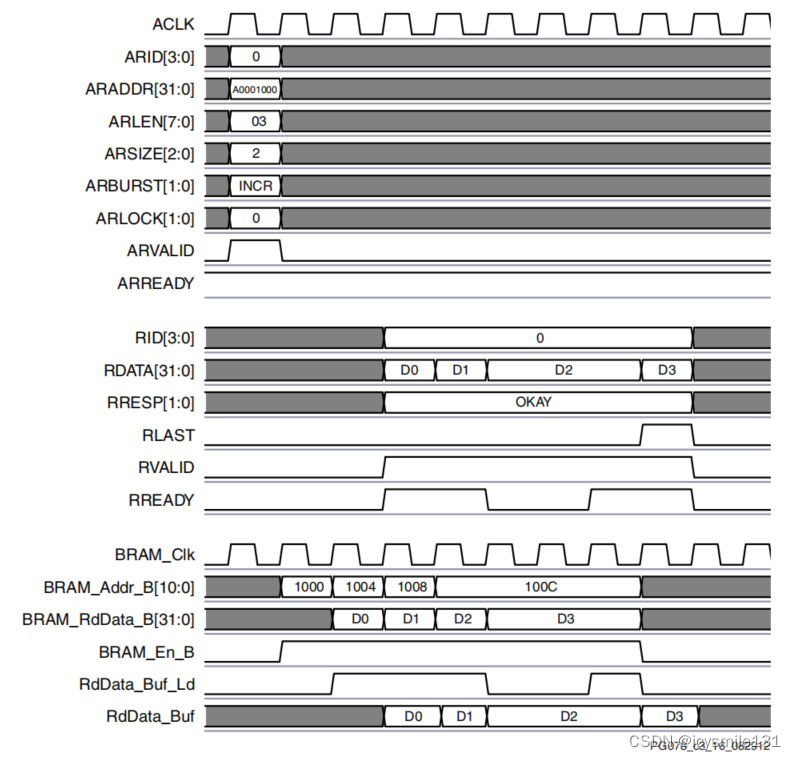

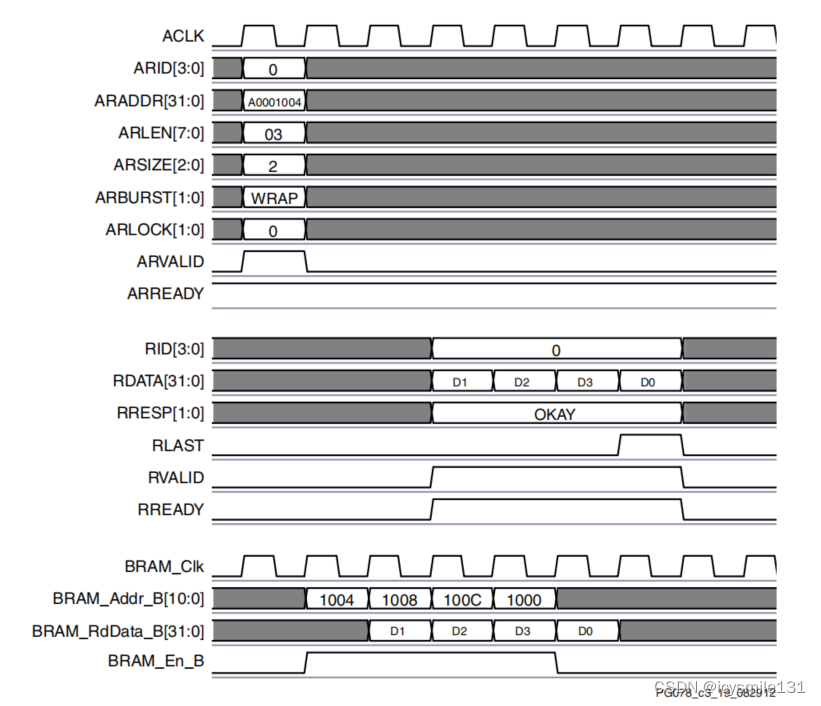

图2展示了一个AXI BRAM Controller进行的一个AXI读突发的时序图。

内存读突发开始于BRAM的0x1000h地址,并给定C_S_AXI_BASEADDR = 0xA000 0000以及C_S_AXI_HIGHADDR允许超过4k的可寻址内存。

AXI Read Address Channel 接口保持 ARREADY 信号断言,直到 AXI BRAM Controller 中的读地址流水线填满,这个过程是AXI协议中主从设备间数据传输的一个重要时序行为。

在AXI的读数据通道(R通道)上,AXI BRAM Controller支持AXI主设备/互联设备(Interconnect)在同一时钟周期内对RVALID信号的断言进行响应,即发出RREADY信号。

当AXI主设备或互联设备(Interconnect)在接受读突发数据时发生节流(即通过将RREADY信号置为低电平来减缓数据接收速率),AXI BRAM Controller能够处理这种情况,并暂停数据流水线,直到RREADY信号再次被断言(置为高电平)。

图2 AXI读突发时序

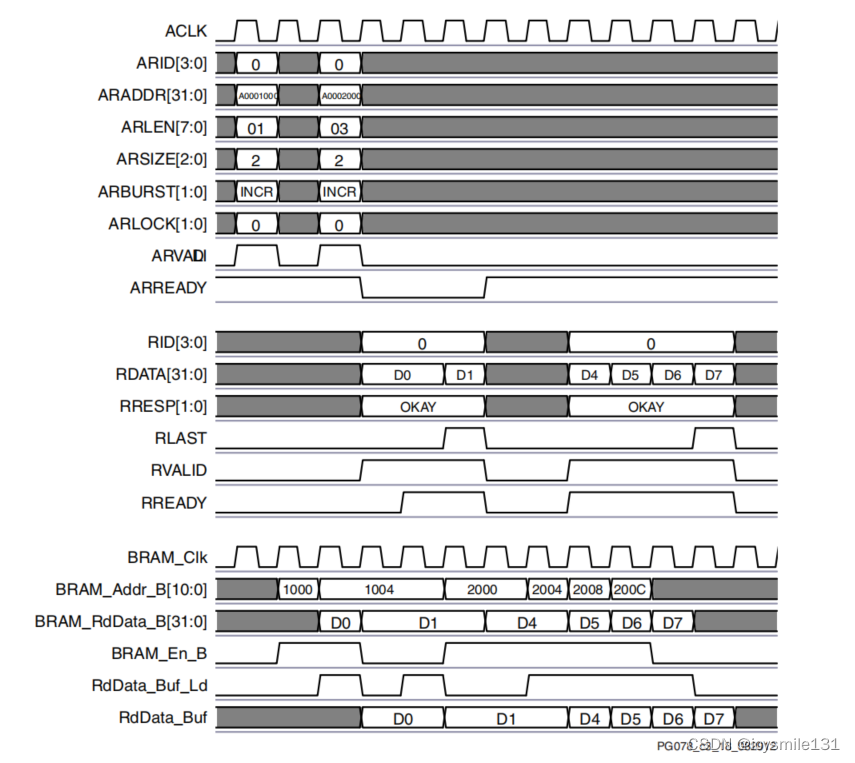

3 Read Throttling

AXI BRAM Controller必须支持读节流。在读操作过程中,AXI BRAM Controller向块RAM发出读命令,但只能在读数据缓存流水线中预读两个地址(这取决于AXI BRAM Controller支持的BRAM读数据节拍数)。请求AXI主设备无需立即捕获所有数据,而是可以在准备好接收数据时,通过断言RREADY信号来进行节流。当请求主设备否定RREADY时,AXI BRAM Controller必须暂停读操作并保持现有读数据。图3展示了这种行为以及相应的BRAM端口操作。

两级读数据流水线确保了所有到块RAM的输出和到AXI读数据通道的输出都被寄存。图3所展示的行为反映了主设备在RVALID被断言之前等待断言RREADY的情况。然而,AXI BRAM Controller可以在RVALID断言之前接受主设备对RREADY的断言。两个信号都必须被断言,以推进AXI BRAM Controller中的读数据缓存流水线。

图3 AXI读突发节流

4 Read Address Pipeline

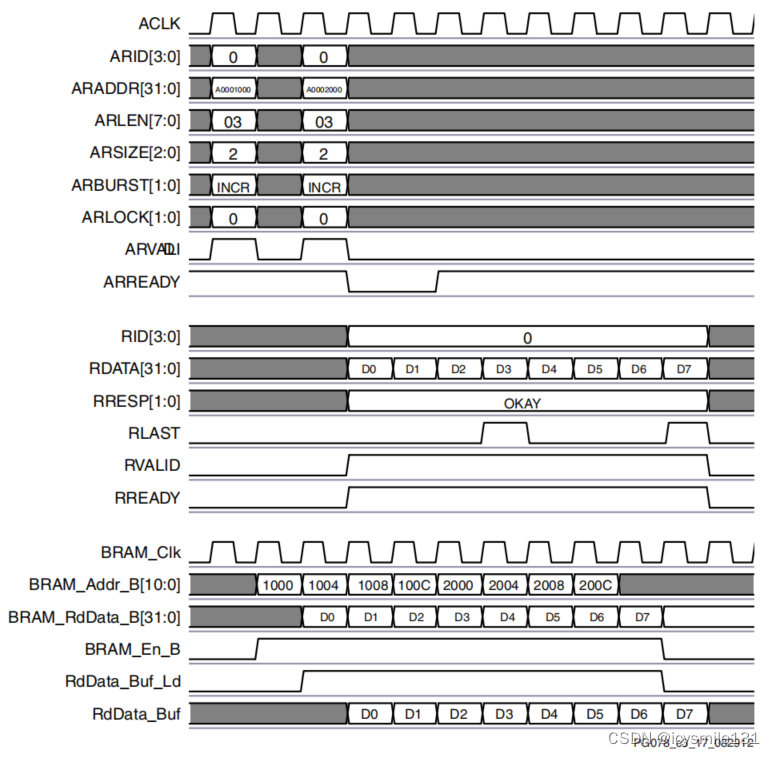

图4和图5展示了流水线读突发操作的时序示例。AXI BRAM Controller可以处理作为连续突发读操作到块RAM的流水线读地址。在这些条件下,流水线读操作的主设备可以在RLAST(来自先前的读操作)断言后的时钟周期内接收数据:

- 读操作不是单个数据节拍的传输

- 读突发大于两个数据节拍

- AXI突发操作大小等于AXI互联(Interconnect)的数据端口大小

- 请求的突发类型是INCR或WRAP

- 在倒数第二个BRAM地址被注册到内存之后,当前读突发在AXI读通道上没有检测到节流

无论是在双端口配置(使用第二个端口到块RAM)还是单端口BRAM配置(没有活动的待处理写传输)中,都支持到块RAM的连续读突发。如果流水线读操作中存在上述任何条件,主设备必须等待RVALID重新断言,才能开始读取后续突发的数据。预期延迟是在先前的RLAST之后两个AXI时钟周期,直到RVALID被断言(当上述任何条件存在时)。图5展示了这种场景的时序。

图4展示了AXI BRAM Controller接受流水线读请求地址的能力,并保持到块RAM的100%总线利用率。数据突发必须大于两个数据节拍,才能在AXI读数据通道上没有空闲时钟周期的情况下,从块RAM达到最大100%的数据吞吐量。请求的突发类型必须是INCR或WRAP,并且请求的读突发大小必须等于AXI互联(Interconnect)读数据端口的大小(没有“窄”突发类型事务),以实现流水线读突发的100%总线利用率。

读数据缓存缓冲区的利用说明了主设备在接受读数据时的节流能力。由此产生的BRAM事务时序如图5所示。

图4 在流水线读突发上实现AXI 100%总线利用率

图5 AXI 读流水线节流时序

5 Cacheline Reads

图6展示了AXI WRAP或缓存行突发事务的时序。当达到地址边界时,生成到块RAM的地址从目标字开始并循环(WRAP)回到起始点。

在WRAP突发模式下,地址在达到其定义的边界后,会“回绕”到突发开始的地址,并继续以递增的方式发送,直到达到突发长度的指定值。这种模式在访问连续内存区域时特别有用,尤其是当这些区域跨越了物理地址边界(如缓存行边界)时。

对于缓存行突发事务,地址通常按照缓存行的大小(如64字节)递增,并可能在达到缓存行边界时继续下一个缓存行的起始地址。这种突发模式有助于高效地与缓存一致的内存子系统交互,因为缓存行是缓存和主存储器之间数据传输的基本单位。

图6 AXI Cacheline Read