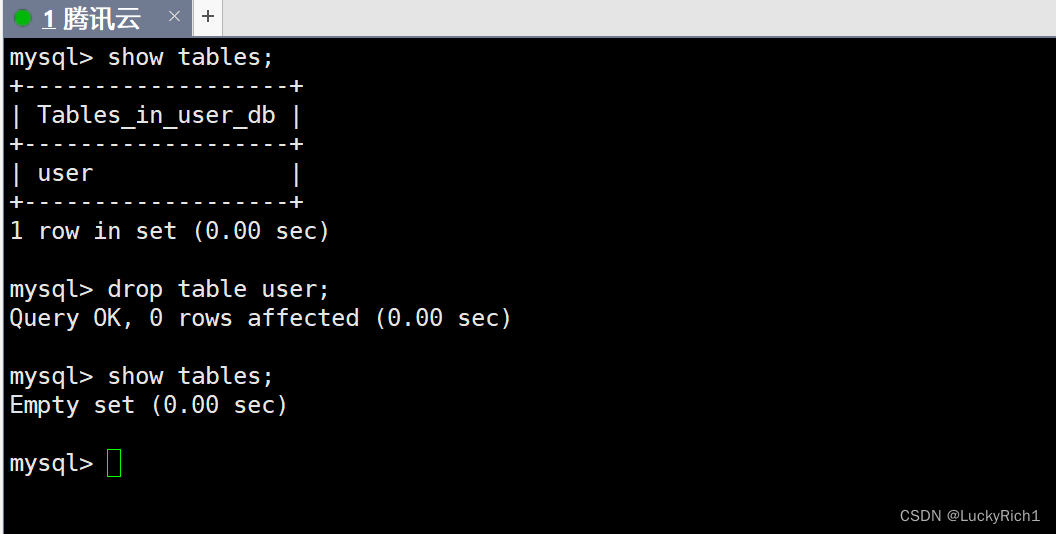

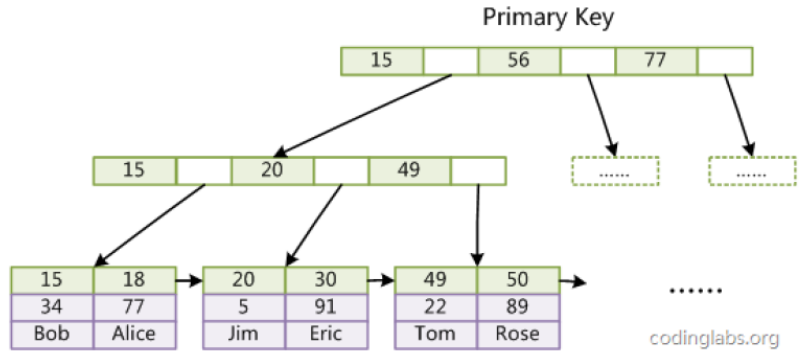

在最近的FPGA应用中,应用到了基于Zynq 7000的Uart串口设计,为了让串口的时钟更精确,采用了外部时钟模式,如下图所示。外部时钟连接到了Clocking Wizard IP核的输出端。

在串口通信时,发现串口有错码出现。例如,循环发送A1,接收到的大部分数据是正确的,但偶尔会出现42、76等不可预期的数。

出现这种情况,时钟是最大的怀疑因素。将Uart的时钟改为Zynq的输出时钟,再进行串口通信,则数据接收正常,不再有乱码出现。

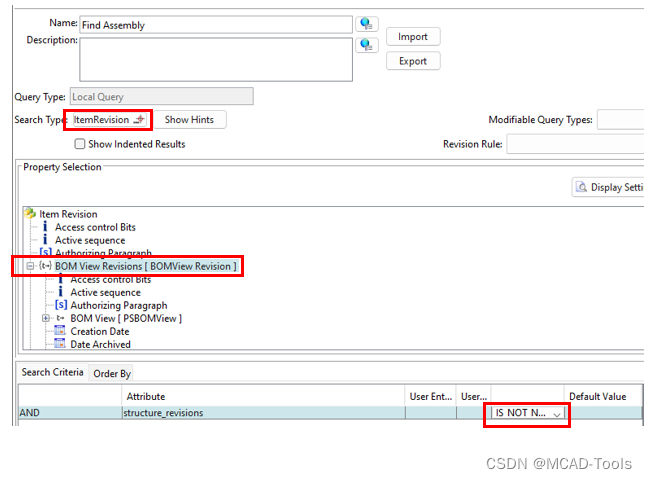

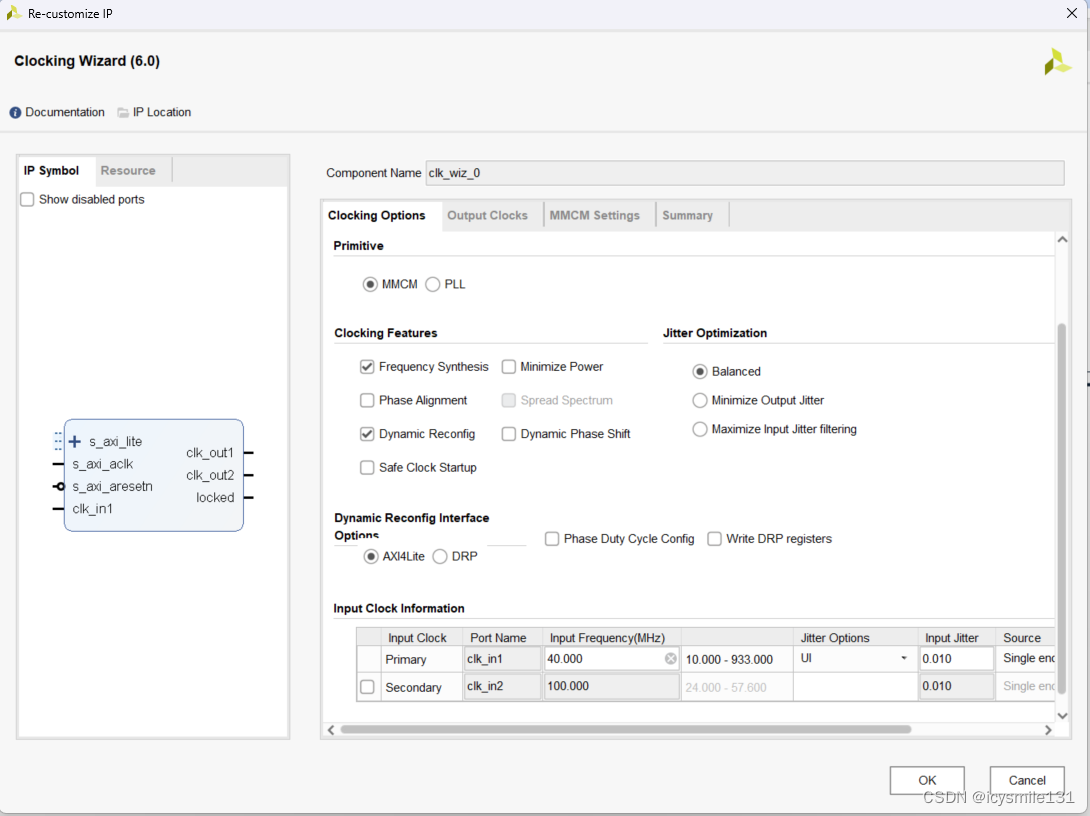

查看Clocking Wizard IP核的设置,如下图所示:

由上述情况可以推断,在Clocking Wizard IP核配置为动态可配置模式时,需要的配置参数比较复杂,如果配置不准确,输出时钟作为其他设备的稳定时钟输入可能会有误差。