基于Verilog表达的FSM状态机

- 1 FSM

- 1.1 Intro

- 1.2 Why FSM?

- 1.3 How to do

在这里聚焦基于Verilog的三段式状态机编程;

1 FSM

1.1 Intro

状态机是一种代码实现功能的范式;一切皆可状态机;

状态机编程四要素:–

1.状态State:

2.转态跳转Condition Jump:

3.行为Action:

4.次态–>现态Transform:

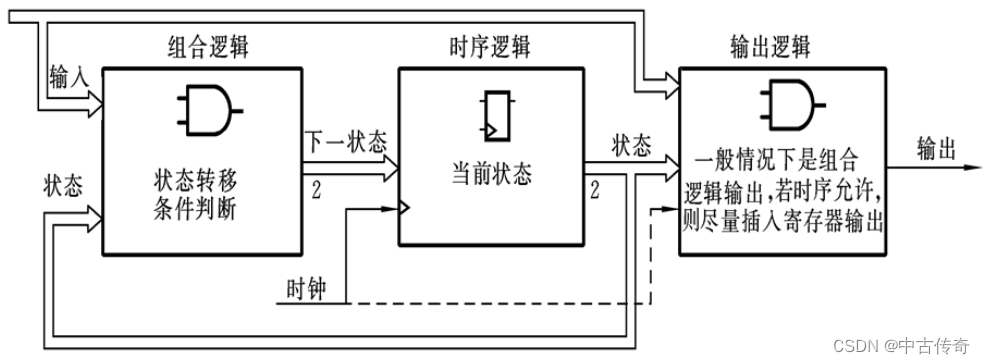

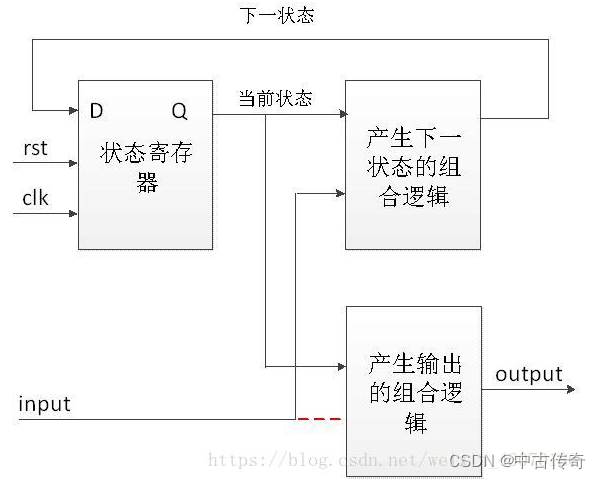

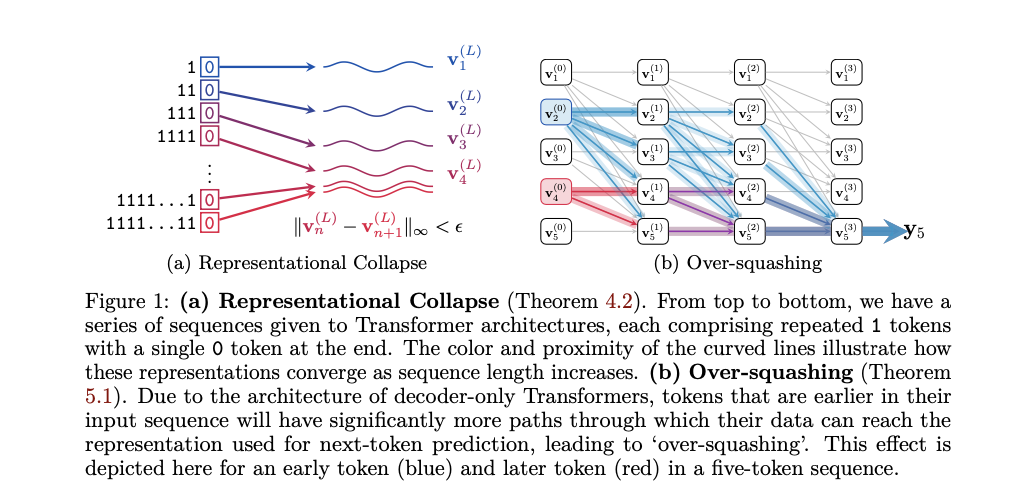

基本范式:systemverilog是Verilog的超集,使用可综合语句即可综合成电路;使用三段式转态机对应的综合电路:

这样看更直观:

module enum_fsm (input clk, reset, input int data[3:0], output int o);

enum int unsigned { S0 = 0, S1 = 2, S2 = 4, S3 = 8 } state, next_state;

always_comb begin : next_state_logicnext_state = S0;case(state)S0:if(xxx) next_state = S1;else if(xxx)next_state = S2;else next_state = S0; S1: next_state = S2;S2: next_state = S3;S3: next_state = S3;endcase

end

always_comb begincase(state)S0: o = data[3];S1: o = data[2];S2: o = data[1];S3: o = data[0];endcase

end

always_ff@(posedge clk or negedge reset) beginif(~reset)state <= S0;elsestate <= next_state;

end

endmodule

1.2 Why FSM?

无论是设计复杂的系统还是处理简单的逻辑流程,状态机都能提供清晰健壮、可维护且易于扩展的代码实现;

状态机思想提供了一种结构化、模块化和可扩展的思维方式进行功能逻辑实现;

- 逻辑清晰:状态机思想通过将系统行为划分为不同的状态和状态之间的切换,使得系统的逻辑更加清晰。可以帮助明确知道系统当前处于哪个状态,以及在不同状态下应该执行哪些动作;----有助于逻辑思考和代码可读性;

- 易于维护:状态机将系统的行为模块化,每个状态及转换都是相对独立的;这帮助解耦,使得修改和拓展该模块功能时,可以专注于特定的状态和转换,而不用再考虑整个系统的复杂性了;

- 可拓展性:状态机思想使得添加新的状态或转换变得相对简单。开发者只需要定义新的状态、转换条件和动作,然后将其集成到现有的状态机中即可。

- 错误处理:状态机通常包含对错误状态的处理机制。当系统遇到异常情况或无效输入时,状态机可以将其引导到错误处理状态,执行相应的错误恢复操作。

- 逻辑调试:状态机将系统的行为划分为有限数量的状态和转换,这使得在调试和测试阶段更容易追踪和定位问题。开发者可以通过模拟不同的状态转换和输入条件来测试系统的行为,从而确保系统的正确性和稳定性。

最后一句话:状态机思想为开发者提供了一种结构化、模块化和可扩展的方法来处理系统的复杂行为。通过采用状态机思想,开发者可以设计出更加清晰、健壮和易于维护的软件系统。

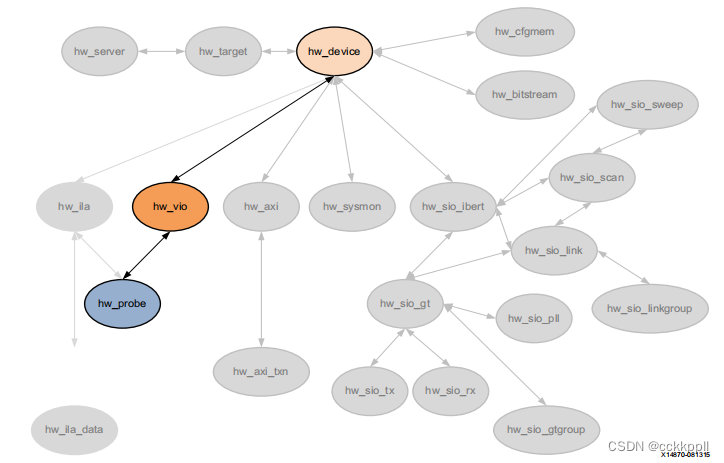

1.3 How to do

在状态机编程思想中:正确的顺序应该是先有状态转换图,而后才指导程序,程序应该是根据设计好的状态图写出来的。

即使是流水线也是状态机表达的一种特殊形式

- 状态描述图:首先需要描述确定下来,自己根据功能逻辑框图进行细化出来,先按照流水线的顺畅转态转移路线;

这个就是不要怕,自己先拍板定义状态及转态跳转关系;大胆的画出来;

根据review过的状态机,指导开始写代码,在写的过程中不断加深理解,再优化,不下手是永远不行的;

学会一种好的编程框架或者一种编程思想----会受用终生!比如模块化编程、框架式编程、状态机编程等,都是一种好的框架。

【Refer】

- https://blog.csdn.net/u012915636/article/details/136963178

- https://cloud.tencent.com/developer/article/2215987

- https://blog.51cto.com/oliverHuang/6503930

- https://blog.csdn.net/weixin_43070186/article/details/82085463

![[Shell编程学习路线]——深入理解Shell编程中的变量(理论与实例)](https://img-blog.csdnimg.cn/direct/f00a2c139497486590f28fef77767c10.png)