依公知及经验整理,原创保护,禁止转载。

专栏 《深入理解DDR4》

存和硬盘,这对电脑的左膀右臂,共同扛起了存储的重任。内存以其超凡的存取速度闻名,但一旦断电,内存中的数据也会消失。它就像我们的工作桌面,起着缓存的作用;而硬盘则像是一个庞大的仓库,各有各的优势与劣势。

随着科技的不断进步,内存技术也在日新月异地发展。从早期的SIMM(单边内存模块)到 DDR(双倍数据率)的诞生,再到 DDR 内存的不断迭代升级,我们不禁好奇地追溯 DDR 的发展历程。

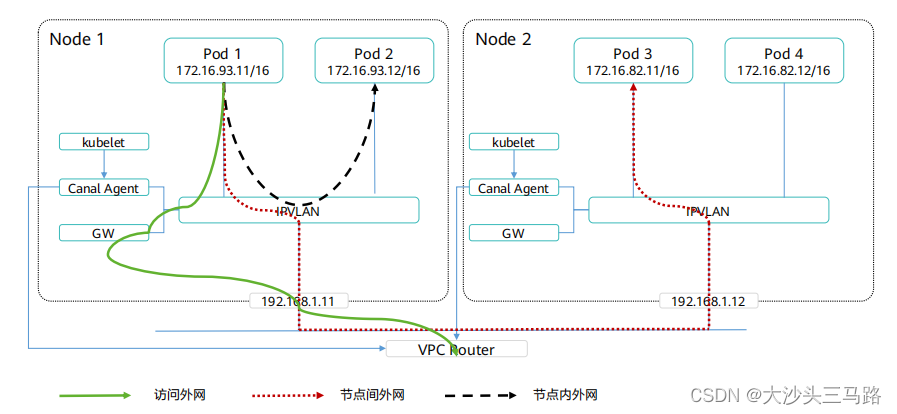

图来源: [今日头条]

发源

许多年前,计算机领域还没有独立的内存条存在,内存芯片直接以DIP(双列直插封装)的形式焊接在主板上。然而,当时的内存容量微乎其微,仅有 64KB 到 256KB [1]。更为糟糕的是,主板的内存容量是固定的,无法扩展。

SIPP

在 80286 处理器的崭新时代,主板上的内存已经无法满足日益增长的系统需求。为了解决这一问题,内存条应运而生,这也是计算机发展历程中的一个重要里程碑。初期的内存条被称为 SIPP(Single In-line Pin Package)

图: 30pin SIPP (Single In-line Pin Package), 来源:系统之家

SIMM

SIPP很快被SIMM取代,SIMM则成为了新一代的内存接口。SIMM拥有两侧十分耀眼的金手指,这与我们现代看到的金手指有点像。SIMM具有5V的工作电压,有30针SIMM、64针SIMM和72针SIMM等不同规格。

在386、486以及后来的奔腾、奔腾Pro、早期的奔腾II处理器中,大多数会使用72针内存。72针内存的位宽为32位,对于32位处理器而言,只需一根内存条即可满足需求。而对于64位处理器来说,需要两根内存条来进行数据读取与存储。这样的设计使得内存与处理器之间的数据传输更为顺畅,使得计算机系统的性能得到了提升。

图 30pin SIMM (Single In-line Pin Package)

SDR SDRAM内存

从 SIMM 到 DIMM,内存条经历了一次大的革新,这代表了内存技术的进步。SIMM 采用两边金手指传输相同的数据,而 DIMM 采用两边金手指传输不同的数据。这种变化使得内存条在进入 SDR SDRAM 时代取得了巨大的突破。

SDR 是指在时钟的单边沿发送数据,而 SDRAM 则是指同步动态随机存取存储器,它的内存频率与 CPU 外频同步,这大大提高了数据传输效率。SDR SDRAM 的数据位宽为 64 位,与当时 CPU 总线一致,因此只需要搭载一根内存条,受到了广大消费者的喜爱。

DDR内存

随后,DDR SDRAM 的问世彻底改变了内存技术的面貌。DDR SDRAM 在时钟的双边沿传输数据,与 SDR SDRAM 相比,在相同的频率下,传输速率提升了两倍。在使用上,DDR SDRAM 的地址方式和控制方式与 SDR SDRAM 几乎一致,使得从 SDR SDRAM 技术切换到 DDR SDRAM 成为了水到渠成的事情。这一时代的变革让人感到十分美好,也为 DDR 的时代开启了大门。至今,我们仍然身处在 DDR 的大家庭中,只是迭代不断,不断更新换代。

DDR2 以及后续的 DDR 系列作为 DDR 的迭代版本,延续了这个美妙的家族。让我们一起来看看这个大家庭的不断壮大吧。

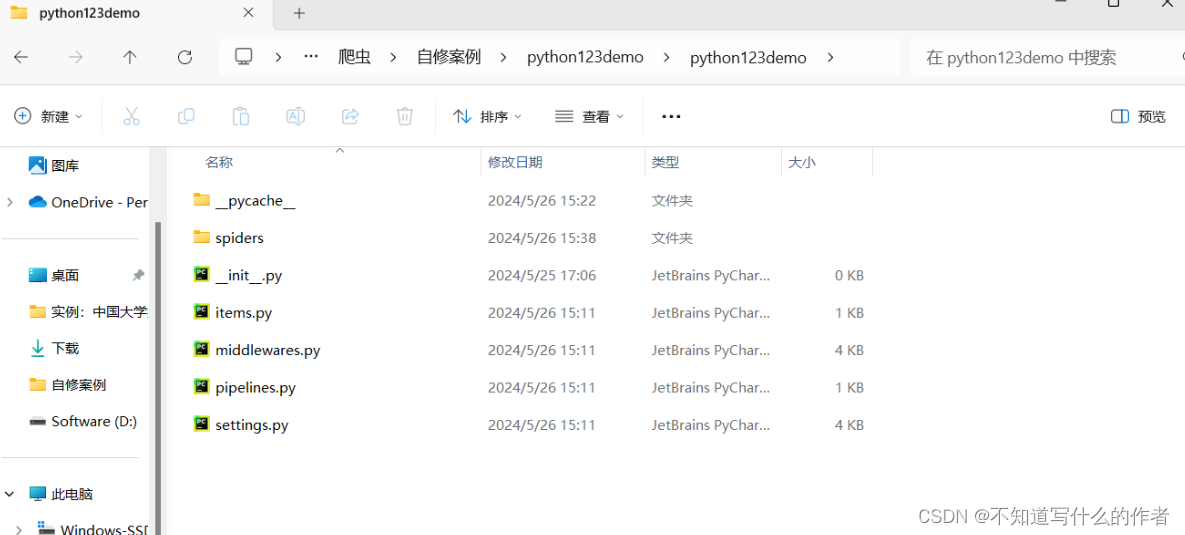

图 DDR 到 DDR4 改进量化指标

图来源: 系统之家-作者quers

DDR2 和前一代比,

电压降低了 28%

速度提升了 50.3%

容量增加了 100%

DDR3 和前一代比,

电压降低了 16.6%

速度提升了 166.5%

容量增加了 300%

DDR3 真是一个飞跃啊~

DDR4 和前一代比,

电压降低了 20%

速度提升了 100%

容量增加了 300%

DDR2

DDR2与DDR的区别

指标差异

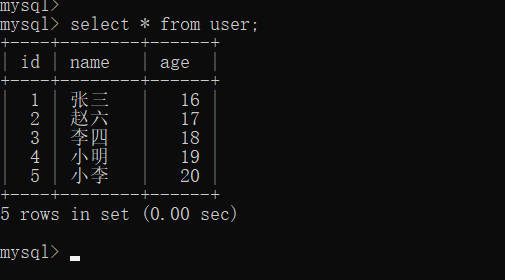

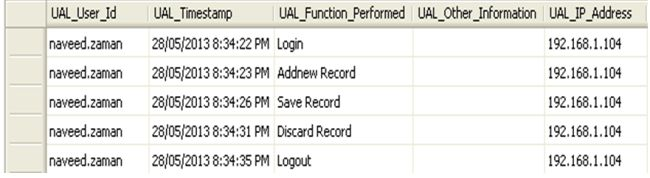

| DDR | DDR2 | |

|---|---|---|

| 电压 | 2.5V | 1.8V |

| 频率 | 100MHz~200MHz | 200MHz~400MHz |

| 速率 | 200Mps~400Mps | 400Mps~800Mps |

| 预取 | 2 bit | 4 bit |

| 封装 | TSOPII | FBGA |

百度百科:

DDR2的最大突破不在于普遍认为的传输能力翻倍,而在于更低发热和功耗的情况下,DDR2能够实现更高的频率,超越了标准DDR的400MHz限制。

而这得益于以下两点:

FBGA封装提供了更好的电气性能与散热性。- DDR2 采用

1.8V电压,相对于 DDR 的2.5V,降低了不少。

新功能

OCD、ODT 和 POST CAS

(1)ODT:ODT是让DQS、RDQS、DQ和DM信号在终端电阻处消耗完,防止这些信号在电路上形成反射。

(2)Post CAS:旨在提高DDR2内存的利用效率。 在没有使用Post CAS功能时,当前行的CAS命令占用了地址线,导致对其他L-Bank的寻址操作被延迟,并使数据I/O总线出现空闲。通过使用Post CAS,能够消除命令冲突,从而提高数据I/O总线的利用率。

来源: AET

(3)OCD(Off-Chip Driver):

OCD起到的作用是调整DQS与DQ之间的同步,以确保信号的完整性和可靠性。OCD主要用于调整I/O接口端的电压,以补偿上拉和下拉电阻的值,从而将DQS与DQ数据信号之间的偏差降到最低。在调校过程中,我们将分别测试DQS高电平和DQ高电平,以及DQS低电平和DQ高电平时的同步情况。如果测试结果不符合要求,将通过设置地址线的突发长度来传递上拉/下拉电阻等级。

来源: AET

DDR3

指标差异

| DDR2 | DDR3 | |

|---|---|---|

| 电压 | 1.8V | 1.5V |

| 频率 | 200MHz~400MHz | 400MHz~800MHz |

| 速率 | 400Mps~800Mps | 800Mps~1600Mps |

| 预取 | 4 bit | 8 bit |

| 封装 | FBGA | CSP和FBGA封装 |

| BANK 数 | 4 & 8 | 8 |

| 突发长度 4 | 4(兼容) & 8 |

新功能

ZQ: 接240欧姆的低公差参考电阻

SRT(Self-Reflash Temperature)可编程化温度控制存储器时钟频率

PASR(PartialArray Self-Refresh)局部Bank刷新

点对点连接(point-to-point,p2p)

RESET

Dynamic ODT

DDR4

| DDR3 | DDR4 | |

|---|---|---|

| 电压 | 1.5V | VDD1.2V, VDDQ 1.2V, VPP 2.5V |

| 频率 | 400MHz~800MHz | 800MHz~1600MHz |

| 速率 | 800Mps~1600Mps | 1600Mps~3200Mps |

| 预取 | 8 bit | 8 bit |

| 封装 | CSP和FBGA封装 | FBGA |

| BANK 数 | 8 | 16 |

| 突发长度 | 4(兼容) & 8 | 4 |

新功能

CRC

DBI

Multi preamble

参考

| 1 | DDR内存的前世今生 |

| 2 | DDR与DDR2、DDR3的区别 |

|

|

免责声明:

一. 本博客及动态出现的信息,均仅供参考。本人将尽力以求所提供信息的准确性及可靠性,但不保证有关资料的准确性及可靠性。本人对有关资料所引致的错误、不确或遗漏,概不负任何法律责任(包括侵权责任、合同责任和其它责任)。

二. 任何透过本博客及动态的网页或链接及得到的资讯、产品及服务,本人概不负责,亦不负任何法律责任。

三. 本博客及动态使用的信息,网页或链接(图片)可能由于本人疏忽未标明作者和出处,如有侵权,请立即与本人取得联系。

四. 本博客及动态支持保护知识产权,任何单位或个人认为本博客及动态中的网页或链接内容可能涉嫌侵犯其知识产权,应该及时向本人提出,并提供侵权情况证明。本人会依法尽快删除相关内容或断开相关链接。

五. 本博客内容仅供学习交流,禁止商用。

六. 阅读并使用本博客及动态包括其提供的网页链接及资源时,即代表您已阅读并同意本免责声明的全部内容。如有异议,请立刻关闭本网页并屏蔽本人动态并停止使用。