目录

1 系统级架构

1.1 DWC_otg PMU模块

1.2 DWC_otg层次结构框图

1.3 DWC_otg功能模块框图

1.4 USB Host体系结构

1.4.1 发送FIFO

1.4.2 接收FIFO

1.5 USB Device体系结构

1.5.1专用发送FIFO

1.5.2 单个接收FIFO

2 DWC_otg_core架构

2.1 AHB总线接口单元(BIU)

2.2 控制和状态寄存器(CSR)

2.3 应用接口单元 (AIU)

2.4 Packet FIFO Controller (PFC)

2.4.1 周期性发送数据FIFO

2.4.2 非周期性发送数据FIFO

2.4.3 PFC到SPRAM接口

2.4.4 端点信息控制器(EPINFO_CTL)

2.5 Media Access Controller (MAC)

2.5.1 MAC架构

2.5.2 USB事务处理

2.5.3 设备协议处理

2.5.4 主机协议处理

2.5.5 OTG协议处理

2.5.6 LPM功能

2.6 PHY 接口单元 (PIU)

2.7 唤醒和功耗控制 (WPC)

2.8 List Processor

3 电源管理单元(PMU)架构

3.1 PMU Slave模块

3.2 PMU Logic模块

3.3 PMU IfMux模块

3.4 PMU同步模块

3.5 ADP模块

4 系统时钟和复位

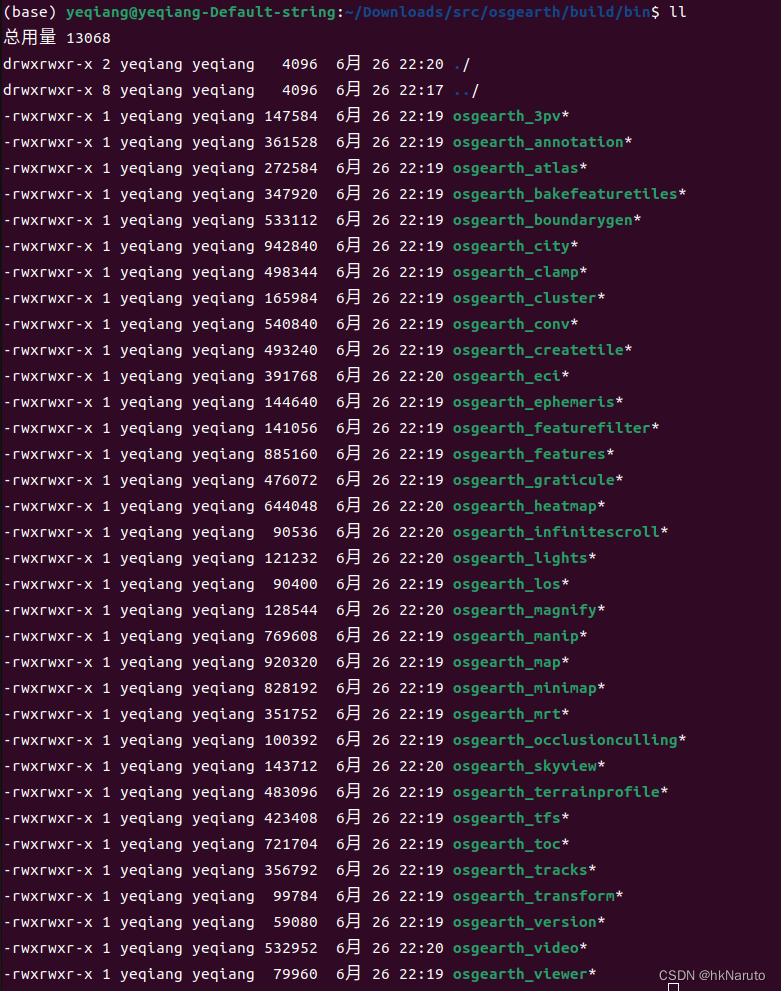

1 系统级架构

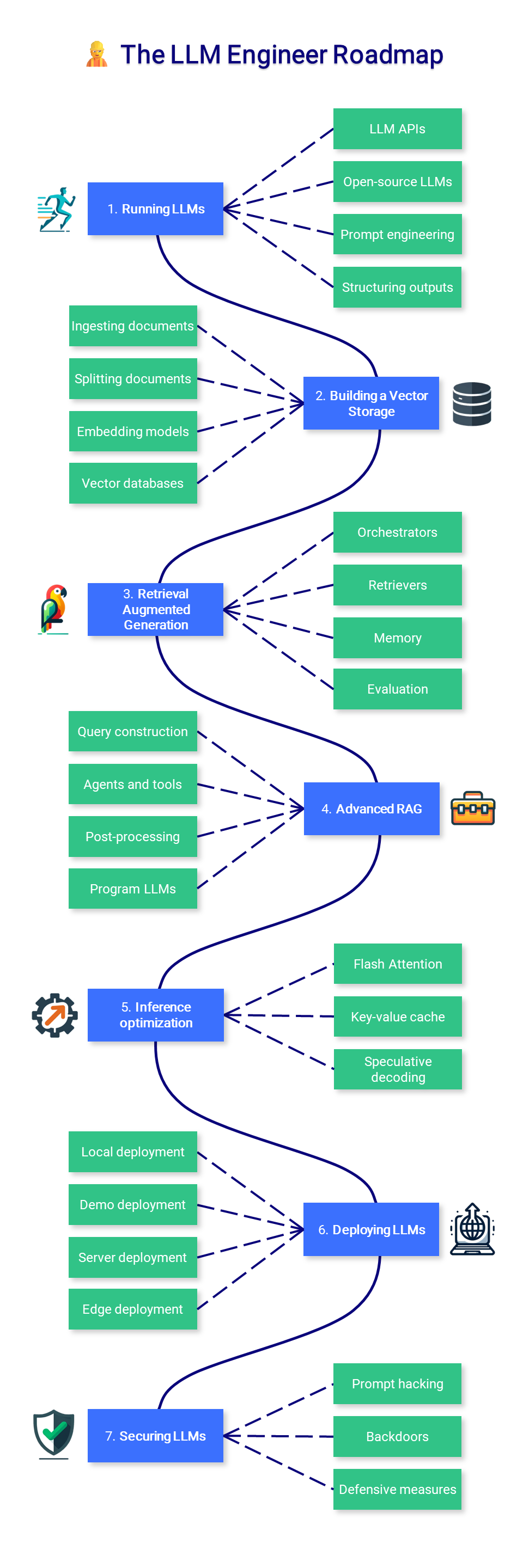

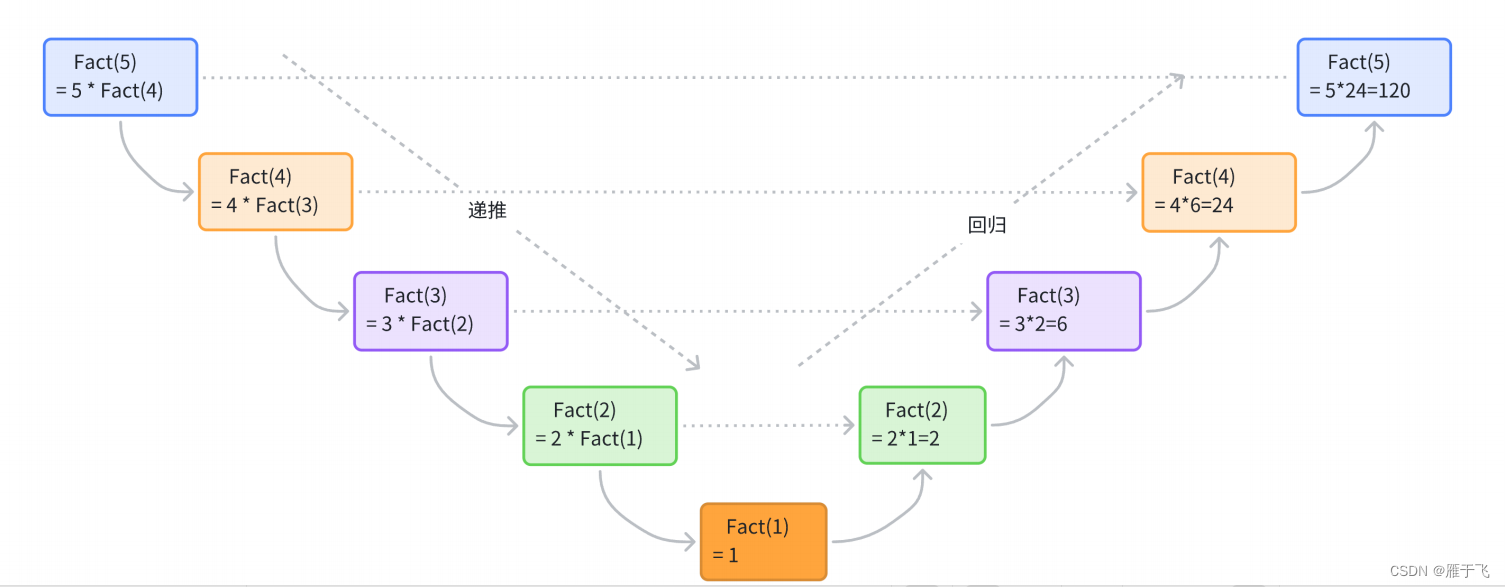

先对IP的系统级架构进行一些介绍。从操作层面看,DWC_otg提供以下三种操作模式,选择哪种模式由coreConsultant配置决定:

- Slave-Only模式

- Internal DMA模式

- External DMA模式(目前已经不支持该模式,后续不展开)

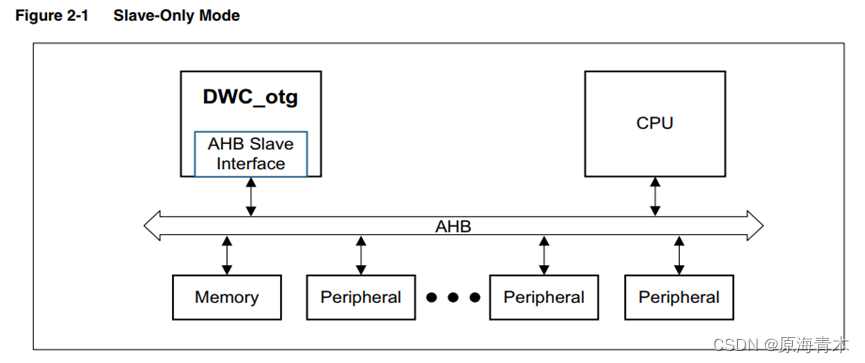

Slave-Only模式

其架构图如上图2-1所示,该模式可以减小IP的面积,此时需要CPU有足够的带宽去完成memory到DWC_otg之间的数据搬运。

这种模式下CPU是主设备,DWC_otg控制器是从设备,CPU通过AHB Slave接口对DWC_otg的寄存器、数据FIFO和队列进行读写访问。

个人理解这里的Slave-Only是针对AHB的总线操作角度来看的,在这种模式下只有AHB Slave接口,没有AHB Master接口,架构图中也没有体现AHB Master接口,至于DWC_otg控制器是作为USB Host还是USB Device,和Slave-Only模式没有关系。

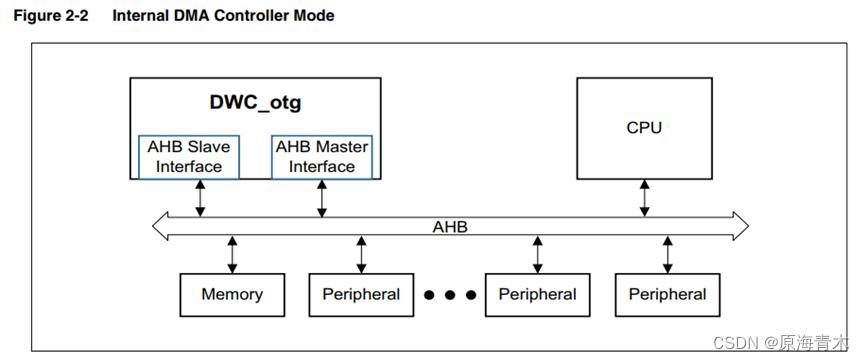

Internal DMA模式

其架构图如上图2-2所示,该模式使用DWC_otg内部的DMA,由DMA完成memory到DWC_otg之间的数据搬运,不占用CPU的带宽,CPU只需要负责完成中断和错误相关问题的处理。

这种模式下CPU是从设备,DWC_otg控制器是主设备,DWC_otg内部的DMA通过AHB Master接口完成memory到DWC_otg之间的数据搬运。

当IP配置Internal DMA模式时, CPU仍然通过AHB Slave接口对DWC_otg的寄存器进行读写访问,所以该模式下,既有AHB Slave接口,也有AHB Master接口。

总结来看,Slave-Only模式和Internal DMA模式主要差别就在于DMA。注意在Internal DMA模式下,软件可以禁用DMA从而变成Slave-Only模式。

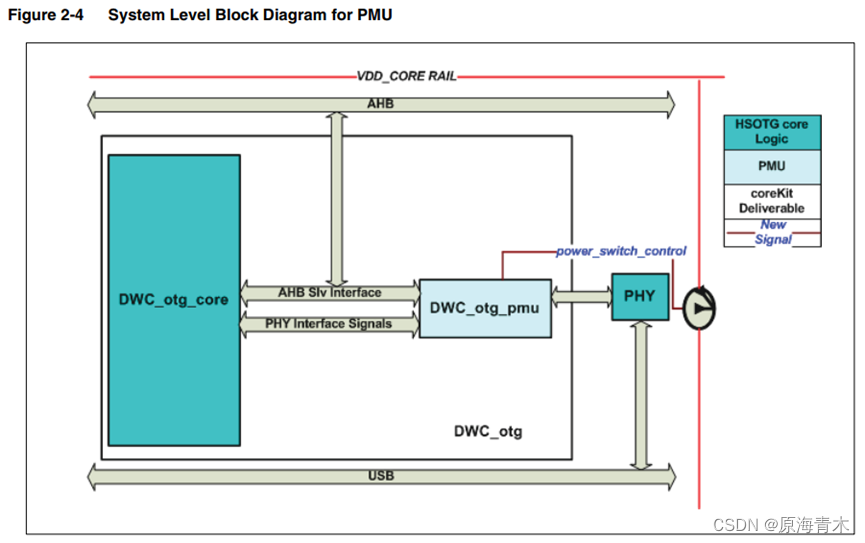

1.1 DWC_otg PMU模块

DWC_otg PMU模块提供如下功能:

(1)休眠(暂停期间在主机和设备模式下完全关闭DWC_OTG控制器)

(2)ADP探测和传感(可用于两种配置-当ADP控制器在控制器外部时以及当ADP控制器是控制器的一部分时)

主机和设备模式,休眠为DWC_otg控制器提供完整的电源门控。休眠可用于以下类型的配置:

■ OTG模式-适用于OTG和非OTG设备以及主机操作模式

■ 接口类型-UTMI+、ULPI、HSIC、IC_USB和FS专用

■ 以下体系结构类型:

❑ 基于内部缓冲区的DMA

❑ 基于内部描述符的DMA

❑ Slave-Only模式

图2-4提供了休眠工作架构。其中DWC_otg_pmu模块(电源管理单元或pmu)负责休眠过程。

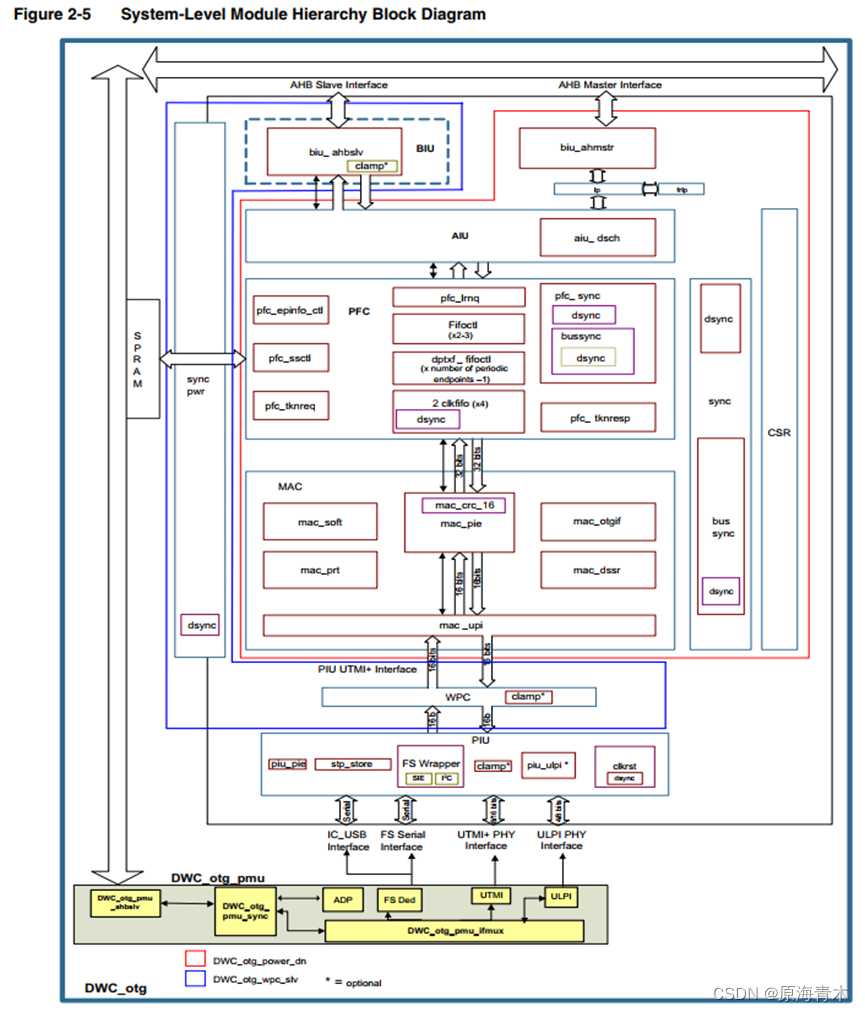

1.2 DWC_otg层次结构框图

图2-5显示了DWC_otg控制器中各个模块的层次结构。

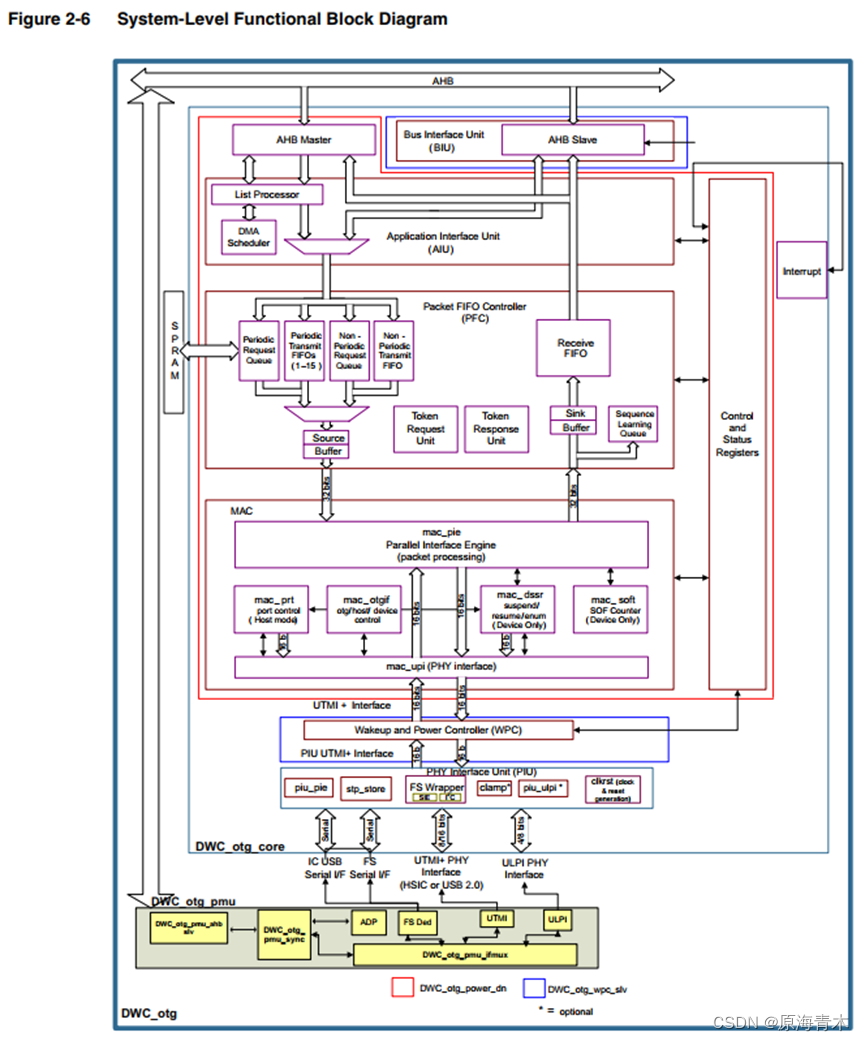

1.3 DWC_otg功能模块框图

图2-6显示了DWC_otg系统的主要模块和控制流程。

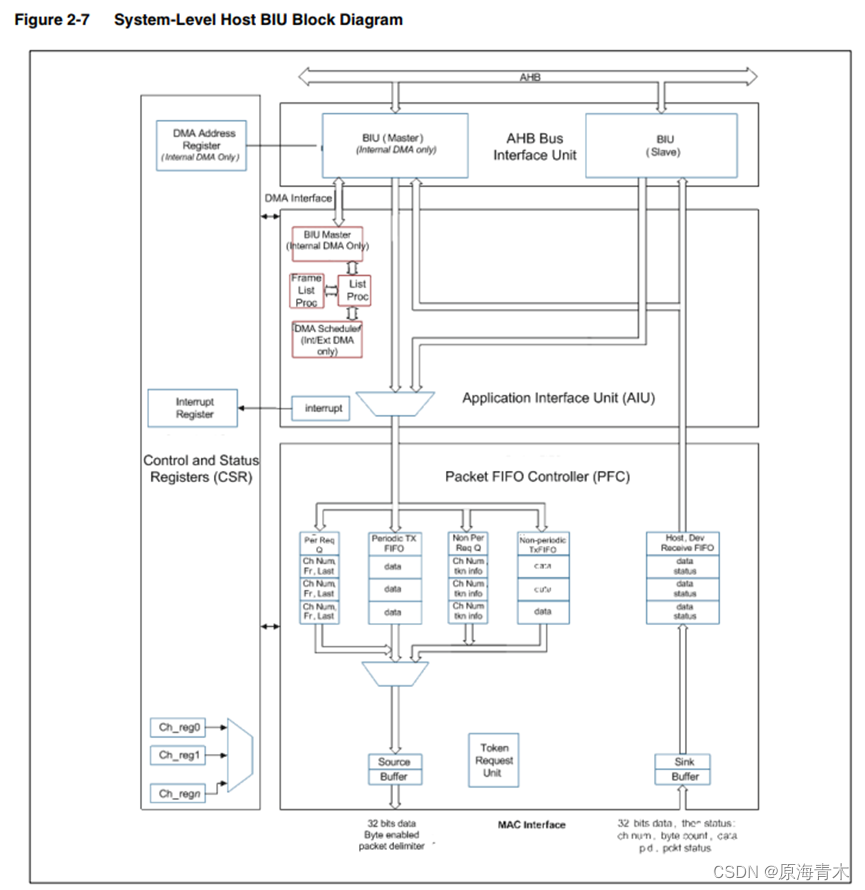

1.4 USB Host体系结构

1.4.1 发送FIFO

DWC_otg作为Host时,所有的非周期OUT传输使用一个发送FIFO,所有的周期OUT传输使用另一个发送FIFO,这些FIFO用于缓存USB传输的数据。

主机通过请求队列(一个用于周期性队列,一个用于非周期性队列)传输USB事务。请求队列中的每个元素都保存in或OUT通道的编号以及传输事务的其他信息。将请求写入队列的顺序决定了USB上的事务顺序。主机首先处理周期性请求队列,然后在每个(微)帧的开头处理非周期性请求排队。

1.4.2 接收FIFO

DWC_otg作为Host时,所有的周期和非周期接收到只使用同一个FIFO,该FIFO用于缓存接收的USB数据包,接收到的每个数据包的状态也保存在FIFO中,这里的状态是指保存IN通道的编号以及其他信息,例如接收的字节数量和有效性状态、在AHB上执行事务的请求等。

图2-7显示了USB Host模式下DWC_otg控制器的总线接口架构。

1.5 USB Device体系结构

1.5.1专用发送FIFO

DWC_otg作为Device时,当使用专用传输FIFO架构时(OTG_EN_DED_TX_FIFO=1),控制器为每个IN端点使用单独的传输FIFO。FIFO没有相关联的请求队列。应用程序无需预测USB主机访问非周期性端点的顺序。

1.5.2 单个接收FIFO

DWC_otg作为Device时,使用单个接收FIFO来接收所有OUT端点的数据,即接收FIFO只有一个,所有OUT端点都是使用一个FIFO。接收FIFO同时保存接收到的数据包的状态,如字节计数、数据PID和接收到的数据的有效性。DMA或MCU从接收FIFO中读取数据。

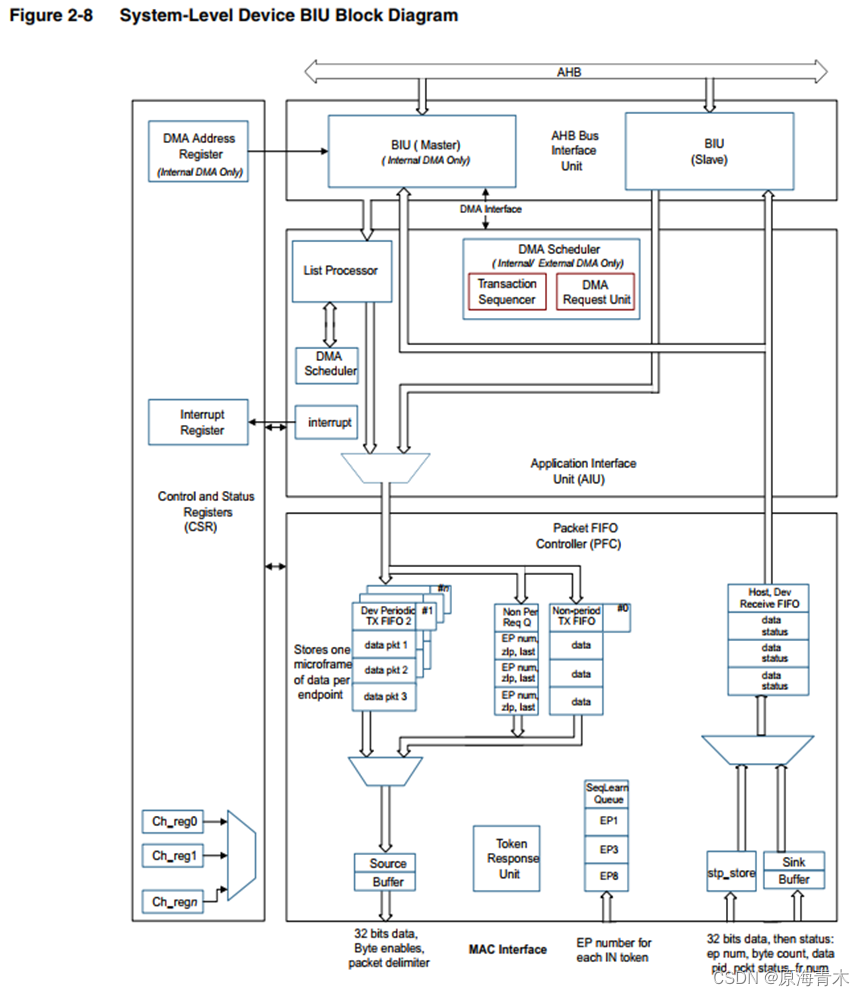

图2-8显示了USB Device模式下DWC_otg控制器的总线接口架构。

2 DWC_otg_core架构

本节介绍DWC_otg_core体系结构和主要模块。图2-9为DWC_otg_core架构框图。从上到下依次是BIU模块、AIU模块、PFC模块、MAC模块、WPC模块和PIU模块,右边还有个CSR模块。

2.1 AHB总线接口单元(BIU)

BIU分为2部分,分别是:AHB从总线接口单元 (BIUS)和AHB主总线接口单元 (BIUM)。

AHB从总线接口单元 (BIUS)

AHB从接口单元将AHB cycles转换为CSR写/读、数据FIFO读/写和DFIFO push/pop信号。BIUS具有下列特点:

- 完全兼容AMBA 2.0 AHB Slave协议。

- 支持INCR4,INCR8,INCR16,INCR和SINGLE。

- 支持忙和提前终止。

- CSR和DFIFO读取/写入必须始终为32位;8位和16位写访问将导致未知值写入DFIFO。

- 仅生成OK响应。

- 不生成SPLIT、RETRY或ERROR响应。

AHB主总线接口单元 (BIUM)

内部DMA控制器将内部DMA请求转换为AHB主请求。DMA地址、传输计数和数据包计数寄存器位于CSR块中。所选通道的地址作为内部DMA控制器的输入。简单说就是DWC_otg控制器的DMA作为AHB主机,负责控制器内部RAM和系统memory之间搬运数据。

BIUM有以下的特点:

- 完全兼容AMBA 2.0 AHB Master协议

- 支持burst类型:SINGLE,INCR,INC4,INC8和INC8

- 处理AHB拆分、RETRY、ERROR条件和提前终止

- 应用程序需要时可插入BUSY cycle

- 处理AHB 1KB边界

- AHB Master数据和地址总线都是32位,控制器可以传输hsize=2(DWORD)和0(BYTE)。

2.2 控制和状态寄存器(CSR)

CSR块位于AHB时钟域中,包含除电源和时钟门控控制寄存器(PCGCCTL)和控制器中断寄存器(GINTSTS)的位31:29之外的所有寄存器。这些寄存器位在断电模式下必须处于活动状态,因此在BIUS模块中实现。BIUS可以写入和读取寄存器,控制器可以设置或重置中断和状态位,中断的优先级高于BIUS。

2.3 应用接口单元 (AIU)

应用程序接口单元(AIU)由以下接口组成:

- AHB Master

- AHB Slave

- Packet FIFO Controller(PFC)

- Control and Status registers(CSR)

AIU主要功能:

- 在设备(in)和主机(OUT)模式中,给传输包生成定界符并将其写入传输FIFO(基于FIFO编号)。

- 在设备和主机模式下,将传输事务的令牌写入请求队列(周期性/非周期性)。

- 将令牌写入IN事务的请求队列(仅在主机模式下)

- 根据事务的类型选择周期性或非周期性请求队列。当通道或端点类型指明时将选择周期性队列。

- 在设备和主机模式下为发送和接收操作生成中断信号

- 给发送FIFO和队列的地址解码

- 为DMA控制器的数据传输生成DMA接口信号。

- 周期性和非周期性信道和端点之间的循环仲裁。周期性通道或端点具有更高的优先级。

- 当Tx阈值使能时,处理发送/接收阈值相关事务。

- 当阈值使能时,在欠载/溢出条件下,DMA地址和传输大小的卷绕逻辑处理。

2.4 Packet FIFO Controller (PFC)

在设备和主机模式下,PFC模块实现DWC_otg控制器内数据包的管理,以及数据包到SPRAM的传输等功能。

2.4.1 周期性发送数据FIFO

该FIFO存储周期性传输数据。在设备和主机模式下,存在不同的周期性FIFO结构。

Device模式

只包含专用发送FIFO。在这种状态下,不存在周期性或非周期性FIFO。FIFO是根据IN端点的数量(OTG_NUM_IN_EPS)来实现的,当启用使能时,应用程序为IN端点选择特定的FIFO。

Host模式

包含共享FIFO和非周期性的发送FIFO。

共享FIFO:在主机模式下,单个周期性FIFO存储所有周期性端点的数据。与该FIFO相关联的周期性请求队列用于存储周期性令牌请求。

2.4.2 非周期性发送数据FIFO

此FIFO存储设备模式下所有非周期性IN端点和主机模式下OUT信道上要传输的数据。与此FIFO相关的非周期性请求队列存储端点或通道相关信息。

专用发送FIFO

在主机模式下,FIFO体系结构与非专用传输FIFO操作中的体系结构相同。

在设备模式下,不存在周期性或非周期性FIFOs。FIFO是根据IN端点的数量(OTG_NUM_IN_EPS)来实现的,当启用使能时,应用程序为IN端点选择特定的FIFO。

接收数据FIFO

此FIFO存储设备模式下所有OUT端点和主机模式下的所有in端点上数据和状态。

2.4.3 PFC到SPRAM接口

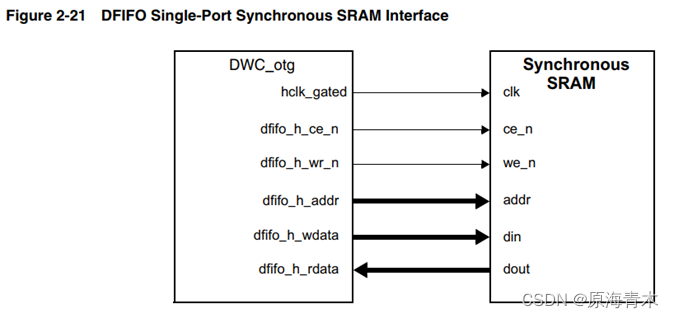

图2-21显示了如何将DWC_otg数据FIFO接口连接到行业标准的单端口同步SRAM。地址、写入数据和控制输出由DWC_otg延迟驱动,但时间上满足SRAM建立时序要求。输入读取数据预计会延迟从SSRAM中读取,并在使用之前在控制器内注册。

2.4.4 端点信息控制器(EPINFO_CTL)

SPRAM中的最后几个位置用于保存寄存器值。EPINFO_CTL用于管理这几个存储的值,如表2-1所列。

2.5 Media Access Controller (MAC)

媒体访问控制器(MAC)模块用于处理USB事务,以及实现USB设备、主机和OTG协议。

2.5.1 MAC架构

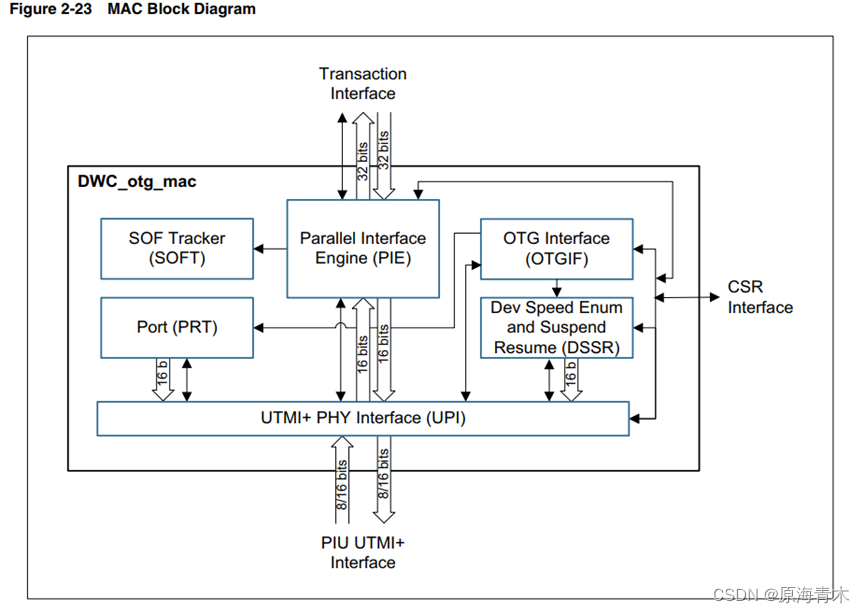

图2-23显示了MAC模块的结构。

DSSR

该模块仅在设备模式下处于活动状态。此块在设备模式下执行速度枚举、挂起、恢复和远程唤醒功能。

PIE

该模块负责令牌、数据和握手包的生成和接收,以及PID和CRC的检查和生成。它根据数据完整性、CSR控制和FIFO状态信息生成握手和数据包。PIE还处理FIFO之间的数据传输,以及PFC和AIU的状态更新。

SOFT

此模块跟踪SOF数据包,并在设备模式下生成SOF中断。它处理丢失的SOF和延迟的SOF,以保持主机和设备之间的帧数同步。

PRT

该模块仅在主机模式下处于活动状态。它负责连接和断开检测、USB重置和速度枚举、挂起和恢复生成、远程唤醒检测、SOF生成和高速测试模式处理。

OTGIF

OTG接口模块处理SRP和HNP。这些OTG协议通过常规UTMI+接口或I2C接口实现(仅适用于USB 1.1串行收发器)

UPI

该模块块转换8位PHY接口的数据宽度,并将来自多个块的输出信号多路复用到PHY。它还实现了由多个MAC块共享的一些逻辑。

MAC的设计使得在某些配置中可以移除未使用的组件,以减少门控数量。SOFT、DSSR和OTGIF可以在仅限主机的配置中删除;对于仅设备配置,可以删除PRT和OTGIF。

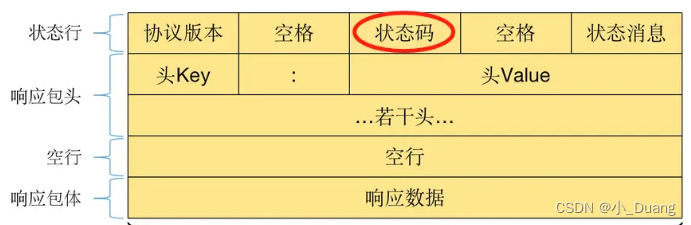

2.5.2 USB事务处理

设备模式

在设备模式下,当MAC接收到主机的令牌包时,对令牌包进行解码并检查其完整性。

如果接收到的令牌是有效的OUT或SETUP令牌,则MAC将等待并检查随后的数据包的PID,然后在RxFIFO可用时将数据写入RxFIFO。数据包完成后,MAC将检查数据的完整性,并在适当的时机向主机发送握手信号,将事务状态写入接收状态队列。如果接收到OUT令牌并且RxFIFO不可用,则MAC向主机发送NAK握手信号。

如果接收到的令牌是有效的PING令牌,则MAC基于FIFO状态和CSR状态发送适当的握手信号。

如果接收到IN令牌并且FIFO中的数据可用,则MAC将读取数据,构建数据包并向主机发送出去,随后等待来自主机的握手包(如果有的话),然后将事务状态更新到PFC。如果接收到IN令牌并且FIFO中的数据不可用,则MAC向主机发送NAK握手信号。

主机模式

在主机模式下,MAC接收来自AIU的令牌请求用于启动USB事务。在接收到令牌请求之后,MAC构建并发送所请求的令牌包。

对于OUT或SETUP事务,MAC从TxFIFO读取数据,构建并发送数据包,等待来自设备的握手包(如果有的话),然后将事务状态更新到AIU。

对于IN或PING事务,MAC等待来自设备的数据或握手包。如果MAC接收到握手包,则将状态更新到AIU。如果MAC接收到具有正确PID的数据包,则将数据写入RxFIFO并检查数据的完整性,再向设备发送握手包,然后将状态更新到AIU。

2.5.3 设备协议处理

在设备模式下,MAC处理USB的复位时序和枚举过程,以确定USB操作速度。MAC检测来自主机的USB挂起和恢复命令,启动远程唤醒,处理软连接和断开连接,解码和跟踪SOF数据包,并处理高速测试模式。

2.5.4 主机协议处理

在主机模式下,MAC检测设备的连接和断开,处理USB重置和速度枚举过程,启动USB挂起和恢复,检测远程唤醒,生成SOF数据包,并处理高速测试模式。

2.5.5 OTG协议处理

MAC处理用于主机和外围角色交换的主机协商协议(HNP),并处理会话请求协议(SRP),该协议允许A设备在使用USB总线时关闭VBUS以节省电力,并为B设备提供请求A设备激活VBUS的手段。

2.5.6 LPM功能

在设备和主机模式下,成功的LPM事务会导致控制器进入L1(睡眠)状态。睡眠状态功能由DSSR/PRT模块执行。

设备模式

作为一个设备,HS OTG控制器解析LPM事务,包括具有EXT PID的令牌和扩展的LPM令牌,并提供适当的响应。响应可以是ACK、NYET或STALL,也可以是无响应(ERROR响应)。

如果任何令牌出现错误,或者EXT PID令牌和LPM令牌之间发生超时,控制器将发送ERROR响应。

如果接收到的数据包的请求链路状态不是L1(睡眠),则控制器发送STALL响应。

如果满足以下任何条件,则控制器发送NYET响应:

■ NYET是编程的应用程序响应。

■ 任何传输FIFO都不是空的(默认值)。

■ 任何非ISOC传输FIFO都不是空的,并且设置了GLPMCFG[22]位。

■ 控制器的控制传输不完整,GLPMCFG[21]位已设置。

如果ACK是编程的应用程序响应并且发送队列全部为空,则控制器发送ACK响应。

通过中断向应用程序指示LPM令牌接收,并且在GLPMCFG CSR寄存器中更新LPM令牌响应以及令牌中接收的参数。

主机模式

当主机端口连接到(根)集线器时,应用程序发送SET和TEST端口控制传输类型。在这种模式(远程设备模式)下,集线器的响应到达应用程序的过程类似于控制传输。

当主机端口直接连接到设备(本地设备模式)时,应用程序必须对编程控制器中的GLPMCFG CSR寄存器用于发送LPM事务。控制器检查所有被禁用通道并发送LPM事务。如果来自本地设备的响应是错误的,主机将重试GLPMCFG.RetryCnt寄存器指定的LPM事务编程次数,或者直到从设备接收到有效响应。设备的响应通过中断指示给到应用程序,并且在CSR中更新LPM令牌响应。

2.6 PHY 接口单元 (PIU)

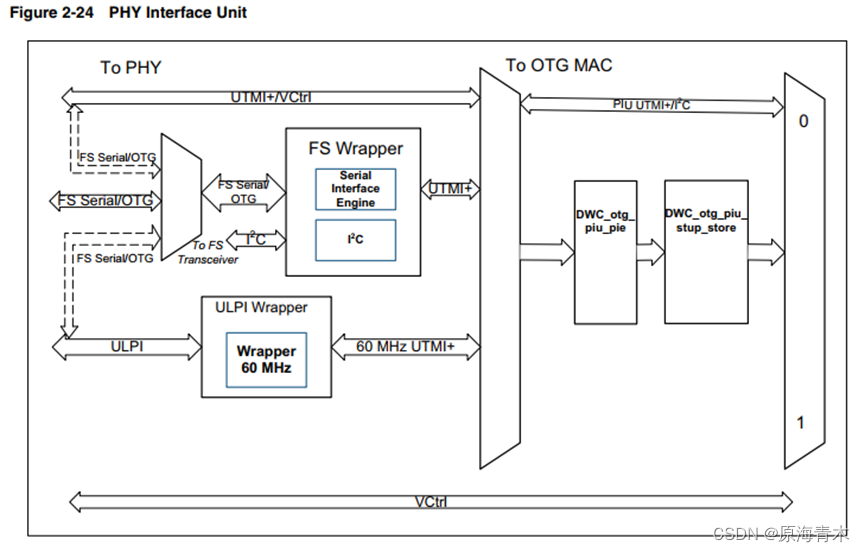

DWC_otg控制器支持的不同PHY接口。控制器上可用的PHY接口取决于在coreConsultant里面为高速PHY接口和USB 1.1全速串行收发器接口配置的值。通电后,可以使用软件选择UTMI+、ULPI或USB 1.1 FS串行收发器。

PHY和FS收发器可以在包含DWC_otg控制器的芯片的内部或外部。专用PHY/FS收发器接口支持在芯片的内部和外部实现。外部USB1.1 FS串行收发器可以共享外部UTMI+或ULPI接口端口,以减少芯片上的引脚数量

图2-24显示了PIU PHY和FS收发器接口。

2.7 唤醒和功耗控制 (WPC)

当USB被挂起或会话无效时,PHY被驱动到挂起模式,并且PHY时钟被停止,以减少PHY和DWC_otg控制器的功耗。

为了进一步降低功耗,DWC_otg控制器还支持AHB时钟门控和部分断电。当USB挂起或会话无效时,可以选择关闭某些DWC_otg模块的电源,或关闭某些选通至DWC_otg模块的AHB时钟。

关于如何使用这些低功耗功能的详细操作信息,请参阅《编程指南》中的“FIFO RAM分配”章节。要使用这些功能,必须在coreConsultant配置期间使能“启用电源优化”。

当USB挂起或会话无效时,给DWC_otg模块供电的大多数的电源可以关闭。某些逻辑必须保持通电状态,以检测恢复、远程唤醒、SRP或新会话启动事件,用于唤醒控制器。要实现部分断电,需要两个电源。在部分掉电模式下可以关闭的逻辑在一个电源VDD_DN上,而在部分掉电源模式下必须激活的逻辑在另一个电源VDD_WAKEUP上。

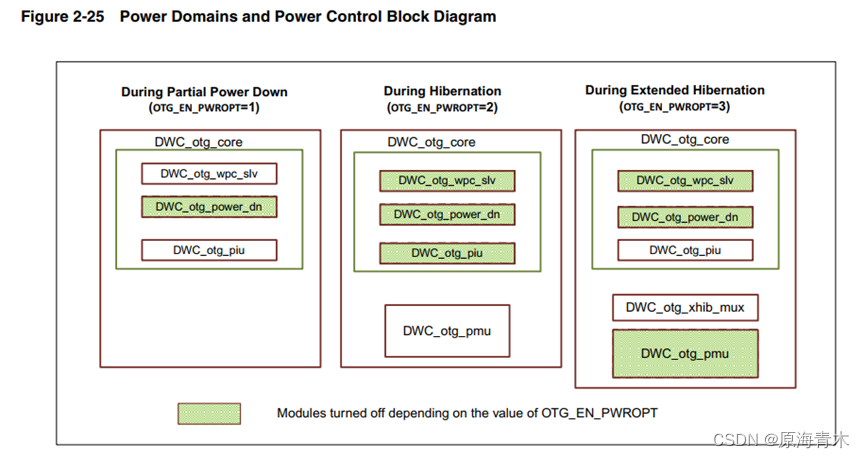

唤醒和功率控制所涉及的组件如图2-25所示。

BIU、PIU、WPC、CLKRST和SYNC_PWR块必须连接到VDD_WAKEUP域。CSR、AIU、PFC、MAC和SYNC模块必须连接到VDD_DN域。在掉电模式下,为了避免掉电模块的产生功耗,由上电模块生成并由掉电模块使用的所有信号都被钳位为低电平。为了避免断电模块的信号状态破坏,由断电模块生成并由通电模块使用的所有信号都是高电平的,并且在断电时被钳位为低电平。

WPC模块将控制器从部分断电模式唤醒,有以下主要功能:

在主机模式下:

■ 当USB挂起时,检测来自设备的远程唤醒信号,驱动恢复并解除挂起的引脚。

■ 当会话关闭时,检测来自设备的会话请求,并解除挂起的引脚。

■ 当USB挂起且控制器处于部分断电模式时,检测高电平恢复信号以生成PHY时钟。

■ 当会话无效且控制器处于部分断电模式时,检测高电平恢复信号以生成PHY时钟。

在设备模式下:

■ 当USB挂起时,检测主机的恢复信号,并解除挂起的引脚。

■ 当USB挂起时,检测设备的SRP信号,并解除挂起的引脚。

■ 当USB挂起且控制器处于部分断电模式时,检测高电平恢复信号以生成PHY时钟

■ 当会话无效且控制器处于部分断电模式时,检测高电平恢复信号以生成PHY时钟

2.8 List Processor

列表处理器(LP)为设备和主机模式实现基于描述符的Scatter/Gather DMA功能。

3 电源管理单元(PMU)架构

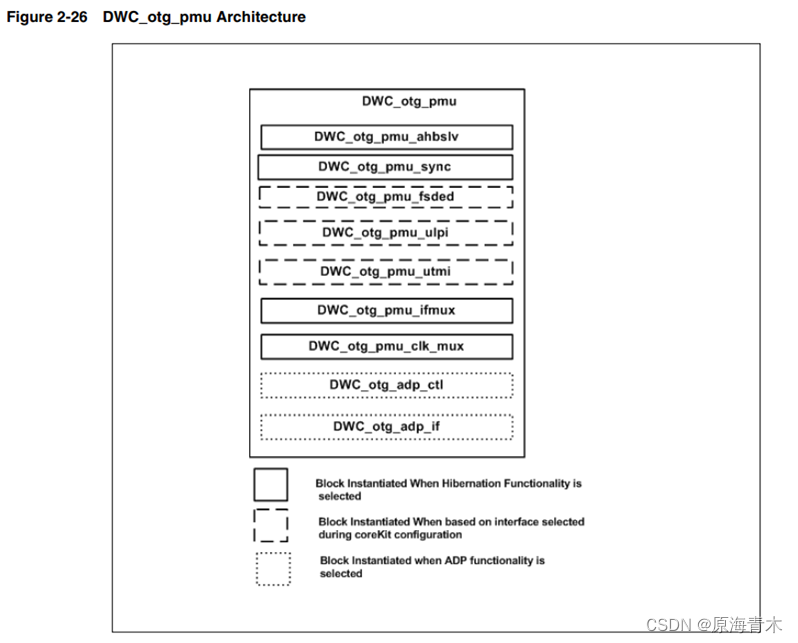

电源管理单元(PMU)是一个支持休眠功能的模块。图2-26展示了DWC_otg_pmu模块的架构。

3.1 PMU Slave模块

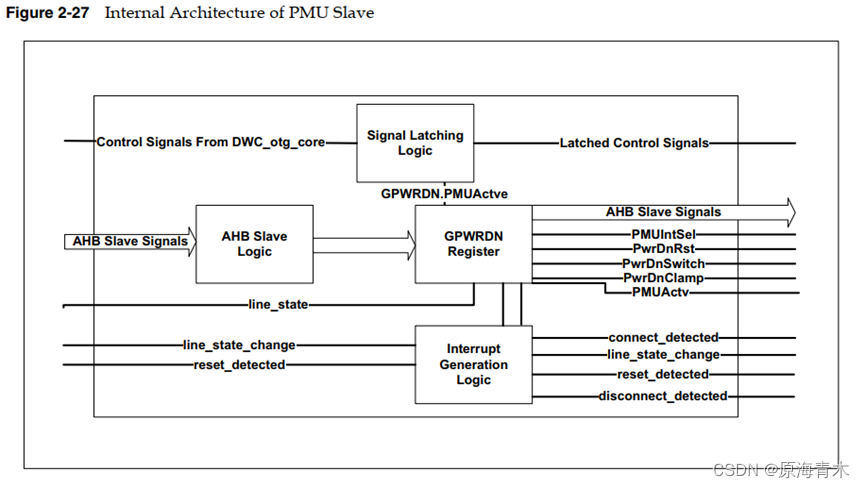

PMU Slave通过AHB总线提供应用程序接口控制PMU逻辑。图2-27说明了PMU Slave的体系结构。

AHB Slave Logic:用于读写 GPWRDN寄存器。

Signal Latching Logic:此逻辑在控制器进入休眠状态之前用于锁存来自DWC_otg_core的控制信号,控制信号提供给PMU逻辑,用于指示控制器的操作模式。

GPWRDN register:GPWRDN寄存器实现。

Interrupt Generation Logic:控制中断信号的产生。

3.2 PMU Logic模块

根据所使用的PHY类型,PMU使用以下类型的唤醒逻辑之一:

■ DWC_otg_pmu_utmi-用于utmi+和HSIC接口

■ DWC_otg_pmu_fs_ded-用于IC_USB和fs专用接口

■ DWC_otg_pmu_ulpi-用于ulpi接口

不管使用哪种唤醒逻辑,PMU逻辑均会执行以下功能:

■ 当控制器处于休眠状态时,驱动PHY接口信号

■ 解码DWC_otg_pmu_ifmux模块的信号状态

除了PMU逻辑之外,还使用以下逻辑:

■ 信号锁存逻辑-当唤醒逻辑被激活时,该逻辑用于将控制器输出信号锁存到PHY。

■ 逻辑驱动PHY信号-基于正常操作、主机或设备操作模式下的远程唤醒操作,此逻辑驱动接口信号到PHY。

3.3 PMU IfMux模块

DWC_otg_pmu_ifmux模块执行以下功能:

■ 复用来自不同接口的line_state

■ 检测line_state中的更改

■ 复用来自不同接口的状态

■ 检测状态的更改

■ OTG 2.0版和OTG 1.3版SRP检测

3.4 PMU同步模块

该模块同步DWC_otg_pmu_ahb_slv和pmu接口逻辑之间的时钟域信号。

3.5 ADP模块

PMU模块内的ADP模块支持ADP探测和ADP传感活动,符合中USB 2.0中On The Go 补充规范。ADP块由以下部分组成:

■ DWC_otg_pmu_adp_ctl.v-这是PHY的adp控制逻辑。

■ DWC_otg_pmu_adp_ctl_if.v-这是AHB和PHY之间的adp控制接口逻辑。

■ DWC_otg_pmu_sync.v-这是AHB时钟和PHY时钟之间的同步器。

4 系统时钟和复位

DWC_otg控制器具有以下输入时钟:

■ hclk:AHB时钟。hclk是控制器的AHB域的扫描时钟。选择它作为测试时钟。

■ pmu_hclk:休眠、ADP启用时,向PMU模块提供时钟。

■ utmi_clk:UTMI+时钟。仅在选择UTMI PHY时才在功能上使用,但在DFT扫描模式期间始终用作PHY域时钟。即使在控制器配置为非utmi PHY时,也选择utmi_clk作为测试时钟。

■ ulpi_clk:ULPI PHY时钟。仅当选择了ULPI PHY时才出现;negedge也用于DDR模式。为ulpi配置控制器时,选择ulpi_clk作为测试时钟。

■ utmifs_clk48:仅当OTG_FSPHY_INTERFACE!=0存在。当控制器配置为USB 1.1全速串行收发器接口时,控制器选择utmi_clk引脚作为测试时钟。

■ ref_clk:仅在使能OTG_SERV_INT_ENH时出现。控制器选择utmi_clk时钟作为逻辑的测试时钟,该逻辑采用ref_clk采样。

此外,控制器在DWC_otg_clkrst模块中生成以下时钟:

■ phy_clk:门控PHY时钟输出(多路复用ULPI、UTMI+、USB 1.1 FS时钟或USB 1.1 FS除以8的时钟之一)。当选择USB 1.1 FS收发器时,在LS中,48 MHz输入时钟除以8以生成6 MHz内部时钟。该时钟必须与生成的时钟同相,并具有与生成的钟相同的插入延迟。如果启用了功率优化,phy_clk必须与生成的时钟和wpc_clk同相操作,并且具有与生成的钟和wpc_clk相同的插入延迟。

■ wpc_clk:非门控PHY时钟输出(MUXed ULPI、UTMI+、USB 1.1 FS时钟之一),仅当OTG_EN_PWROPT不等于零时才出现。该时钟必须与phy_clk、utmi_clk,ulpi_clk和utmifs_clk48同相,并具有相同的插入延迟。

■ hclk_gated:hclk门控用于功率优化。仅当OTG_EN_PWROPT不等于零时出现。

■ utmifs_clk6:ULPI、UTMI+或USB 1.1 FS时钟除以8。仅当选择USB 1.1 FS串行收发器接口时才显示。