3.数字音频处理

芯片支持高级数字音频处理能力,包括:

-

高通滤波器/直流阻断

-

数字音量控制

-

PVDD的Foldback/AGL

-

热Foldback

-

双象限增益补偿

-

混合调制

-

实时负载诊断

-

低延迟路径

-

喇叭功率限制

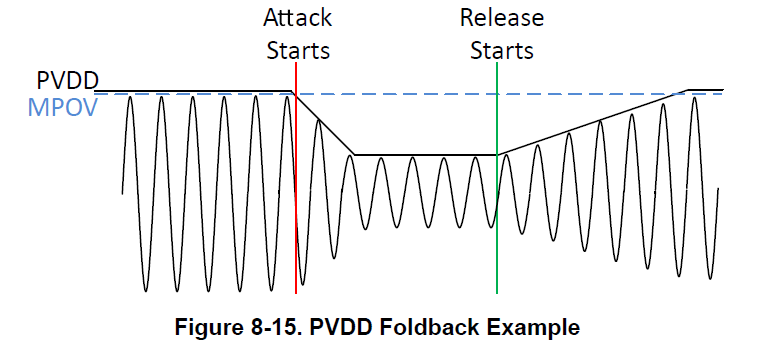

1)PVDD Foldback

本功能主要为了防止音频信号失真,也称为自动增益限制(AGL:Automatic Gain Limiter)。PVDD Foldback依据PVDD的电压值有两个功能模式:

-

模式1:如果PVDD超过最大输出峰值电压(MPOV),则无需动作;

-

模式2:如果PVDD低于MPOV,则将降低信号增益,同时触发PVDD Foldback警告事件。

本功能通过设置DSP_CTRL2 Register (Address = 0x3A)的bit4为1进行使能。

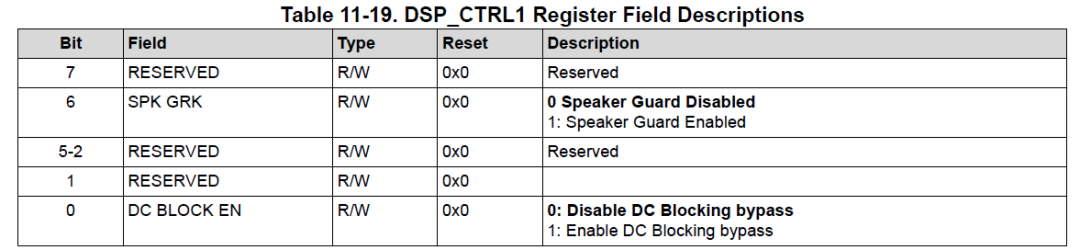

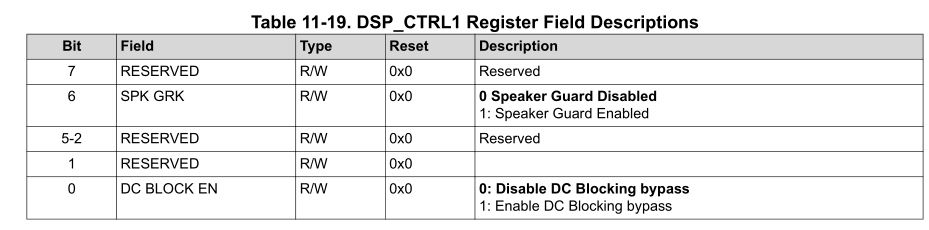

2)高通滤波器

为了保护连接到TAS6511-Q1的扬声器,在音频处理路径中内置了一个直流阻断高通滤波器。该滤波器默认打开,当然也可以通过设置DSP_CTRL1 Register (Address =0x39)的bit0为1关闭。

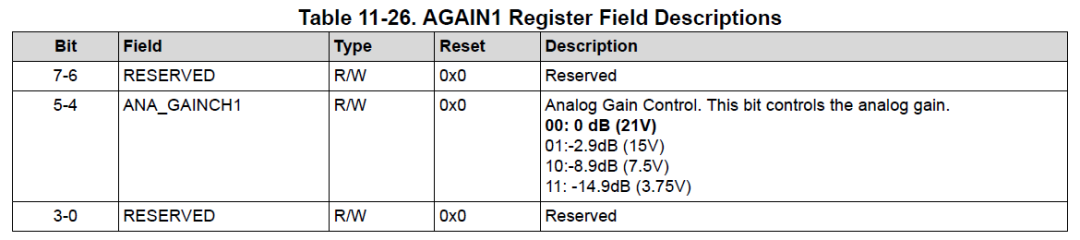

3)模拟增益

芯片支持4种模拟增益,通过GAIN1 Register (Address = 0x4A)进行设置。厂商建议选择最低的增益以优化输出噪声和动态范围的性能。

模拟增益设置只能在深度睡眠或睡眠状态下修改,当芯片在播放状态时,逐渐切换到新设置,切换速率通过寄存器

AGAIN_RAMP(Address = 0x4E)配置。

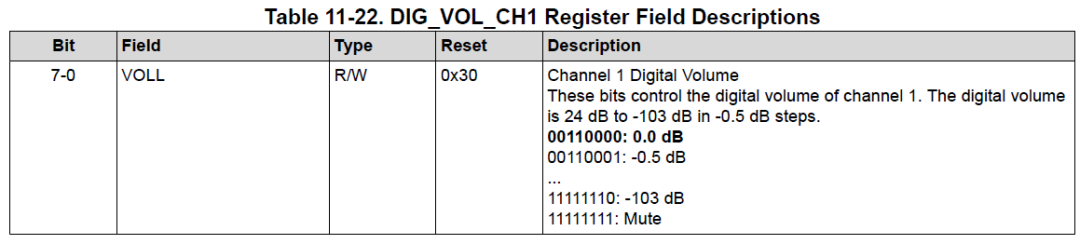

4)数字音量控制

输出通道具有数字音量控制,范围为-100dB(寄存器说明写的是-103dB,估计其中一个写错了)至+24dB,步长为0.5dB。设置通过I2C配置DIG_VOL_CH1 Register (Address = 0x40):

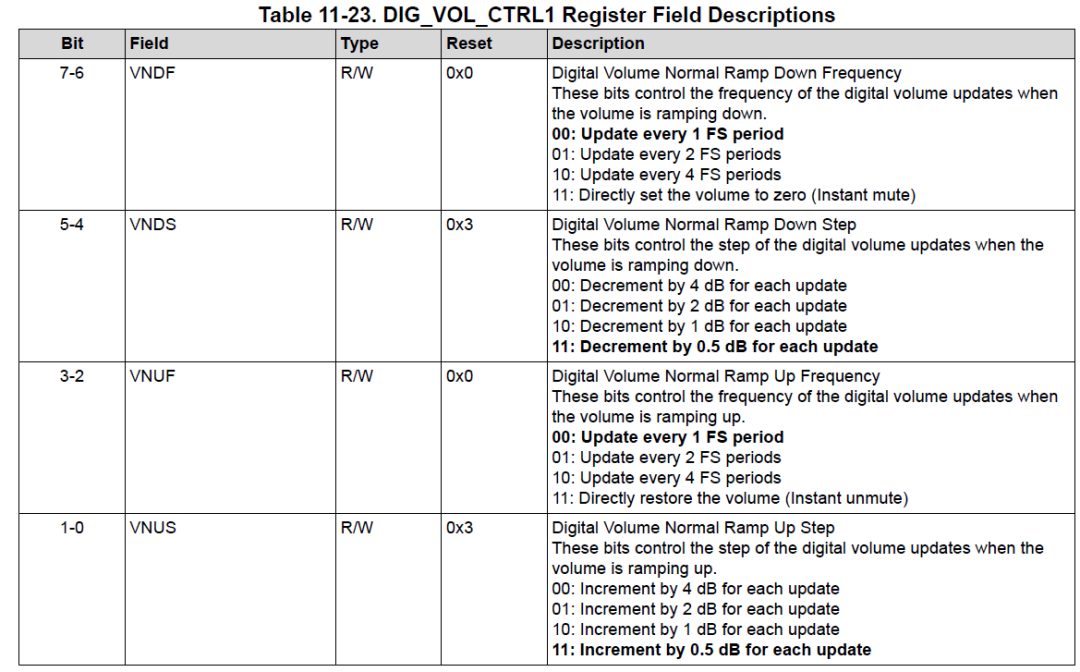

当然,步长也可设置。增益上升/下降步长可以在DIG_VOL_CTRL1 Register (Address = 0x44)中进行配置:

5)自动静音

当检测到连续的零样本数据流时,芯片可以自动设置通道静音。同时会持续监控输入通道,当有非零信号时自动恢复正常。

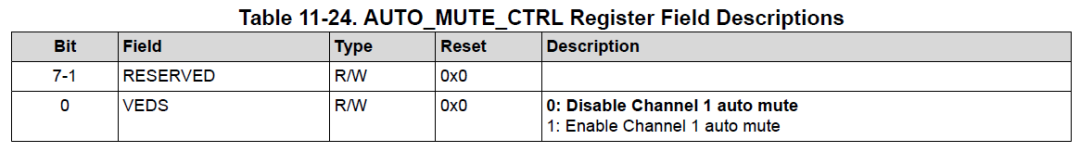

自动静音功能默认是不使能的,需要配置寄存器AUTO_MUTE_CTRL(Address = 0x47):

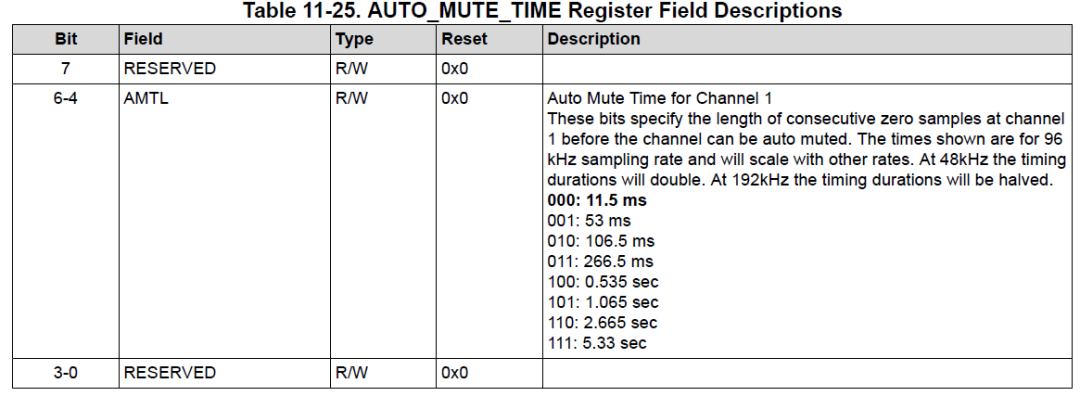

自动静音需要连续采样零信号的时间设置由寄存器AUTO_MUTE_TIME(Address = 0x48)完成:

6)双象限增益补偿

D类放大器的调制器和输出LC滤波器可能会对频率响应线性产生不利影响,导致频率下降/峰值,双象限增益补偿可以改善这种问题,不过本功能是默认关闭的,如需打开需要将相应的系数写入 DSP 存储器。

7)低延迟信号路径

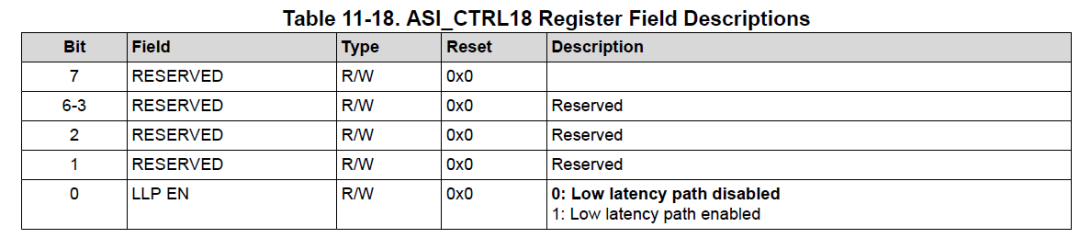

时间敏感的信号(ANC或RNC等)需要最小的处理延迟,芯片在48KHz采样频率下提供一个低延迟信号路径,有效降低70%的延迟。支持低延迟功能的采样频率只有48KHz和96KHz两个。

低延迟信号和常规音频信号路径是并行建立的,可以同时传输,两组信号在输出放大级之前混合,因此需要注意混合后信号不超过增益范围造成失真。本功能默认关闭,打开需要配置寄存器ASI_CTRL18(Address = 0x32)的bit0为1,如下:

4.扩频控制

1)调制

芯片支持3种调制:BD调制、高级1SPW调制和混合调制。

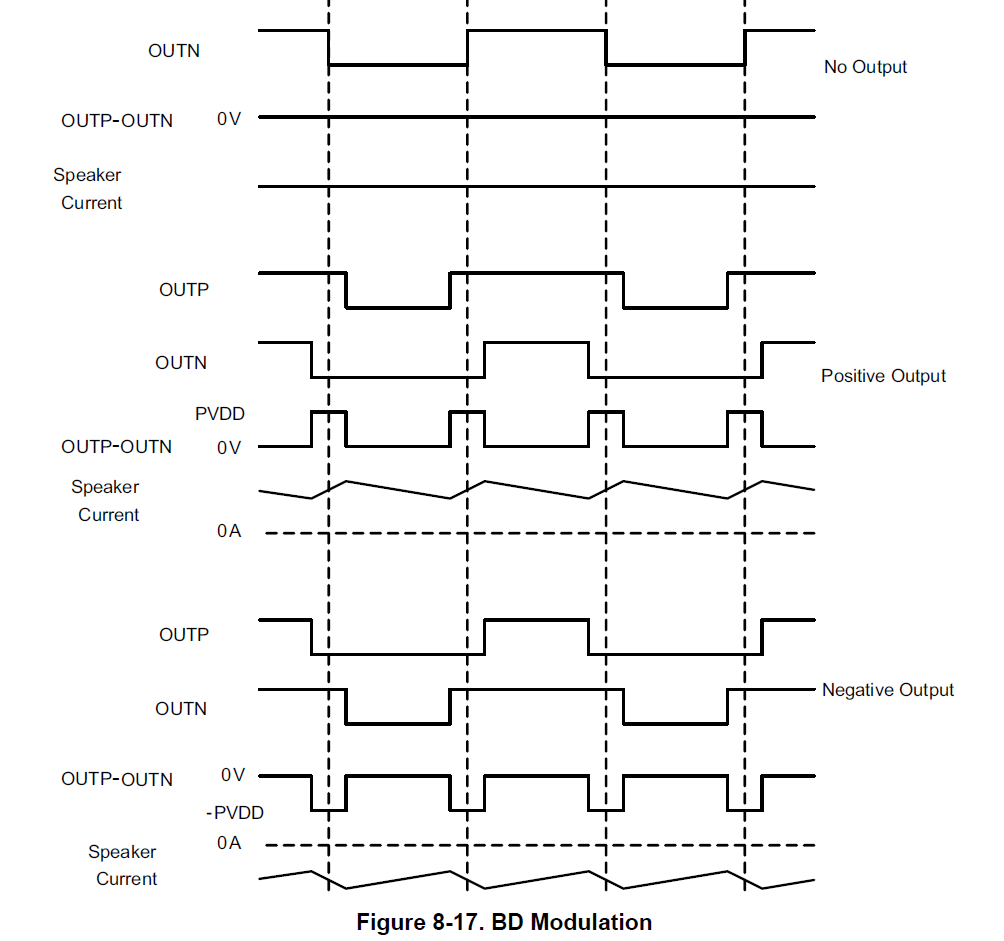

BD调制中每个输出摆幅都是0V到电源电压。在没有信号时,OUT_xP和OUT_xN彼此同相,因此喇叭无输出电流;当输出正电压时,OUT_xP的占空比>50%,OUT_xN的占空比<50%;当输出负电压时,OUT_xN的占空比>50%,OUT_xP的占空比<50%。低信号时条件下,负载两端的电压在大部分开关周期内保持在 0 V,从而减少了开关电流以及负载中的损耗。具体如下图:

高级1SPW调制有更高的效率。在空闲或低信号条件下,输出以小于20%的占空比运行,将损耗降至最低。当施加音频信号时,电桥的一个输出降低其占空比,而另一个输出侧增加。递减的输出信号降到GND。此时,所有的音频调制都是通过增加的输出进行的。结果是,在音频周期的大部分时间里,只有一个输出在切换。由于开关损耗的减少,在这种模式下效率得到了提高。

混合调制在不损害高输出功率性能的情况下将功率损失降至最低。TAS6511-Q1使用集成DSP检测输入信号电平,并根据输出功率动态调整PWM占空比和其他调制参数。混合调制实现了超低的空载电流,并保持了出色的音频性能。与1SPW或BD调制不同,混合调制必须在DSP存储器中激活才能使用。混合调制配置取决于所选的开关频率、PVDD电源电压和输出阻抗。

2)高频PWM

PWM调制器将输入音频数据转换为占空比变化的开关信号。PWM调制具有高带宽、低噪声、低失真和出色的稳定性。

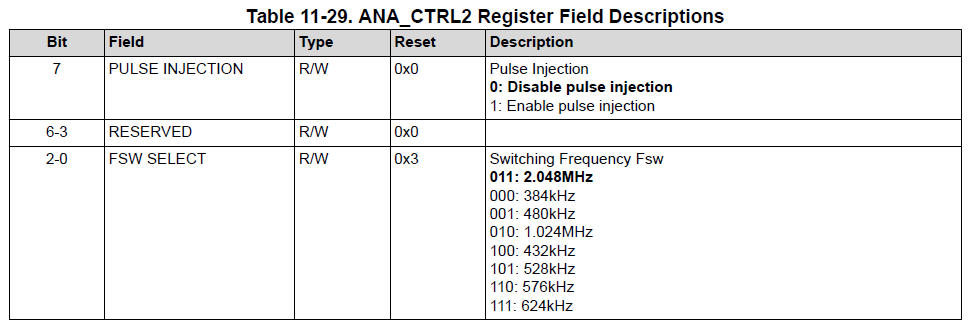

输出开关频率需使用I2C在寄存器ANA_CTRL2(Address = 0x52)中设置:

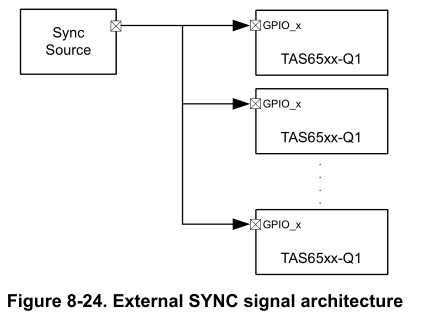

如果需要不同的PWM输出相位,可以启用HASE_CTRL0寄存器(Address=0x60)bit7中的手动相位模式。在手动模式下,必须在相位寄存器中设置通道的输出相位。

3)扩频控制

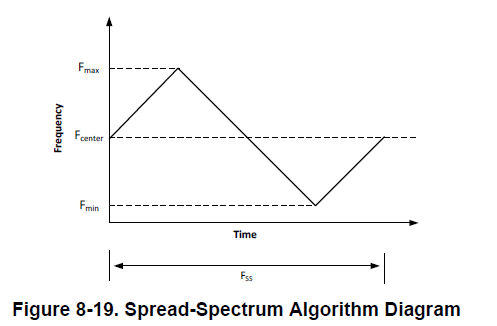

芯片支持时钟扩频调制,主要用来优化EMI。扩频调制是一种PWM调制技术,通过改变输出PWM频率来降低EMI测量中的峰值,从而产生更宽的频谱但更低的电平。

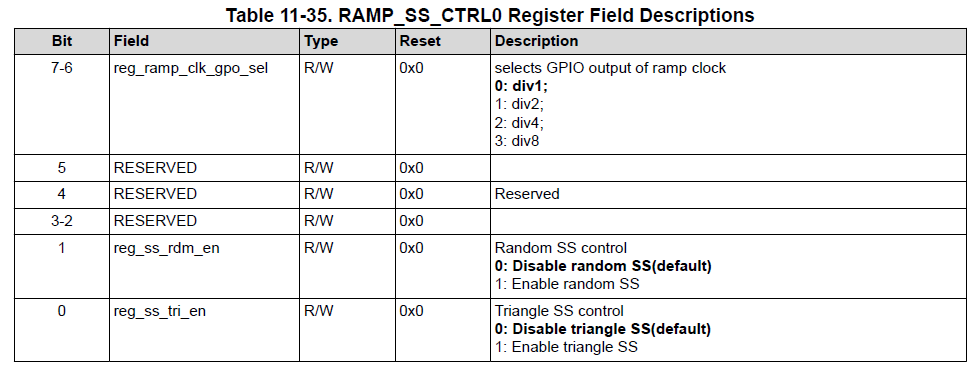

芯片支持3种扩频方案,可通过寄存器RAMP_SS_CTRL0(Address = 0x61)配置,如果bit0和1都设置为0则关闭扩频调制:

-

三角形

-

随机

-

三角形+随机

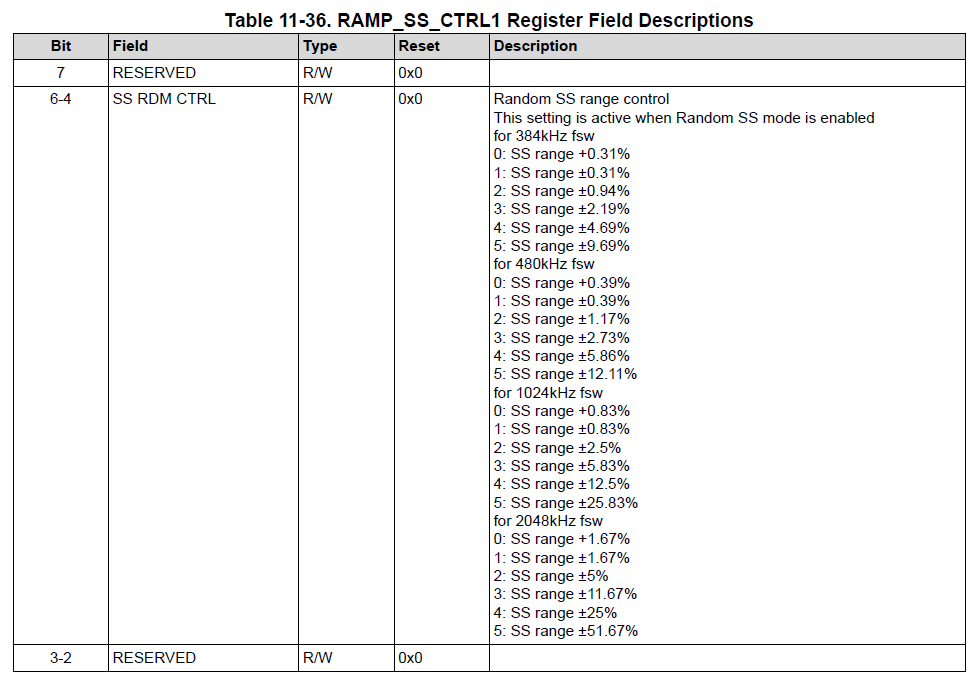

扩频频率范围和扩频调制频率Fss通过寄存器RAMP_SS_CTRL1(Address =0x62)设置。

4)栅极驱动

栅极驱动器接受低压PWM信号并对其进行电平转换,以驱动高电流、全桥、功率FET级。栅极的电源电压GVDD由内部产生,需要GVDD_BYP管脚外接一个去耦电容。

全H桥输出级仅使用NMOS晶体管。因此,高侧NMOS晶体管的正常工作需要自举电容器,要求质量为X7R或更高的0.22uF陶瓷电容器从每个输出端连接到相应的自举输入端,其额定值应与施加的电压相匹配。连接在BST管脚和相应输出之间的自举电容器用作高侧N沟道功率MOSFET栅极驱动电路的浮动电源。在每个高侧开关周期中,自举电容器保持VGS的高电压,使高侧MOSFET保持导通。

5.负载诊断

负载诊断包括直流和交流负载诊断,其中DC诊断默认是打开的。

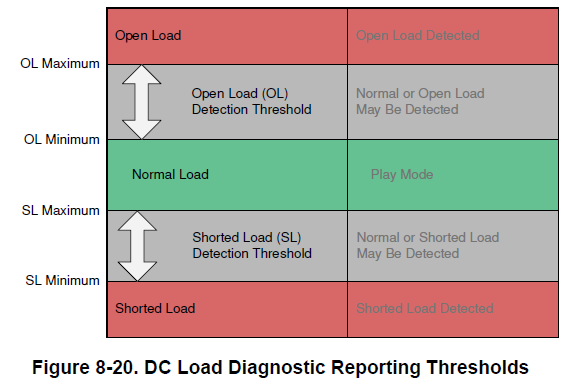

1)DC负载诊断

直流负载诊断用于检查负载是否正确连接。

电源在正常范围内时,一旦不在深度睡眠模式,直流负载诊断就会有效。诊断包括:

-

输出对地短路

-

输出对电源短路

-

OUT_M和OUT_P短路

-

OUT_M或OUT_P开路

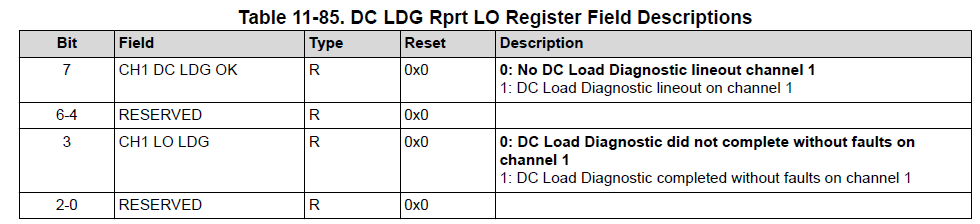

如果检查没有报错,则DC LDG RprtLO(Address = 0xC2)寄存器bit3置1,否则置0.

当有报错时,每750ms检测一次,直到报错消失或者I2C控制关闭诊断功能。

2)线路输出诊断

芯片支持可选的线路输出负载检测,在检测期间通道需要静音。检测结果记录在寄存器DC LDG Rprt LO(Address = 0xC2)中。

3)交流负载诊断

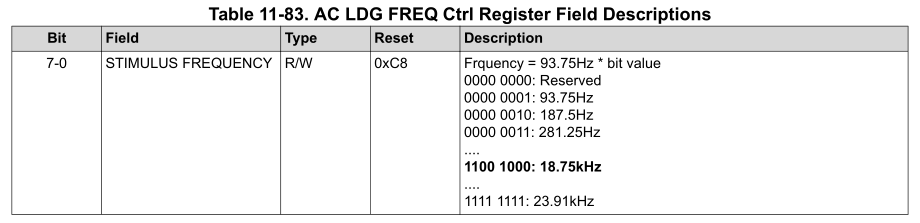

当与无源分频器一起使用时,交流负载诊断用于确定电容耦合扬声器或高音扬声器的是否正确连接。本诊断可以通过I2C控制。诊断原理就是内部产生激励信号,然后捕获负载响应的实部和虚部,预估其幅值和比较器对比判断。激励是一个低电平、10mA的驱动电流,不会对喇叭产生明显的声压。其频率通过寄存器AC LDG FREQ Ctrl (Address = 0xB8)配置如下:

如果负载阻抗低于8Ω,建议将寄存器AC LDG Ctrl 1(Address = 0xB5)的AC DIAG GAIN位设置为1,以提高分辨率。

交流负载诊断工作工程:

-

使用STATE_CTRL0寄存器(Address = 0x3)配置通道进入睡眠状态;

-

AC LDG Ctrl 1寄存器(Address = 0xB5)启动交流诊断;

-

在寄存器DEVICE STATE REPORT(Address = 0x72)轮训通道状态,一旦反馈通道为睡眠状态,则可读取交流诊断结果;

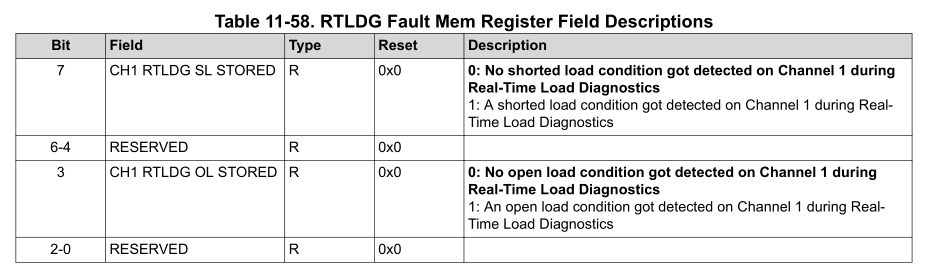

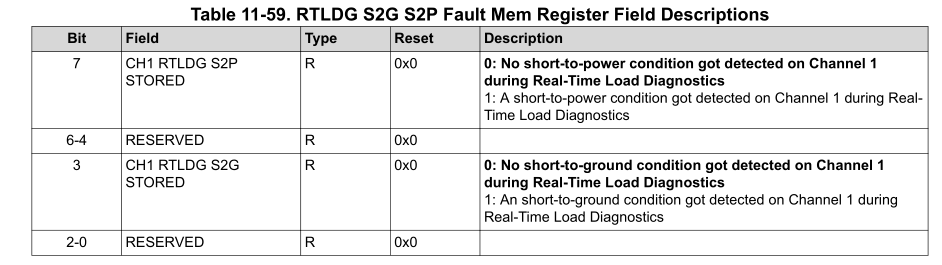

4)实时负载诊断 (RTLDG)

RTLDG可以在播放状态下检测短路(SL)、开路(OL)、短电源(S2P)和短地(S2G)。芯片内部集成了电流感测电路,可以测试通道输出阻抗,通过和设置的阈值比较判断状态。芯片内部有导频音,可不依赖外部输入信号即可连续检测输出阻抗,默认的话导频音是 5.86 Hz, -36 dBFs的信号。

另外RTLDG仅在采样频率为f 16 kHz, 32 kHz, 48 kHz和96 kHz时支持,192KHz不支持。同时要是能电流感测。

SL/OL和S2P/S2G可以单独启用或关闭,也可以并行使用。SL/OL检测是根据计算出来的输出阻抗判断;S2P/S2G是通过判断OUT_M和OUT_P上的电流大小完成。

输出限幅和限流能力会对结果产生影响,建议在RTLDG期间关闭它们。如果打开限幅功能,则RTLDG的结果不会更新。

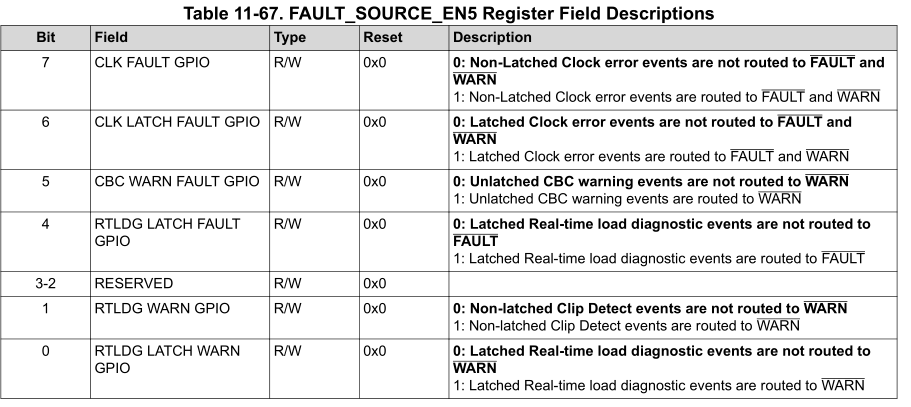

SL和OL的结果在寄存器 RTLDG Fault Mem(Address = 0x8B)记录,S2P和S2G的结果在寄存器RTLDG S2G S2P Fault Mem中记录。这些事件可以映射到WARN或FAULT管教输出,需要在寄存器FAULT_SOURCE_EN5 (Address = 0x94)内配置。如果出现这些错误,则会进入到错误状态中。

6.保护和监控

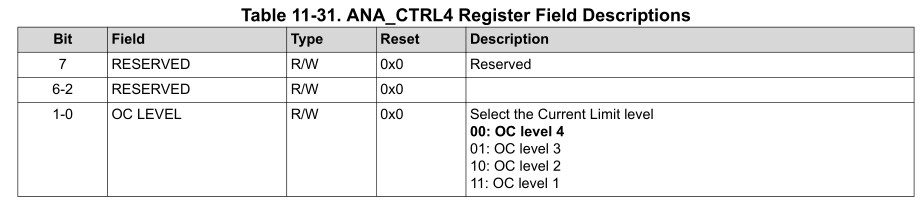

1)过流保护

在正常操作下,在播放高音量音乐时,负载电流可能会超过芯片的最大负载电流ILIM。在这些情况下,设备会动态限制进入负载的电流,播放会继续进行而不会中断,并防止因瞬态音乐事件而意外关机。

芯片有4个过流限制level,在ANA_CTRL4 Register (Address = 0x55)中设置。

如果在21.3内有超过25%是过流状态,则会在对应通道产生一个报警事件。如果报价事件持续超过170.4ms,则会产生一个过流错误事件,导致通道进入到错误状态,输出为高阻态。

2)过流关机

如果负载电流超过ISD,就会出现过流关机事件(OCSD),芯片会限制输出电流并关闭对应通道(错误状态,输出高阻态),芯片的FAULT管脚输出一个低电平。具体关闭时间依据短路严重程度而定。

过流限制值也可通过寄存器 ANA_CTRL4(Address= 0x55)配置不同level。

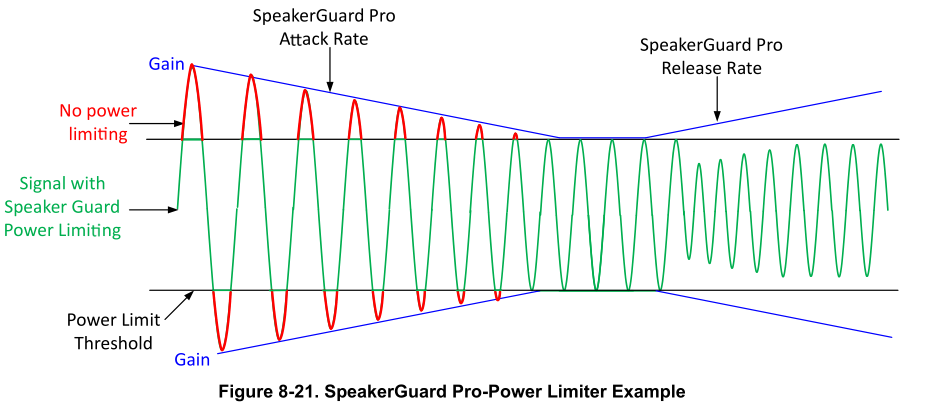

3)喇叭功率限制

如果输入信号超过配置的峰值电压阈值,新品将自动减低增益来把信号削波到配置的阈值,以避免潜在地损坏扬声器。信号降低到阈值以下时,增益可自动恢复。电压限值、释放速率、最大衰减等参数可在DSP存储器中设置。

本功能默认关闭,如需打开,DSP_CTRL1 Register (Address= 0x39)的bit6设置为1即可。

4)直流检测

该电路在正常运行期间连续测量放大器输出端的直流偏移。如果偏移超过DCfault阈值,就会触发DC错误时间,导致输出为高阻抗状态,FAULT管脚输出低电平。

5)温度保护和监控

芯片内部集成了温度传感器,如果结温超过OTSD阈值,该通道将关闭,FAULT管脚输出低电平。如果使能了过温自动恢复,则在温度降低后自动恢复到之前的状态;如关闭了过温自动恢复功能,芯片将进入错误状态,只有寄存器MODE_CTRL (Address = 0x1)的bit3被设置成1(清空错误)后才可恢复正常。

在过温关机(OTSD)之前还有一个状态是过温告警(OTW),这个状态不会进入FAULT状态,只会有一个告警事件产生,可以通过I2C读取或者硬件管脚输出。过温告警阈值有7个不同的level可设。

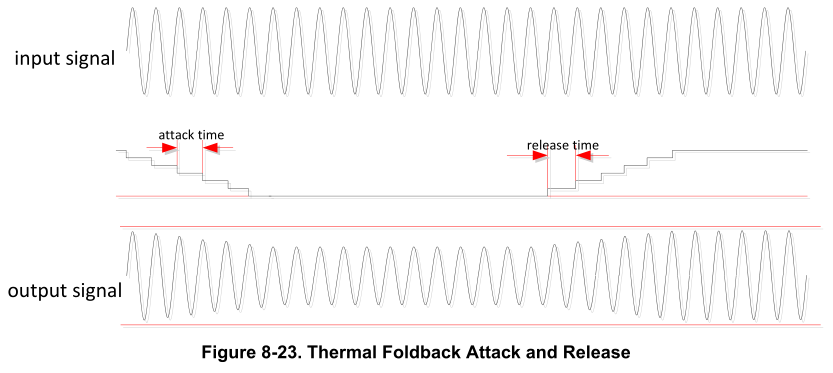

5)热增益Foldback

本功能主要是保护芯片,尽量不进人过温关机状态。当温度超过阈值时,本功能会比较平滑降低增益;当温度降下来,则会逐步恢复增益。这样芯片就不会简单的关闭通道,提高体验。

6)电源错误

PVDD电源有两种错误:低压错误和过压错误,触发就会有电源错误事件,导致关机。DVDD也有保护,当DVDD低于VPOR_OFF,会触发DVDD POR错误事件,并关机。

7.控制管脚

1)PD管脚

PD是低有效信号,当有效时芯片会关机,电流降到最小值,内部所有模块全部断电,下次启动时所有寄存器恢复默认值。该管脚内部集成了1一个110KΩ的下拉电阻。

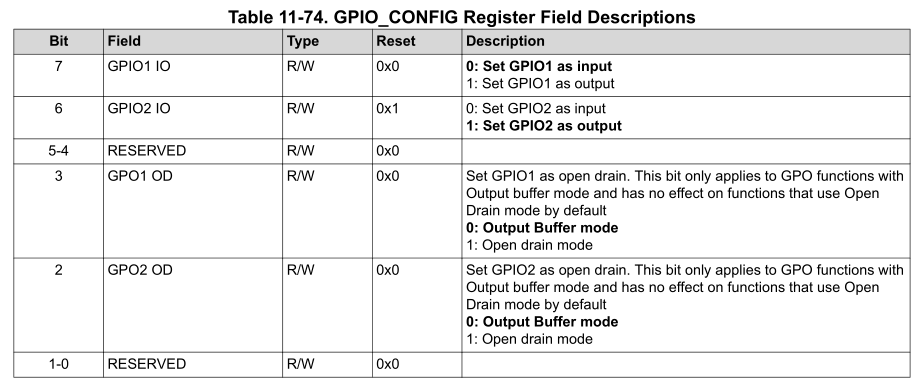

2)GPIO管脚

芯片有2个控制IO,都可以配置成输入或者输出。它们的具体功能需要在上电初始化和上电复位之后,且在正常工作之前通过I2C配置。默认的话,GPIO_1是一个输入管脚,GPIO_2是FAULT管脚;具体可在GPIO_CONFIG寄存器中配置:

FAULT管脚的功能就是在以下情况时发出一个低电平信号:

-

过温关机OTSD;

-

过流关机事件;

-

直流偏移事件;

还有一些错误警报可以屏蔽,不在FAULT管脚上体现:

-

电源错误;

-

直流负载诊断错误;

-

实时负载诊断报告;

-

时钟错误;

-

警告事件;

本管脚开漏输出,内部有一个110 kΩ的上拉电阻器连接到DVDD。

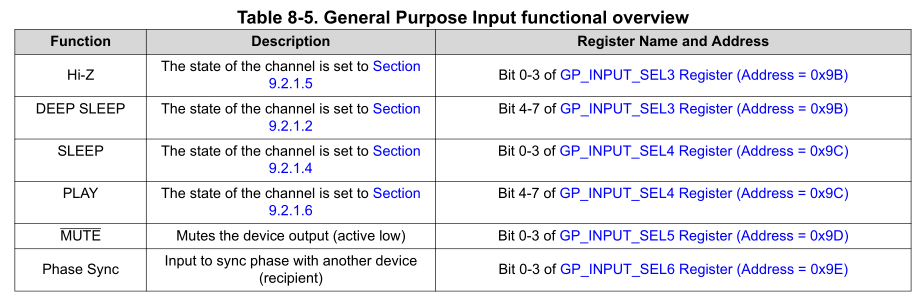

另外一个管脚作为输入管脚时,可以配置成如下功能:

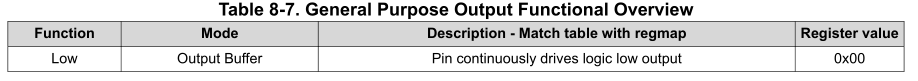

作为输出管脚时,可以配置为如下功能:

4)STBY管脚

任何GPIO管脚都可以配置为低有效的STBY。有效时,芯片进入深度休眠状态,输出管脚进入高阻抗状态,内部模拟部分电源关闭,但是I2C和内部寄存器是有效状态。

本管脚内部集成了一个110KΩ的下拉电阻。

5)高级GPIO功能

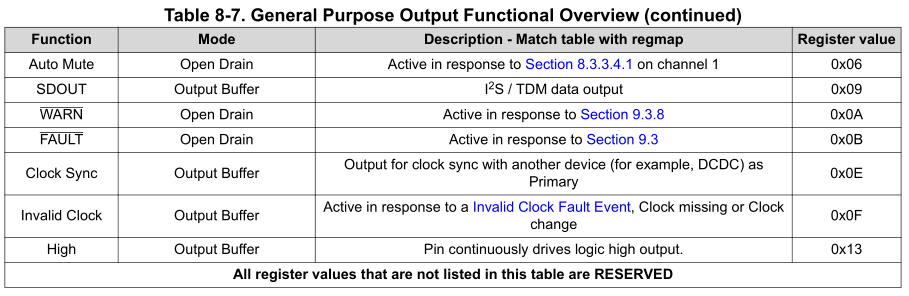

芯片支持多种时钟同步选项,以改善系统EMI并控制电源峰值电流。

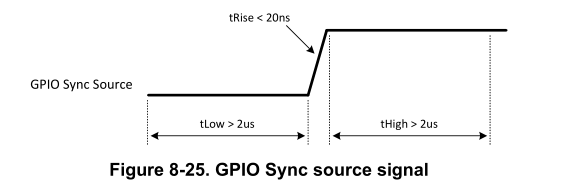

第一种是外部时钟输入,如下:

首先将一个GPIO引脚设置为“相位同步”输入,所有芯片的该GPIO连在一起;

其次RAMP_PHASE_CTRL0 Register (Address = 0x60)中将bit0设置为1,bit1设置为0;

然后为每个设备及其各自的通道选择输出相位设置;

接着所有同步设备的输出通道设为高阻态;

之后切换GPIO同步源;

最后设所有通道为播放状态即可。

第二种是使用音频总线的SCLK信号,

大概需要六步:

-

中止SCLK信号,I2C仍然使能;

-

RAMP_PHASE_CTRL0 Register (Address = 0x60)中将bit0和bit1均设置为1;

-

为每个设备及其各自的通道选择输出相位设置;

-

所有同步设备的输出通道设为高阻态;

-

开始发送SCLK信号,并在等待至少2ms;

-

设所有通道为播放状态;

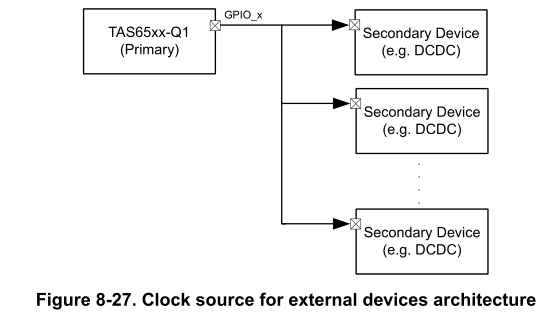

第三种是TAS6511-Q1作为时钟源,

总共5步配置:

-

选择TAS6511-Q1作为主时钟运行,设置GPIO为时钟输出,并连接到其他设备的时钟输入管脚上;

-

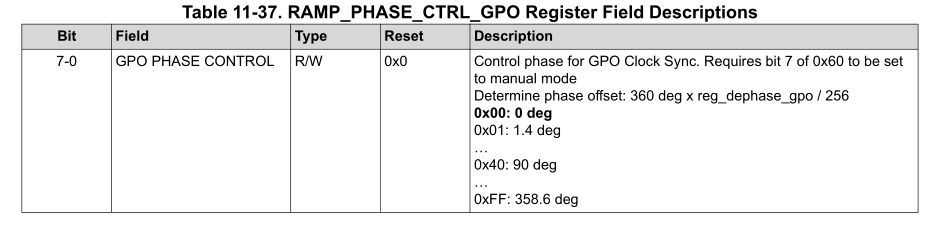

RAMP_PHASE_CTRL0 Register (Address = 0x60)中将bit0设置为1;

-

时钟同步将相对于输出通道以0度的相位偏移。如设置不同相位,需在RAMP_PHASE_CTRL_GPO Register (Address = 0x68)中进行设置;

-

所有同步设备的输出通道设为高阻态;

-

设所有通道为播放状态;