相关阅读

Verilog基础![]() https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482

Verilog中的端口定义有两种风格,一种是Verilog Standard 1995风格,一种是Verilog Standard 2001风格,本文将对Verilog Standard 1995风格进行详细阐述。

首先来看一下模块定义的BNF范式(语法),有关BNF范式相关内容,可以参考之前的文章。

Verilog基础:巴科斯范式(BNF)![]() https://blog.csdn.net/weixin_45791458/article/details/132567389?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522172381461616800207085955%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fblog.%2522%257D&request_id=172381461616800207085955&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~blog~first_rank_ecpm_v1~rank_v31_ecpm-1-132567389-null-null.nonecase&utm_term=BNF&spm=1018.2226.3001.4450

https://blog.csdn.net/weixin_45791458/article/details/132567389?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522172381461616800207085955%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fblog.%2522%257D&request_id=172381461616800207085955&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~blog~first_rank_ecpm_v1~rank_v31_ecpm-1-132567389-null-null.nonecase&utm_term=BNF&spm=1018.2226.3001.4450

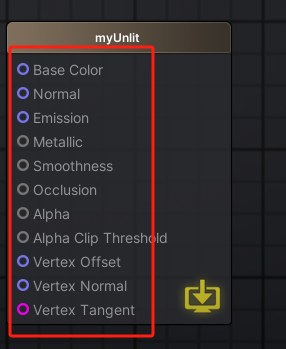

图1 模块定义的BNF范式

从上图可以看出,module_declaration有两种形式,由符号|分隔:前一种使用list_of_ports形式的是Verilog Standard 1995风格;后一种使用list_of_port_declarations形式的是Verilog Standard 2001风格,这是一种ANSI C风格的形式(对于一个模块来说,只能二选其一)。

图2将图1中与端口定义有关的语法单独列出来了。

图2 端口定义的BNF范式

下面将对Verilog Standard 2001风格端口定义的格式进行逐步分析。

list_of_port_declarations

list_of_port_declarations是用小括号包围的一个或多个port_declaration(如有多个,用逗号分隔),它还可以只是简单的左右括号,表示没有一个没有输入输出端口的模块(比如testbench)。有三个类型的port declaration:输入端口声明、输出端口声明和双向端口声明,它们的BNF范式如图3所示。

图3 端口声明的BNF范式

从图3中我们可以看出,输入端口和输出端口有可选的net_type,这是因为输入端口的连接就像是一个assign连续赋值,作为等号左边的信号自然得是net大类(图4所示,除了trireg类型),其中wire类型最常用。

图4 net大类

输出端口则没有这些限制,所以它可以是net大类(除了trireg类型),也可以是variable大类中的reg,integer和time类型。

port declaration可以用net_type,reg,signed,range,描述一个信号的信息。

与Verilog Standard 1995风格不同的是, Verilog Standard 2001风格能够减少端口定义时的重复说明,如下例所示。

// 1995风格的端口声明

module my_module (input1, input2, output1, output2);// 端口方向和位宽定义input [7:0] input1;input [7:0] input2;output [7:0] output1;output [7:0] output2;// 信号类型定义wire [7:0] input1;wire [7:0] input2;reg [7:0] output1;reg [7:0] output2;// 逻辑实现// ********

endmodule// 2001风格的端口声明

module my_module (input wire [7:0] input1,input wire [7:0] input2,output reg [7:0] output1,output reg [7:0] output2

);// 逻辑实现// ********

endmodule但Verilog Standard 2001风格不支持Verilog Standard 1995风格中的显式端口的特性,即.port_identifier加上可选的port_expression这种形式。同时也不支持port_reference拼接,且port_reference必须是一个简单的标识符(包括转义标识符)而不是向量的常量位选或常量域选(见图中的constant_range_expression)。

不能使用net declaration或variable declaration对其再次进行声明也导致了不能使用[delay3]可选项和线网声明赋值(尽管这很少见),即如下所示的Verilog Standard 1995风格的特性。

module examlpe(a, b);// port declarationinput a;input [1:0] b;// additional declarationwire a=1'b1; // 线网声明赋值wire [1:0] #1 b; // [delay3]endmoduleVerilog基础:模块端口(port)定义的语法(1995标准)![]() https://blog.csdn.net/weixin_45791458/article/details/141254289?csdn_share_tail=%7B%22type%22%3A%22blog%22%2C%22rType%22%3A%22article%22%2C%22rId%22%3A%22141254289%22%2C%22source%22%3A%22weixin_45791458%22%7D

https://blog.csdn.net/weixin_45791458/article/details/141254289?csdn_share_tail=%7B%22type%22%3A%22blog%22%2C%22rType%22%3A%22article%22%2C%22rId%22%3A%22141254289%22%2C%22source%22%3A%22weixin_45791458%22%7D