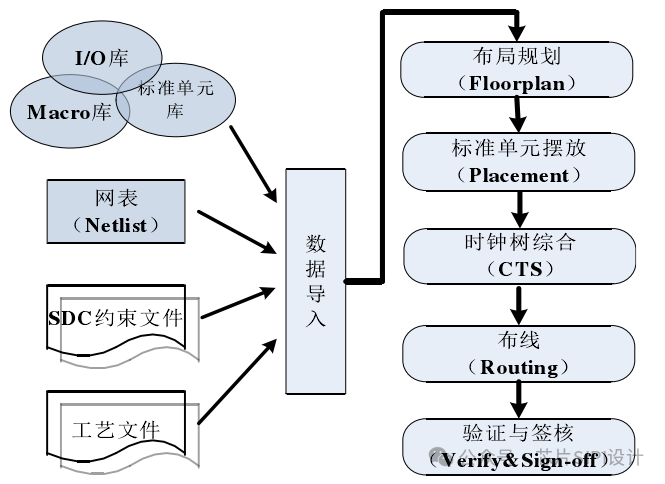

芯片设计的物理实施过程通常也简称为布局布线(P&R,Place-and-Route),布局一般被分为布局规划(Floorplan)和标准单元摆放(Place)两个过程。而其中的布局规划是芯片后端物理实现过程的重要环节,其合理性直接影响到芯片的时序收敛、电源稳定程度及其可靠性。

布局规划基本理论

布局规划是芯片后端设计过程中最初的部分,同时也是很重要的一环,它的设计结果将决定芯片的面积,影响布线资源、时序收敛以及芯片的稳定性。

布局规划主要包含对芯片面积(Die Size)、宏单元(Macro)及输入输出(I/O)等单元的规划,是对芯片内部结构的完整规划与设计,同时也为之后的标准单元(Stand Cell)摆放及布线做好准备。