反射二进制码(RBC),也称为反射二进制(RB)或格雷码(Gray code),得名于Frank Gray,是二进制数制的一种排列方式,使得连续两个值之间仅有一个比特(二进制位)不同。格雷码在数字电路中的应用有助于减少误差、提高系统的可靠性,并简化逻辑操作,因此被广泛应用于各种数字系统和电子设备中。

格雷码的最主要特点:各个相邻码之间仅有一位状态不同,首尾也是仅有一位状态不同

在现代数字通信中,格雷码在错误纠正中扮演着重要的角色。例如,在诸如QAM这样的数字调制方案中,数据通常以4位或更多位的符号传输,信号的星座图被安排成相邻星座点传达的位模式仅相差一个比特。通过结合能够纠正单比特错误的前向错误纠正,接收器可以纠正导致星座点偏离到相邻点区域的任何传输错误。这使得传输系统对噪声的影响更小。

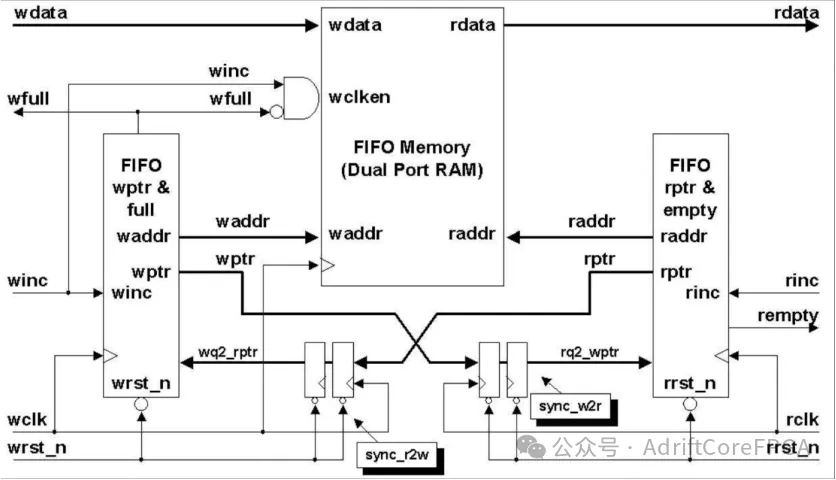

格雷码在FIFO中的应用

在FIFO的设计中,在写请求中,写地址在写时钟作用下递增,在产生FIFO满信号时,需要将写地址和读地址进行比较,由于两个地址分别与其各自的时钟同步,但是彼此之间又是异步的关系,所以在使用二进制计数器实现地址的时候,就会出现现取样值错误的问题。如果我们有多个信号线(例如,4位计数器),并且这些信号线的延迟不一致,即skew不同,使用异步时钟采样更容易错误。为了避免这一问题,FIFO计数指针的常见方法是使用格雷码计数器。格雷码每个时钟转换只允许一位改变,从而消除了尝试在同一时钟边缘上同步多个改变信号所带来的问题。

使用格雷码编码地址可以减少在不同时钟域之间发生的时序问题,提高跨时钟FIFO的可靠性和性能。

- 将格雷码转换为二进制

- 根据条件递增二进制值

- 将二进制转换为格雷码

- 将计数器的最终格雷码保存至寄存器中

Verilog 语言描述二进制码转换为格雷码

module bin_to_gray (bin, gray);

parameter SIZE = 4;

input [SIZE-1:0] bin;

output [SIZE-1:0] gray;

assign gray = (bin >> 1) ^ bin; //右移与自己异或

endmodule

Verilog 语言描述格雷码转换为二进制码:

module gray_to_bin (bin, gray);

parameter SIZE = 4;

input [SIZE – 1:0] bin;

output [SIZE – 1:0] gray;

reg [SIZE – 1:10] bin;

integer i;

always @ (gray)

for ( i = 0; i <= SIZE; i = i + 1)

bin[i] = ^(gray >> i); //右移一位并按位异或

endmodule

所以一般用FIFO的空满指示比较地址的时候会使用到格雷码。

![[羊城杯 2020]Blackcat1](https://i-blog.csdnimg.cn/direct/1f540352b08446b7ad52b1eac870ad98.png)