文章目录

- 前言

- 一、TC397简介

- 二、命名规则

- 三、多核开发建议

前言

AURIX™ TC3xx微控制器架构具有多达6个独立的处理器内核CPU0…CPU5, 可在一个统一平台上无缝托管多个应用程序和操作系统.

由于实现了具有独立读取接口的多个程序Flash模块, 该架构支持进一步的实时处理.

AURIX™专为性能,安全性和安全性而设计,具有并行执行流程,锁步核心和进一步增强的硬件安全机制的功能

一、TC397简介

Infineon Aurix TC397是一款高性能的微控制器,专为智能汽车域控制和其他工业应用领域设计。它具有高达六核的架构。以下是对TC397的简单介绍:

6个CPU核的高性能微控制器

6个32位超标量哈佛(Superscalar Harvard)架构的TriCore CPUs (TC1.6.2P),具有以下特性:

——超高的实时性能

——强大的位处理能力

——超强集成DSP能力

——乘法累加(Multiply Accumulate)单元,每周期可维持2次MAC(Multiply Accumulate)操作

——所有CPU都有32位浮点单元(Floating point unit-FPU), 符合IEEE-754的单精度, 每个周期2个FLOP(流水线)

——在温度范围内最高支持300MHz操作

——Data Scratch-Pad RAM (DSPR)最高支持240/96K字节

——Instruction Scratch-Pad RAM (PSPR)最高支持64K字节

——Data RAM (DLMU)最高支持64K字节

——32K字节的指令缓存(Instruction Cache-ICACHE)

——16K字节的数据缓存(Data Cache-DCACHE)

——所有嵌入式NVM和SRAM都受ECC保护

——最高16M字节的程序存储器(Program Flash Memory-PFLASH)

——最高1M字节的数据存储器(Data Flash Memory-DFLASH0)用于EEPROM仿真

——BootROM (BROM)

——用于总线主机、CPU和存储器之间高速并行访问的64位Cross Bar Interconnect (SRI)

——用于片上外设和功能单元的32位System Peripheral Bus (SPB)

——SRI到SPB的总线桥(SFI Bridge)

——硬件LIN支持(V1.3、V2.0、V2.1和J2602)最高可达50M波特率的8路同步/异步串行通道

——6路支持主从模式的QSPI,最高支持50 Mbit/s

——2路支持串行内部处理器通信的高速串行链路(HSSI),最高支持320 Mbit/s

——4路串行微秒总线接口(Micro Second Bus-MSC),用于串口扩展到外部电源设备

——3路MCMCAN模块和4个CAN节点,通过FIFO缓存实现高效数据处理

——25路单边半字节传输(Single Edge Nibble Transmission-SENT)用于传感器的连接

——2个FlexRay带有2路通道(E-Ray),支持V2.1

——1个通用定时器模块( Generic Timer Module-GTM)提供强大的数字信号滤波和定时器功能,实现自主和复杂的输入/输出管理

——1个6路捕获/比较模块(两个内核CCU60和CCU61)

——1个12路通用定时器单元(GPT120)

——符合V1.3(PSI5)标准的4路通道外围传感器接口

——1路符合串行PHY(PSI5-S)的外围传感器接口

——2路符合V2.1标准的内部集成电路(Inter-Integrated Circuit-I2C)总线接口

——1路符合IEEE802.3协议,支持RMII和MII接口的以太网MAC

——1路外部总线接口(external Bus interface-EBU)

——20路独立ADC内核组成的集群

——输入电压范围为0V~5.5V

——多核调试,实时跟踪和校准

——4线/5线JTAG(IEEE 1149.1)或DAP(Device Access Port)接口

——符合汽车AEC-Q100

——满足ISO 26262功能安全规范,可达到ASIL-D

具体可查阅Datasheet & Usermanual:AURIX™ Family – TC39xXX

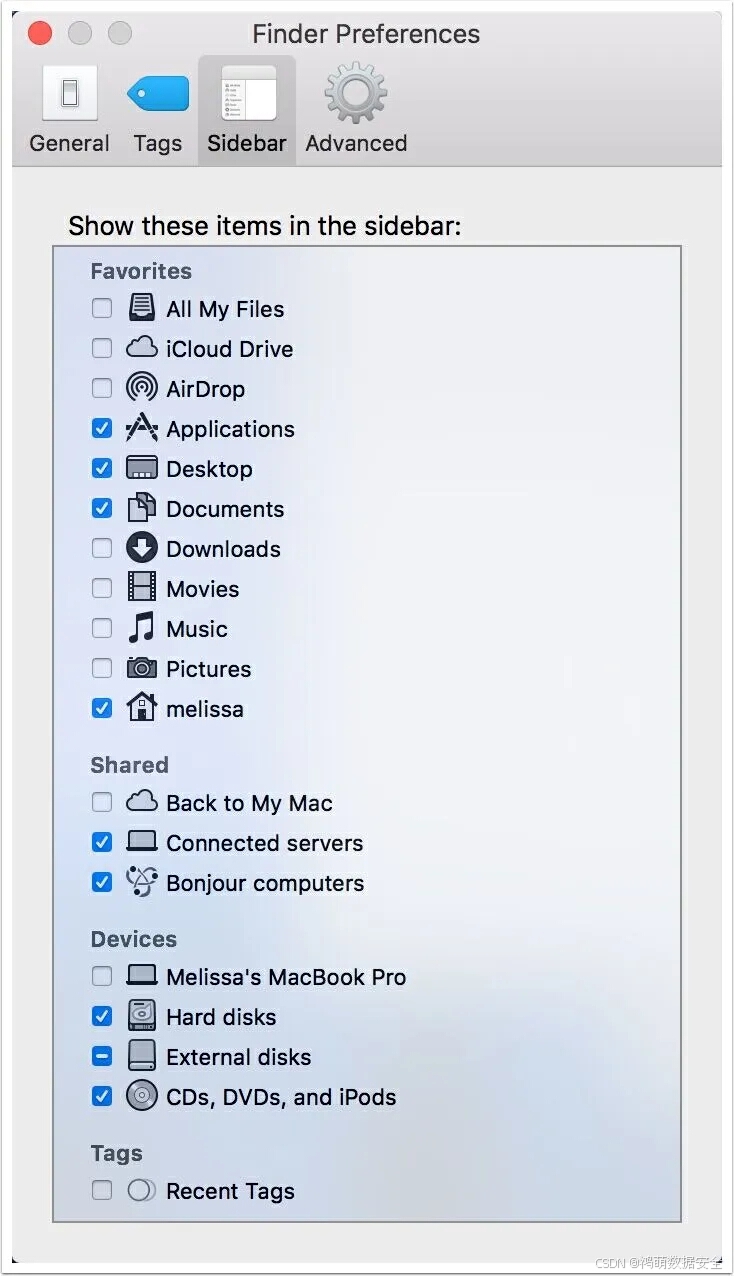

二、命名规则

三、多核开发建议