简介

框架图

本章节主要针对MIG读写做详细介绍,首先创建BLOCK DESIGN,工程连接如下图所示:

MIG IP介绍

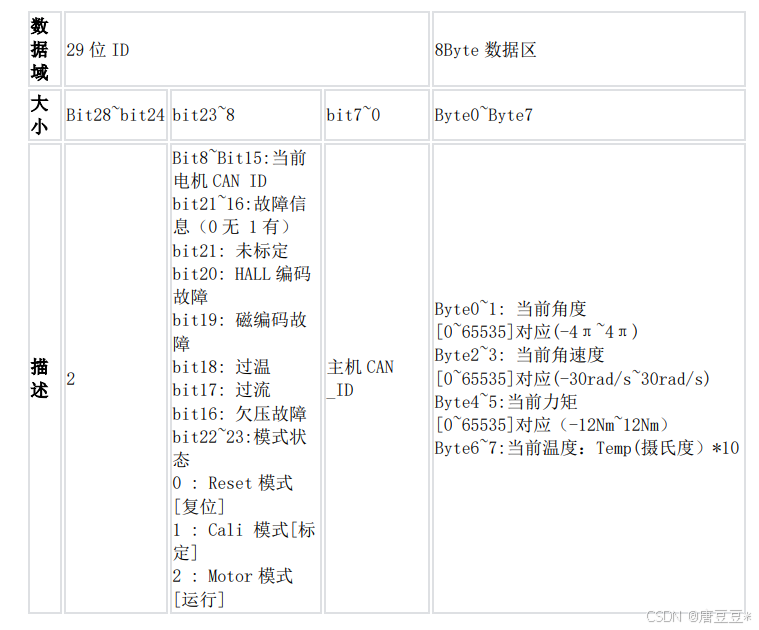

DATAMOVER的配置这里不再做介绍,结合上篇文章讲到DATAMOVER对BRAM进行读写操作,这里通过AXI桥再加一个MIG模块,MIG模块的配置和说明如下:

1、Clock Period:设置DDR3的IO时钟频率,根据开发板上实际DDR3支持的最大时钟频率进行设置,MT41K256M16TW-107IT最大支持933MHz的接口时钟,本次设计设置为400MHz的数据时钟。

2、PHY to Controller Clock Ratlo:FPGA给DDR3芯片提供的时钟频率为Clock Period,但是FPGA内部其余模块的时钟一般是运行不到Clock Period这么高的时钟频率的,所以需要给FPGA内部提供一个较低的时钟,这个参数就是用来设置DDR3接口时钟与MIG IP提供给FPGA内部其他模块的时钟(ui_clk)频率比值。本次设计的比值固定为4:1。由于ui_clk与DDR3接口时钟频率比值为1:4,ui_clk时钟为100MHz,可以作为系统时钟工作。

3、Vccaux_io:设置bank的供电电压,一般都是锁死的,会根据DDR3时钟频率变化而变化。

4、Memory Type:一般选择Components即可,其余几种可能与内存条有关。

5、Memory Part:选择DDR3的型号,芯片类型不同会涉及具体的DDR3时序参数不同以及地址线和数据线的位数不同。

6、Memory Voltage:选择芯片引脚的电平标准,DDR3一般只有1.5V和1.35V两种,根据原理图选择支持的电平的类型即可。本次设计选用1.35V。

7、Data Width:DDR3读写数据位宽,根据原理图选择DDR3位宽。本次设计将位宽设置为64。

8、ECC:数据线多余72为才能使用的功能。

9、Data Mask:启用之后,可以通过一个掩膜信号去控制DDR3写入数据,本质就是去控制DDR3的DM引脚,一般也不会使用此功能。

10、Number of Bank Machies:选择bank数量,DDR3虽然有8个bank,但是如果不需要全部使用时,可以只选择部分bank,降低功耗,节约资源,默认使用4个bank。

11、ORDERING:DDR控制器调度命令的顺序的配置,当选择strict时,严格按照命令先后顺序执行;选择normal时,为了得到更高的效率,可能对命令重排序。

Data Width:表示axi_full接口读写数据的位宽。

Arbitration Scheme:仲裁机制,由于DDR3芯片只有一组数据,而axi_full的读、写接口支持同时传输数据。当选用“TDM”时,读、写操作同时到达时,将交替进行。由于MIG IP自带仲裁机制,用户侧就不需要再考虑读写仲裁问题。

Narrow Burst设置位0即可。

1.Input Clock Period:MIG IP 核的系统输入时钟周期,该时钟一般由晶振直接提供,本设计输入200MHz差分时钟信号;

2.Read Burst Type and Length:突发类型选择,突发类型有顺序突发和交叉突发两种ÿ