雷击是一种危险的静电放电事件,其中两个带电区域会瞬间释放高达 1 千兆焦耳的能量。雷击就像一个短暂而巨大的电流脉冲,会对建筑物和电子设备造成严重损坏。雷击可分为直接和间接两类,其中间接影响是由于感应能量耦合到靠近雷击位置的物体。间接雷击在许多电子应用中更为常见,尽管感应电流小于直接雷击,但仍可能造成严重问题。本文将重点介绍使用 Ansys HFSS 和电路联合仿真模拟间接雷击对多层印刷电路板的影响的示例工作流程。

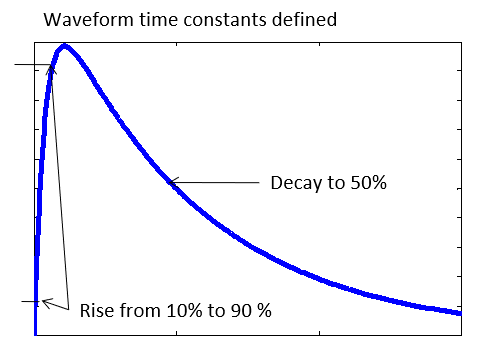

雷电波形呈现双指数特征形状,如下所示。由一系列较小振幅脉冲组成的多次雷击也会出现,但本例使用第一次雷击,因为它总是最严重的。已经制定了雷电波形标准,该标准定义了峰值振幅从 10% 到 90% 的上升时间和从峰值振幅到 50% 的衰减时间,可用于在模拟中对雷电脉冲进行建模。示例标准包括用于国防应用的 MIL-STD-464 和用于配电应用的 ANSI/IEEE C62.41。

可以使用 Ansys HFSS 中的全波时域或频域有限元求解器来模拟雷击对电子设备的影响。此示例使用频域 FEM 求解器与时域 Ansys 电路求解器相结合。可以使用相同的方法根据 IEC61000-4-2 等标准模拟静电放电 (ESD) 事件对电子设备的影响。

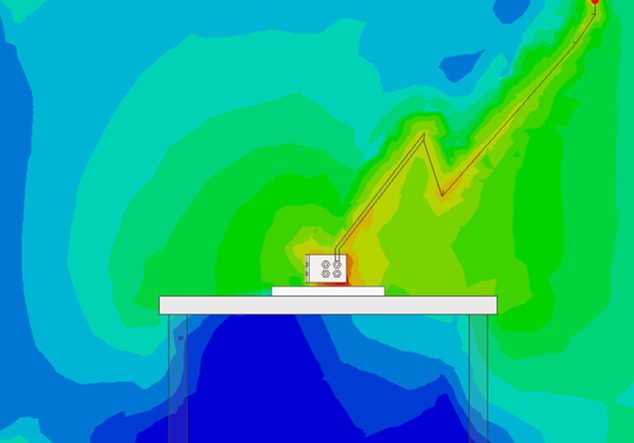

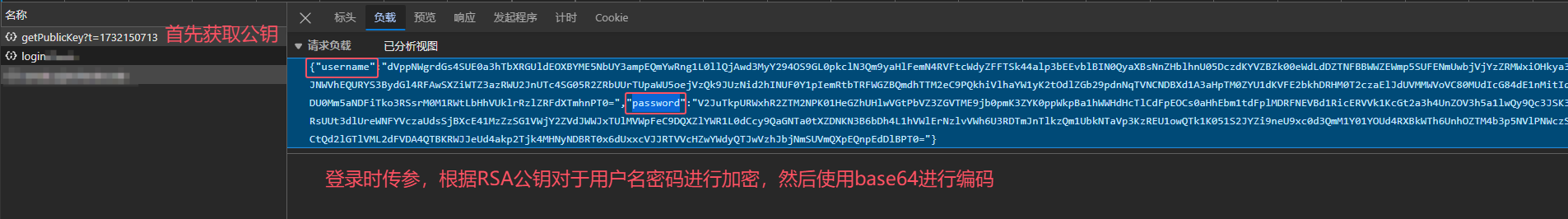

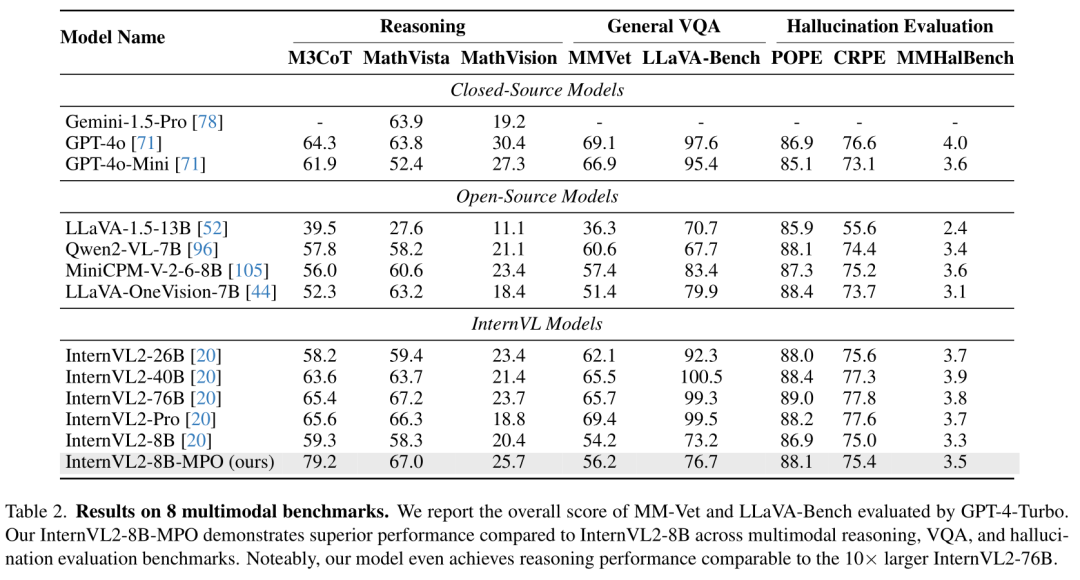

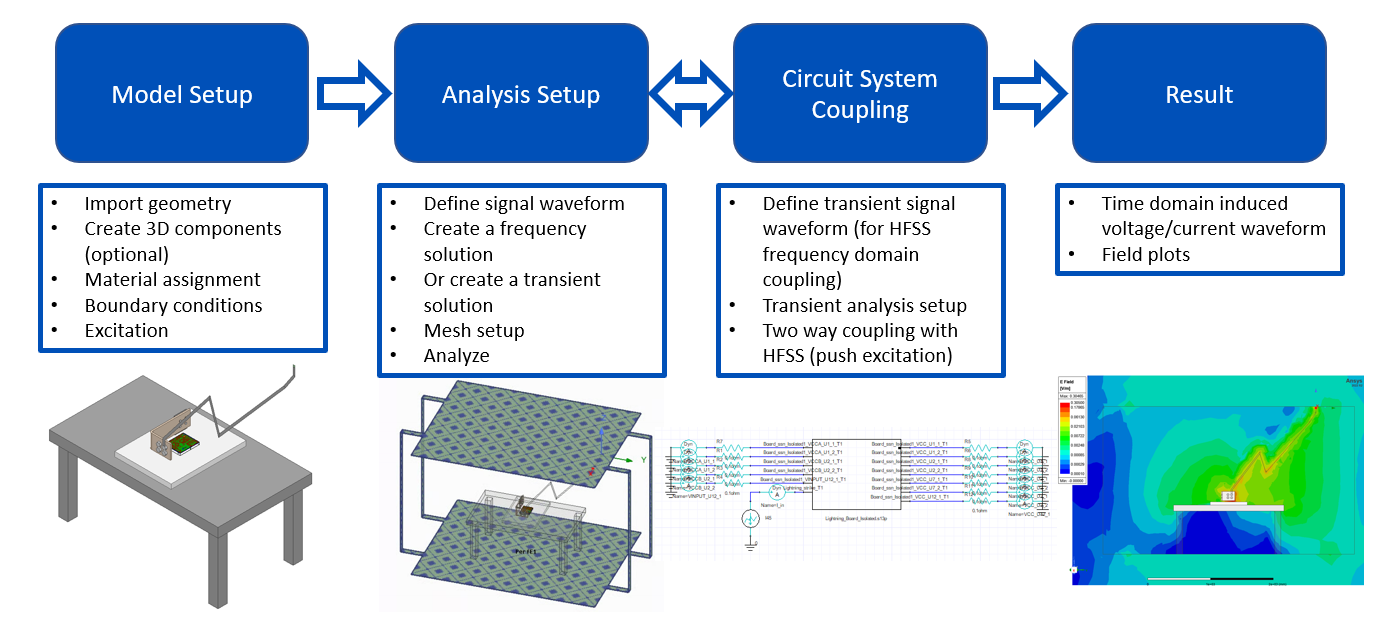

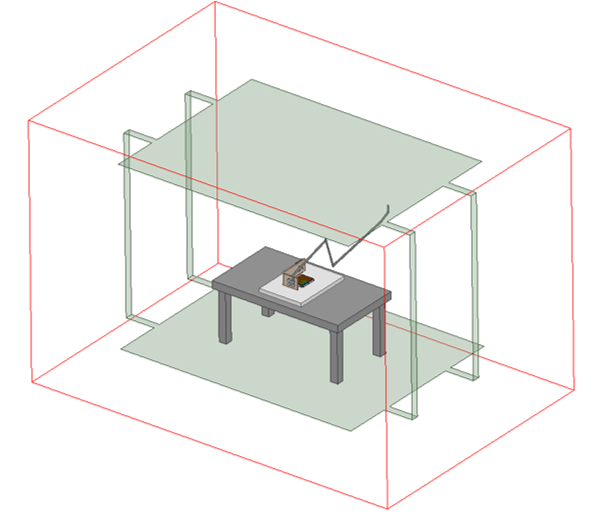

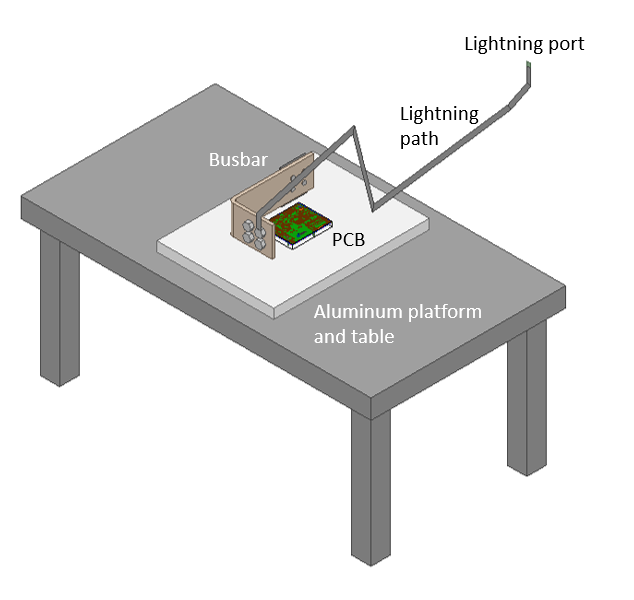

下面显示了模拟在铜母线附近被雷击的 PCB 中感应电流的仿真工作流程。HFSS 模型包括多层 PCB、铜母线结构和铝制平台和工作台。可以分配变量以自动研究感兴趣的参数,例如 PCB 和母线之间的间隔距离。将材料属性、边界条件和激励分配给模型。使用高达 50 MHz 的频率扫描求解 HFSS 模型,并将其动态链接到同样位于 Ansys Electronics Desktop 环境中的电路原理图。动态链接提供来自 HFSS 解决方案的 S 参数,用于电路模型。峰值幅度为 50 kA 的雷电波形用作电路电流源激励。可以从电路仿真结果中获得 PCB 导体上感应的电流和电压,双向动态链接可以在 HFSS 模型中检查电磁场。

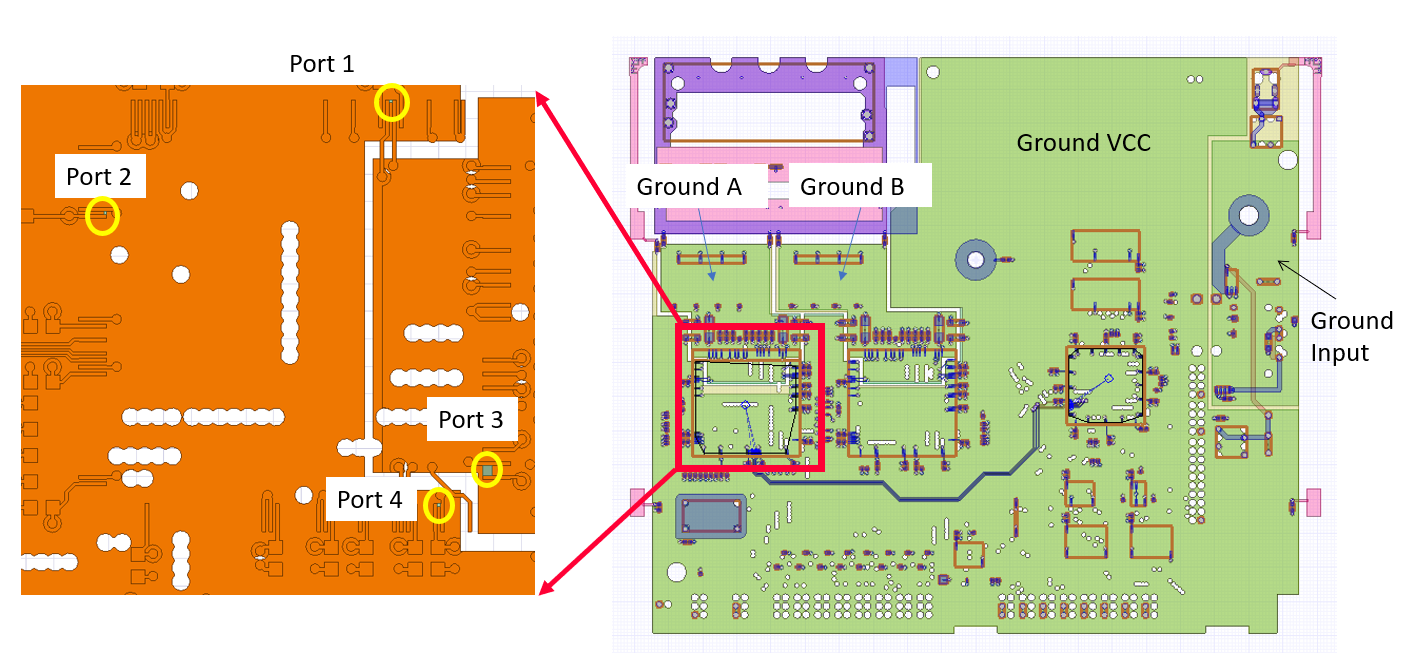

分配矩形集总端口来模拟雷电激励,并分配到需要确定雷击感应效应的 PCB 位置。吸收辐射边界被分配到周围空气区域的外表面。一对连接的导电板用作雷电返回路径,导电路径将上部雷电端口连接到母线结构上的雷击位置。

PCB 端口放置在多层 PCB 的较大导体上,这些导体预计会与附近雷击的能量有更高的耦合。在此示例中,这些导体是电源层,它们连接到可能受到损坏的敏感电子元件。HFSS 模型使用驱动终端解决方案类型。PCB 的尺寸约为 170 毫米 x 200 毫米,距离母线结构约 100 毫米。

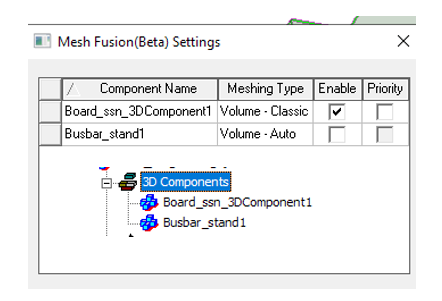

HFSS 模型中使用 3D 组件来重复使用现成的对象,例如 PCB、连接器或母线结构。这还允许使用网格融合,通过将最佳网格划分类型应用于每个 3D 组件,可以显著增加可用有限元方法求解的模型的大小。

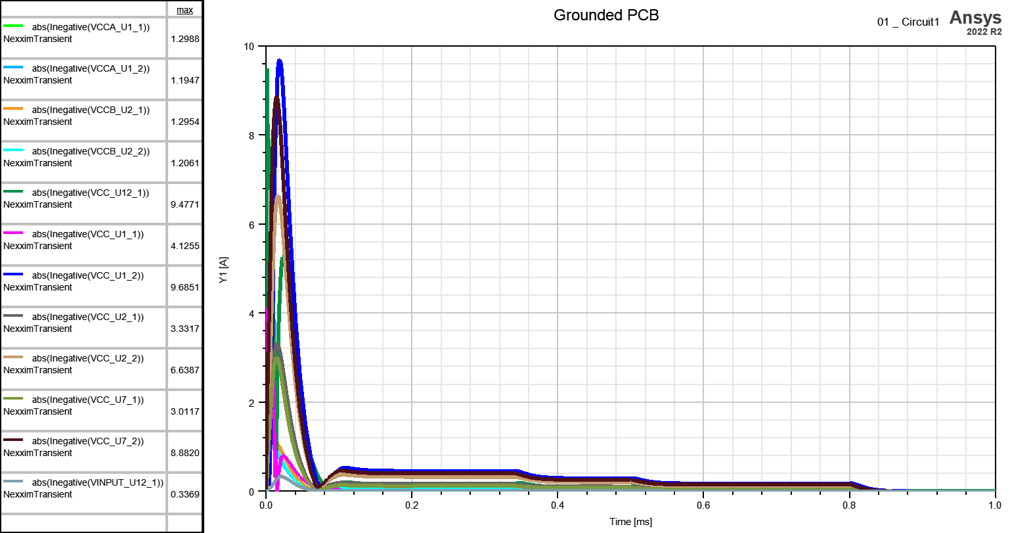

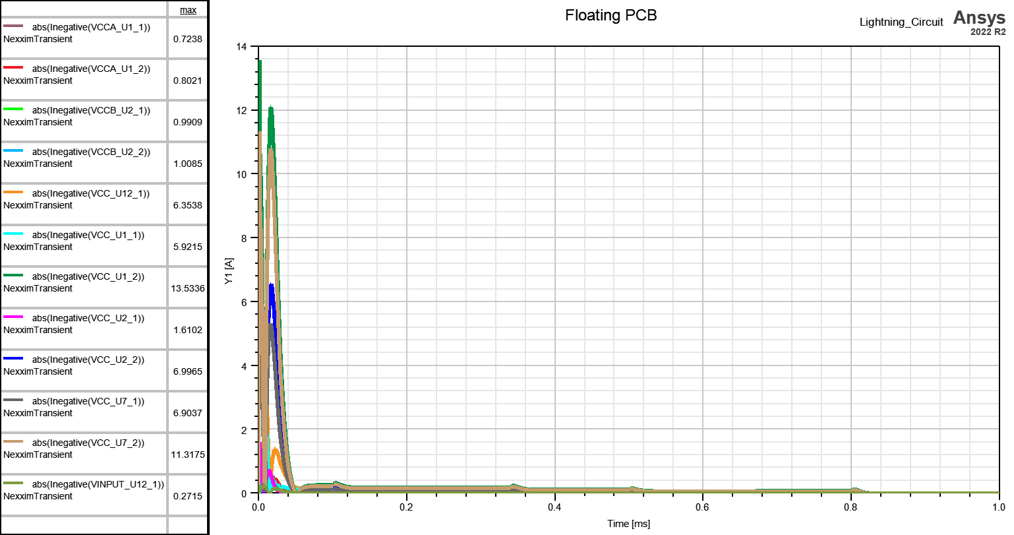

仿真结果可用于确定不同 PCB 接地连接对感应电流的影响,并优化敏感元件保护设计。在此示例中,在 PCB 导体中观察到高达 10 安培的瞬态电流幅度。HFSS 模型的更新可通过动态链接轻松传递到电路仿真,以确定对目标输出的影响。还可以检查电磁场,以了解如何减轻近场耦合到 PCB。