verilog编程规范

文章目录

- verilog编程规范

- 前言

- 一、代码划分

- 二、verilog编码

- A

- B

- C

- D

- E

- F

- G

前言

高内聚,低耦合,干净清爽的代码

一、代码划分

高内聚:

- 一个功能一个模块

- 干净的接口

- 提取公共的代码

低耦合:

- 模块之间低耦合尽量用少量的线连接

模块划分:关键路径逻辑和非关键路径逻辑放在不同的模块。方便对关键路径做速度优化,非关键路径做面积优化

二、verilog编码

A

- 设计文档和应用文档

- 一个模块一个文件,并命名相同

- 顶层模块只包模块之间的连线

B

- 避免门级电路,变得不可移植

- 避免三态门,而使用多路选择电路

- 避免latch

C

- 保证时钟和复位不出现gilch(竞争冒险产生的毛刺)。尽量使用同步复位

- 单个模块的reg使用同步复位

- 小心使用门控时钟(一般在低功耗设计中是用),门控时钟容易产生毛刺。如果要使用门控,尽量借助综合工具自动插入门控时钟。如果是手动,门控信号要从reg中给出,避免glitch

- 避免使用模块内部产生的使用,用PLL或者mmCM

- 一个模块中只使用一个时钟

- 避免多周期路径和假路径(多周期路径就是一个寄存器输出到另一个寄存器输入的路径不能再一个时钟周期完成)

- 要写可测试性设计(DFT):写功能时,就要考虑ATPG和BIST,要添加各种测试逻辑和bypass逻辑

- 一个模块中只用一个时钟沿。如果需要两个,则分开模块或者,将该时钟进行取反后输入(取反后的使用IBUFG)

- 跨时钟处理:要同步的信号从reg中出来。要同步的信号至少锁存两个clk。对cnt同步要用格雷码

关于跨时钟处理,有以下代码可以比较:

100MHz时钟域下有一个单周期的脉冲,如何将其转换到80MHz时钟域下的单周期脉冲。

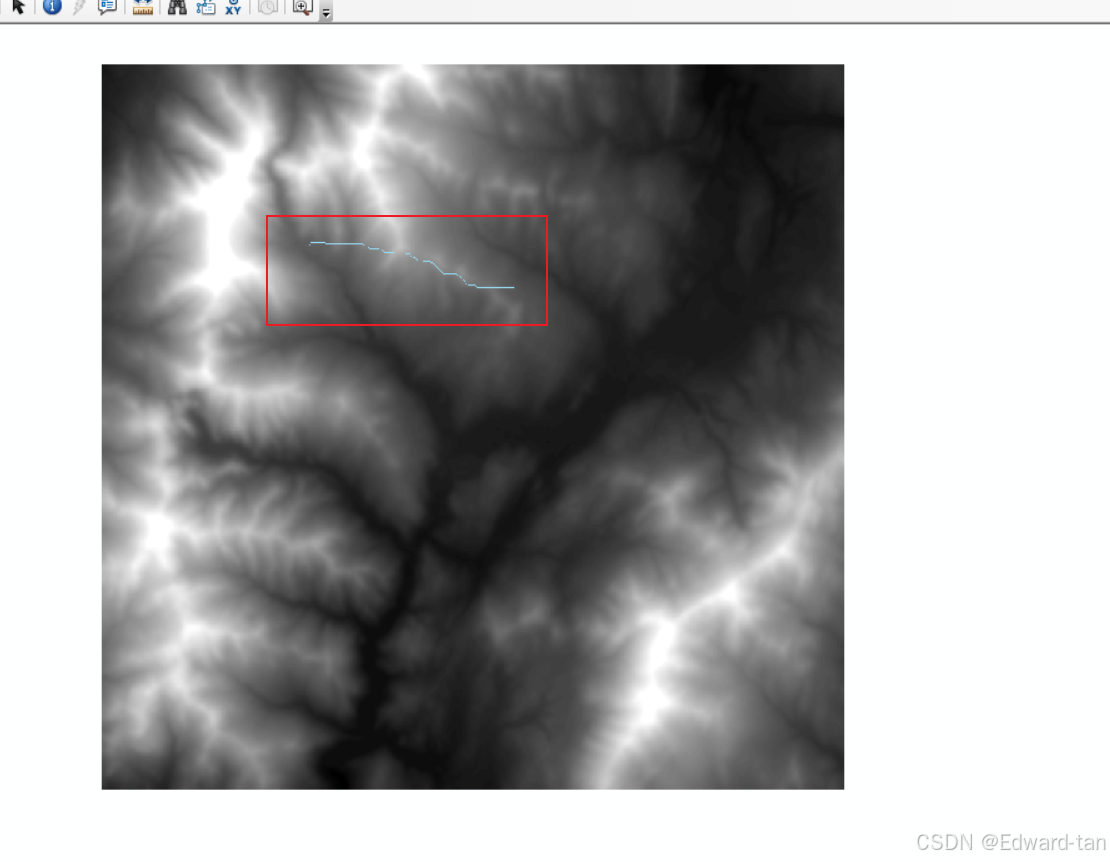

使用电平同步,将100MHZ的信号扩展,然后使用边沿检测。但是下面代码存在问题。

module test( input

i_clk1, //100MHz

input i_clk2, //80MHz

input i_pulse,

output o_new_pulse);

reg r1_pulse;

reg r2_pulse;

wire w_pulse;

always @(posedge i_clk1) //100Mbegin r1_pulse <= i_pulse ; r2_pulse <= r1_pulse;

end

assign w_pulse = r1_pulse | r2_pulse;

reg r1_new_pulse;

reg r2_new_pulse;

reg r3_new_pulse;

wire w_new_pulse;

always @(posedge i_clk2) //80Mbegin

r1_new_pulse <= w_pulse;

r2_new_pulse <= r1_new_pulse;

r3_new_pulse <= r2_new_pulse;

end

assign o_new_pulse = ~r3_new_pulse & r2_new_pulse;

endmodule

问题代码在这里:assign w_pulse = r1_pulse | r2_pulse;

两个寄存器之间是有延迟的,通过把脉冲变成电平信号,如果出现上图的情况,会导致电平信号又断点。在80MHZ的时钟周期的采样,可能或漏。处理方式如下面说的“要同步的信号从reg中出来”。即先在当前时钟域下先展宽之后,在从reg中输出出来给别人用,这样就避免使用组合逻辑了。

因此代码修改如下

always @(posedge i_clk1) //100Mbegin r1_pulse <= i_pulse ; r2_pulse <= r1_pulse; w_pulse <= r1_pulse | r2_pulse;end

reg r1_new_pulse;

reg r2_new_pulse;

reg r3_new_pulse;

wire w_new_pulse;

always @(posedge i_clk2) //80Mbegin

r1_new_pulse <= w_pulse;

r2_new_pulse <= r1_new_pulse;

r3_new_pulse <= r2_new_pulse;end

小结:

会议竞争和冒险的原理,可以发现,assign B = a & b; 这如果a和b因为布线延迟的原因,那么该组合逻辑就可能产生毛刺。在写组合逻辑的时候,也尽量去考虑布线的延迟问题,是否产生的毛刺会给设计带来影响。

参阅文章 竞争和冒险

D

- 用always@(*)

- 注意阻塞赋值和非阻塞赋值的场合:1.不要混用。2.组合逻辑always@()用=;锁存逻辑always@()用<=.3.时钟逻辑用<=

- 使用三段式状态机,且组合逻辑的转态跳转要用default

- case比if的时序好,case无优先级。if有优先级。

- if语句书写:嵌套要用begin

if(a == 1) beginif(c == 1)...else...end

else...

E

- 模块的输入先reg再使用。模块的输出先reg再输出。使得输入的时序,输出强度和延迟好预测。这样可以获得更好的时序

如代码:

module ins(input i_clk,input i_rst,input i_data,output o_vld

);

reg ri_data;

reg ro_vld;assign o_vld = ro_vld;always@(posedge i_clk)ri_data <= i_data;always@(posedge i_clk)ro_vld<= 1'b1;

endmodule

- 不要驱动input

- 保证所有output被驱动,如果没有使用则用assign 输出为0或者1

- 要声明所有信号,反之会被综合为1bit

- reg只能在一个always中赋值

- 在写验证代码时,不要用内部信号,用点操作符有时候会有问题,因为内部信号在综合为网表之后就不见了,在使用ila抓数时,使用点操作符去索引内部信号,可能会报错(综合时被优化掉了名字)。

- 设计代码时,不要使用force release initial forever === !===等

F

- 不要在include中写目录名字,写工层的相对路径,否则移植很麻烦

- 使用vh头文件

G

使用简洁的代码书写

c[3:0] = b[3:0] & d[3:0];

改写为

c=b&d;

// 没必要不用begin end

always@(posedge i_cllk)if(a == 1'b1) ro_data <= 1'b1;else ro_data <= 1'b0;- 模块端口按照功能划分

- 如果用 i_

- 输出用 o_

- inout用io_

- wire用w_

- reg用r_

- 打拍用r_data_d1

- 关于注释:注释的核心就是把代码删除了,看注释还能明白其功能。1.模块开头的注释,实现功能和关键特性。2.代码中的注释简明扼要。3.删除陈旧的代码和注释

- 使用参数化parameter