Chapter 19 Layout and Packaging

这一章我们介绍版图和封装, 关注模拟和数字电路的要求. 首先讲模拟电路中layout设计考虑, 然后解决衬底coupling问题, 最后描述封装问题, 分析IC的外部电容和电感问题.

19.1 General Layout Considerations

19.1.1 Design Rules

Minimum Width 最小线宽, poly和金属都有最小线宽限制

Minimum Spacing 最小间距限制

Minimum Enclosure 最小包裹限制. 例如poly和金属包裹contact

Minimum Extension 最小延申距离

19.1.2 Antenna Effect 天线效应

如果连到Gate的M1面积过大, 在刻蚀时M1会收集离子并增加电位, 导致栅氧击穿. 此为"天线效应". 为了避免此现象, 需要限制M1的总面积, 或者把M1打断, 通过M2连接.

19.2 Analog Layout Techniques

19.2.1 Multifinger Transistors

为了减小S/D节面积和MOS gate电阻, 宽W的管子需要折叠起来. 如下图所示. 每一个finger的宽度需要小于该finger的1/gm.

通过折叠finger能减小gate resistance, 但会增加gate capacitance.

对于cascode管, 最好取上下管的Width一样. 这样好画.

19.2.2 Symmetry 对称性

在Chapter 14中介绍非对称给全差分电路带来 input-referred offsets, 影响输入信号. 对称性能抑制共模噪声和偶数次非线性, 因此模拟版图中对称性很重要.

注意在S/D离子注入时, 会倾斜7°, 导致S/D一端被gate挡住, 造成Asymmetry. 可以通过添加dummy来使S/D的周围环境保持一致.

提高对称性, 有时候需要采用中心对称布局, 即版图上下左右都对称, 但会造成布线的复杂和困难.

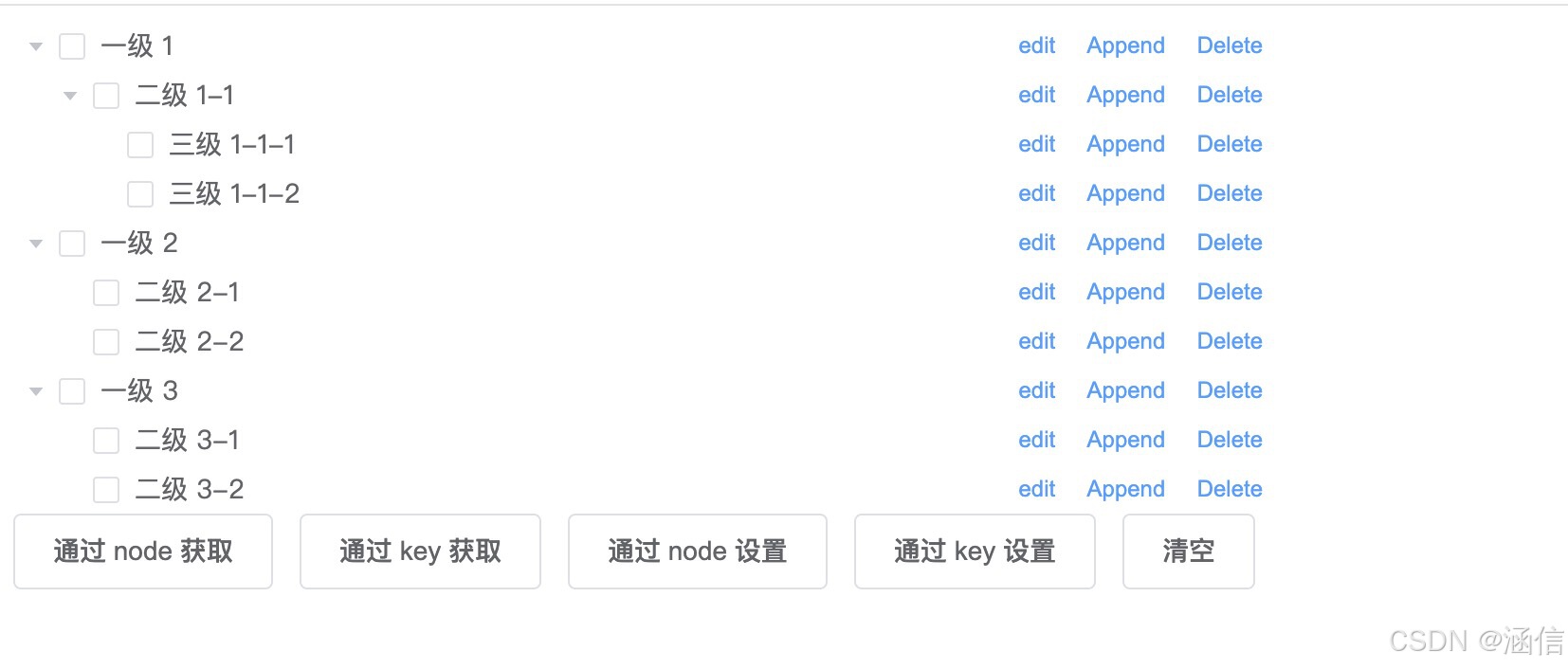

或者采用一维的交叉匹配. 如下图所示, 1221 (a)或者1212 (b). (a)略好于(b). 但是必须在1,4旁边加入dummy

19.2.3 Shallow Trench Isolation Issues

MOS管周围会挖浅沟渠(shallow trench)来阻断和其他MOS形成沟道. 为了解决应力不均问题, 需要在周边加dummy.

19.2.4 Well Proximity Effects N阱临近效应

在N阱注入时, 离子注入不是垂直90°, 而是偏移7°, 因此在N阱边上的注入浓度和N阱中间的注入浓度不同. 如下图所示, M1的Vth和M2,M3不同, 造成电流镜的不匹配.

为了解决WPE效应, 需要确保敏感管子(例如电流镜)的有源区(Active Area)到最远处的N-well的距离一致, 或者和Nwell的距离拉开(10um以上WPE效应就很小了).

19.2.5 Reference Distribution

对于电流镜基准的分布, Fig 19.23由于走线的电阻, 会造成M1, M2… Mn的Vs不同, 造成电流不同. 解决办法用Fig 19.24 送电流到哥哥模块, 在各电路内部复制电流. 但需要注意M1, M2… Mn之间的匹配. 例如朝向要同一个方向.

19.2.6 Passive Devices

Resistors:

polysilicon 电阻通过contact 金半接触, 用多晶硅做电阻, 有更好的线性性, 到sub小电容, 和小的mismatch.

金半接触需要打至少两个contact空来减少via阻抗, 可用蛇形分段走线来增加电阻值.

polysilicon的sheet resistance, 其值随process变化会达到±20%, 温漂变化+/-0.1%/◦C

用nwell或者S/D有源区做电阻, process偏差会变大. nwell的sheet resistance 在1kohm左右, 但是工艺偏差达到±40%. 另外其电阻受电压影响较大. TC 在+0.2% ~ +0.5% /◦C.

p+, n+ S/D有源区做电阻, sheet resistance在 20 ~ 30 ohm, silicided S/D region 适合小电阻应用. 但其电阻值也受到电压影响, 而且和衬底couple电容较大.

Silicided (掺入金属) polysilicon 电阻值 在sheet resistance在 20 ~ 30 ohm, 适合小电阻应用, 其衬底couple电容值较小. TC: +0.2 ~ +0.4%/◦C.

Capacitors

线性电容可用多层金属做成三明治形夹层. 需要注意两点: 电容的面积, 底层寄生电容和互连电容的比值 Cp/C.

下图(d)用了9层金属+poly, C1-C2之间的容值达到35 ~ 40 aF/μm2, M1-poly容值达到60 aF/μm2, 其值是(a)的9倍. 但是(d)的Cp/C的比例达到20.

需要注意Fringe Capacitance. 另外MOS也可以做电容, 将d,s,b短接到一起做一端, gate做另外一端. 注意MOS电容值会随着电压变化. 如Chapter 18所示.

对于高精度电路, 电容也需要做好匹配, 类似电阻一样做成矩阵.

Diodes

CMOS工艺中二极管需要做到N-well中, 但需要注意PNP的导通, 务必确保Nwell的电位不能低于p-sub, 否则会从p+上抽取电流.

19.2.7 Interconnects 互连

layout中金属层数多, 要注意排查线与线之间的coupling 电容. 尤其是注意时钟信号对敏感信号的couple. CLK到VIN的电容为50aF, VIn到GND右10fF, 那么CLK 5V跳变导致VIN变化25mV.

解决办法: 1, 输入信号采用差分形式, 抑制共模噪声. 2, 敏感信号做shielding, 即用线(通常是地)包住敏感线

Resistance 金属线sheet电阻为40 to 80 m/Ω, 80nm-80nm的metal contact-silicided polysilicon为 30-40Ω, M1到M2的via为 5-10Ω.

这些金属走线电阻会引入热噪声.

走线延迟可初略估算为

T D = 1 2 R u C u L 2 T_D=\frac{1}{2}R_uC_uL^{2} TD=21RuCuL2

Ru和Cu为单位电阻和电容值

另外需要注意走线的电流, 1, 大电流产生IR drop, 造成sense点电压偏低. 2, 注意electromigration(EM), 即金属走线电流能力. 一般来说, 对于M1-M3底层金属, 110C下电流能力为1um走1mA, 对于Top metal™电流能力要大一些, 达到1um走1.6mA.

19.2.8 Pads and ESD Protection

Bond Wire的大小为25um - 50um, Bond Pad的大小为70 μm × 70 μm 或者100 μm × 100 μm, 由top metal构成, 寄生电容大概40fF ~ 60fF. Pad走高频信号通常做成8边形, 来减小20%电容.

另外还需要注意的是electrostatic discharge(ESD)问题, 即静电把pin脚击穿.

ESD的基本原理是用R1, D1, D2确保circuit看到的信号不超过VDD. 常用ESD期间可以GGNMOS, 即gate, source, body接到一起. drain做抗pin的. ESD会带来额外的电容寄生(pF级别)

19.3 Substrate Coupling

CMOS工艺用P衬底, 其电阻值很小0.1Ω·cm, 会造成不同电路衬底串通, 或者衬底噪声严重干扰敏感信号. 例如在数模混合电路中, 数字Clock电路对模拟敏感电路的干扰.

为了解决这个问题, 1,模拟电路尽量采用差分结构, 来抑制共模噪声. 2,数字电路采用complementary结构, 减少coupled noise. 3, 关键操作例如采样需要等到clock完成, 等到PSUB稳定之后. 4, 尽量减少衬底SUB的bond wire.

在layout上, 可加入guard ring, 即把电路周围用Pwell和Nwell分别包一圈出来, 吸收隔离浅层的SUB噪声电流.

对于芯片整体, 可以把SUB和Ground通过一根线接到一起.

有AGND和DGND, SUB最好还是和AGND连到一起, 这样模拟电路性能更好一些.

19.4 Packaging

封装寄生包括 Bond wire自身电感, trace电感, trace到地的电容, trace之间的电容和电感. 封装并没有随着电路工艺提升那么快, 制约了电路的速度和性能.

对于典型的bond wire, 寄生参数约为 1nm/mm.

数字电源脏(纹波大), 模拟电源要求高, 因此会把模拟电源和数字电源分开.

如果特别在意电源纹波, 可以在电源VDD和GND之间加入大电容做couple.

为了降低bonding线的寄生, 可把芯片长在可导电的外延层上, 或者用WLCSP (Wager Level Chip Scale Package), 如下图所示. Pad通过RDL金属层连到Ball上, 中间有绝缘层和die的passivation(钝化层)

Mutual Inductance

为了减小bonding线之间的寄生电感, 可用干净线把敏感线隔开, 或者让电流相反的线并排, 这样能减小电感.