上一节给大家介绍了PXI的背景和历史,让我们对PXI的起源有了更多的认识。同时对PXI机箱做了初步介绍。本节将会从10个方面为大家详细解剖PXI机箱。

PXI槽位序号

每一个PXI槽位都有一个对应的槽位号(大部分情况下)被标注在PXI插槽下方。一般为从左到右排列。

图1.3-在每个槽位下方标有槽位号的小型PXI机箱(图片所示为Pickering公司的40-922-001)

6U机箱及3U模块叠加安装

某些6U机箱允许3U模块被“叠加”使用,使每个6U插槽可安装两个3U模块。通常允许部分特定的槽位支持此类叠加应用,如下图所示。

图1.4-支持3U叠加安装的6U机箱上的槽位编号

一个支持叠加的6U机箱中的各槽位在底部都具备P1和P2两个连接器以支持3U PXI模块,而双叠加槽位中P4和P5连接器将用于支持安装在在槽位上部的另一个3U PXI模块。顶部PXI的槽位号标示在槽位上方,而不支持叠加的槽位上方没有此类标记。

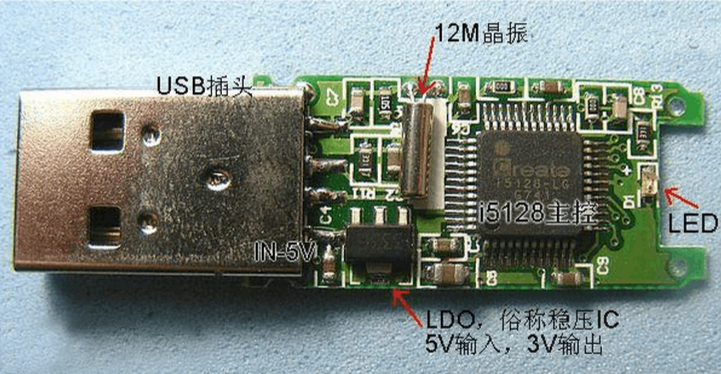

PXI背板

PXI背板通常是多层的单一PCB(通常是很厚的PCB,因为层数很多并且包含专门的电源层用于电源分配),PXI模块可以插在其上,背板将所有的控制信号与电源传送到模块。

图1.5-19槽机箱中的背板(图片所示为Pickering公司的40-923A-001)

PXI总线与枚举

多数PXI系统通过33MHz 32位宽的总线连接模块,总线分段之间通过PCI桥连接。PCI桥对于用户的软件来说是透明的。

PCI总线通过被称为总线枚举的过程,以一种基于程序设定的识别算法来定位物理的PXI槽位。对于PCI来说有两个识别码:PCI总线分段号和段内设备号。PCI是共享总线的系统,系统内每个总线分段(在两个PCI桥之间)都有一个总线号,在每个分段内最多可以支持16个设备,并以设备号区分。在机箱中设备的物理位置是“硬连接”的。因此安装于机箱中特定插槽的外设模块都具有一个与之对应的特定的总线号和设备号。一个小小的难题是总线号是由枚举算法决定的,两个不同的控制器有可能会为同一个总线分段分配不同的总线号,例如一个控制器安装有PCI显示卡而另一个没有,则分配给PXI的总线号就可能不同,并且如果一个控制器添加了新的PCI设备也可能造成编号改变。对于控制器而言,内部的PCI总线首先得到编号,然后才是从控制器开始进行枚举。这个复杂的过程由VISA和其他软件工具来完成,对于用户来说是不可见的。

PCI可以支持的总线分段数量有明确的上限——256,PXI也同样如此。这对系统规模并不是一个严重的限制,因为在PXI系统中每个总线通常可支持最多7个设备。

PXI背板为PXI模块提供电源和PCI接口。背板需要同时包含为保持PCI总线完整而必须的PCI桥。此外背板还需支持其它PXI特性,如触发,本地总线和星形触发,这些内容在本书其它部分加以介绍。

PXI机箱电源

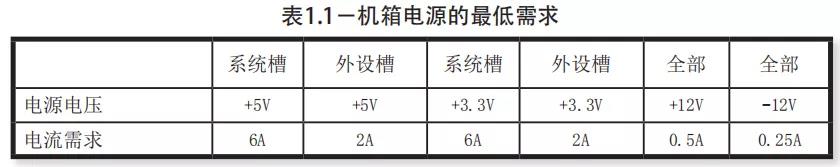

PXI标准规定了供应到每个模块的最低电源要求。以下为兼容2.1版PXI规范机箱的最低指标。

机箱电源必须能够为每个槽位提供电源且每个电源轨需供应足以支持所有槽位全部占用的情况。上表显示了通常机箱需提供的最低电流,这并非对单个模块的耗电限制——对这一指标另有规定。

机箱的电源和背板必须能够为每个外设槽位的+12V和-12V供应至少1A电流,而每个槽位的+5V需供应至少6A。如果机箱是遵照2.1版本之前的标准制造的,无需符合以上要求。

如果机箱中安装了多个高耗电的模块,有可能超过电源的容量,这种情况并不多见,因为在大多数测试系统中大部分模块的电源需求远低于平均值。

背板连接器上的每个针最大可通过1A电流。每个连接器为了承载额定电流需要使用多个针。按照上面的表格,每个+5V和+3.3V电源需要6根针。很多机箱可以为每个电压提供更高的电流。此信息需要在机箱使用手册中注明。

系统参考时钟

PXI背板提供了一个10MHz并达到100ppm或者更高精确度的系统参考时钟。此时钟规定为具有50%±5%占空比,并对每个模块都单独传送以避免模块之间相互干扰。保证每个槽位接收到的参考时钟信号同步,误差不超过1ns。

对于有些应用,系统参考时钟还不够精确或者不够稳定,尤其是对于规定射频载波频率准确度的射频应用。星形触发插槽具有专用引脚用于提供替代的参考时钟。PXI规范建议,背板提供在参考时钟与星形触发槽位(2槽)提供的替代频率源间切换的功能。

本地总线

本地总线是一组在相邻的PXI槽位间以菊花链形式连接的13条导线。本地总线中的每条线从槽位的右侧连接至相邻槽位的左侧。总线用于使两个相邻的模块间直接传送模拟信号(最高±42V)或数字信号。软件需要在模块使用此功能前检查相邻模块之间的相容性。如果模块使用了本地总线但没有安装在正确的位置,那么本地总线会失效,因为规范并没有要求模块提供本地总线桥接功能。不同的模块可能以不同的方式使用本地总线(或完全不用)。

位于控制器旁边的插槽(2槽星形触发)是例外情况。左侧的本地总线连线(面对控制器)用于星形触发功能,不与系统控制器连接。本地总线的带宽与其它特性并未在标准中规定,完全取决于产品设计者如何使用这些连接。

(PCI 仲裁与时钟信号)图1.6-PXI本地总线线路

触发总线

8个PXI触发线提供了一个同步操作PXI模块的方法。该总线可配置,因此在系统中任何模块都能向另一个模块发送触发信号,并且可以响应其它模块的触发。标准没有对缓冲区或支持工具做出具体规定。触发总线不允许在机箱中没有附加缓冲系统对段间电气隔离的情况下穿越PCI桥。

触发总线的长度也被限制为252mm。由于标准没有规定缓冲和相关的支持工具,因此这些功能可能并未包含在机箱中或仅通过跳线手动实现。因此建议将需要使用触发总线的模块置于同一个触发总线段中。机箱前部的PCI分段标示符明确标注了PCI桥的位置。

8个PXI触发线可以提供一种低延迟的事件触发方法——触发线可以直接连接到硬件。但在多数PXI产品中,触发操作会通过驱动程序处理(在IVI中则全部需经过驱动程序)所以实际的操作速度受制于软件延迟。

星形触发

星形触发是一种高性能的触发系统,设计用于从第一个外设槽位(2槽)向其它外设槽位之间引出高速触发线。这些外设槽位中的模块只有支持星形触发线才能实现以下所述的特性。星形触发占用的是2槽左侧通常用做本地总线的线路。星形触发插槽并不是一个机箱的必备组件,但是在实际中,大多数机箱都提供此槽位。如果不需要使用星形触发功能,该槽位可以用作一个普通的外设槽位。

星形触发的背板和模块均标记有星形触发槽位符号。

图1.7-星形触发槽位符号

将星形触发控制器安装在机箱中,通过星形触发可以确保对外设模块同步进行事件触发,且模块间的触发时间差极小,触发器系统是双向的,因此星形触发允许通过一个外设模块中的事件触发另一个模块中的事件。

星形触发控制器提供13根输出线,每一根都连接到特定的外设模块。在14槽机箱中通常包含12个外设插槽(14个槽位减去1槽和2槽)和1个PCI桥(指33MHz的PCI总线)。此13根星形触发输出线连接到12个外设插槽。对于更大的机箱,较高序号的槽位(超过15号)不支持星形触发,这些槽位中应安装不需要此功能的模块。

对于需要使用超过一个机箱的系统,可以将星形触发模块安装在每个机箱中,并将它们连接在一起。连接方法可以通过线缆,或者通过GPS时钟来同步,以使PXI测量仪器系统以分布式的形式实现更复杂的测量。

与8个PXI触发线类似,星形触发的操作可能需通过驱动程序来执行,在这种情况下,同步度可能要取决于软件的延迟时。

图1.8-包含两个总线段的PXI系统结构

PXI模块

PXI标准同时定义了3U和6U模块适用的机械尺寸与连接器形式。

3U模块在模块底部安装有一个助拔手柄。在顶部和底部通过螺钉固定,底部的固定螺钉部分隐藏在助拔手柄中。占用超过一个槽位的模块可以使用超过两个螺钉来固定。可以安装两个连接器(J1,J2),但是如果模块不需要J2连接器的功能(64位PCI和PXI特性),为了降低成本可以不安装此连接器。

6U模块安装有两个助拔手柄和两个连接器(J1,J2)。安装任何其它连接器(定义为J3,J4,J5)都不在规范之内并且可能产生机械和电气的兼容性问题。用于固定的螺钉安装在模块的顶部和底部且部分隐藏在助拔手柄中。占用超过一个槽位的模块可以使用超过两个螺钉来固定。

应该保持所有的锁紧装置均调整牢靠,尤其对于需要良好接地的模块来说非常重要。前面板地必须与PXI电源地相隔离以避免产生地环路电流。对所有模块的性能描述均指所有螺钉已锁紧的条件下。

近年来PXI的发展进入了一个新阶段,前面板空间不足的问题愈发显现,当前有一种趋势是取消模块的助拔手柄。

图1.9-PXI外设模块的封装形式和连接器

除了具有特定仪器功能的PXI模块,制造商也提供PXI原型模块,这种模块提供一个PXI接口,一些控制线以及其它一些实用功能。这些模块使得用户可以设计实现具有独特功能的模块而无需投入过多资源用于PXI基本功能的研发。当硬件完成后就可以创建专用的驱动程序再集成到PXI系统之中。

图1.10-典型的原型模块(图片所示为Pickering公司的面包板模块40-220)

PXI-1槽,系统插槽

机箱最左侧的槽位预留为系统控制器专用。该槽位包含一组连接到背板的连接器,且名义上此处为1个槽位。然而在实际使用中,一个控制器可能需要占用多个槽位,因 此标准允许在机箱中将1槽的空间向左扩展(远离其它外围模块的方向)。典型的机箱可能包含三个控制器扩展槽位,与控制器槽一起共可为控制器提供4槽的空间,但是仅使用一组背板连接器。控制器扩展槽位没有背板连接器。

PXI机箱中可以在1槽位置安装嵌入式控制器,也可以安装接口模块连接外置控制器(例如一台电脑)。典型的接口模块基于专用的串行接口,以铜缆或光纤连接外部控制器和机箱中的模块。接口的运作方式类似于PCI到PCI桥,对系统软件透明。控制器中的PCI接口卡发送串行信号而机箱中的PXI接口卡解码数据并传送至PCI总线。例如,National Instruments的MXI-3采用专用1.5Gb/s串行连接作为互联接口,ADLINK采用4个基于开放标准的Star Fabric串行连接提供总带宽2.5Gb/s的连接来实现相同的功能。也可以使用外部PCIe系统。

相同接口的模块可以在系统中用于机箱扩展。在第一个机箱中任意外设槽位安装接口模块,通过串行接口连接到另一个机箱1槽中的接口模块。

到此PXI总线及PXI机箱内容暂时告一段落,下一章节将为大家介绍PXI Express总线的相关内容,敬请关注!

关于虹科测试测量

虹科是一家在测试测量行业经验超过10年的高科技公司,虹科与世界知名的测量行业巨头公司Marvin Test以及Pickering Interface合作多年,提供领域内顶尖水平的基于PXI/PXIe/PCI/LXI平台的多种功能模块,以及自动化测试软件平台和测试系统。事业部所有成员都受过国内外专业培训,并获得专业资格认证,所有工程师平均5年+技术经验和水平一致赢得客户极好口碑。我们积极参与行业协会的工作,为推广先进技术的普及做出了重要贡献。至今,虹科已经为全国用户提供了100+不同的解决方案和项目,并且获得了行业内用户极好口碑。