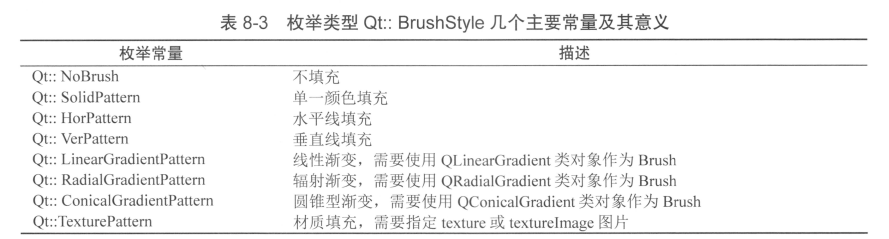

一.FIFO简介

FIFO (First In First Out,即先入先出),是一种数据缓冲器,用来实现数据先入先出的读写方式。

二,FIFO实现原理

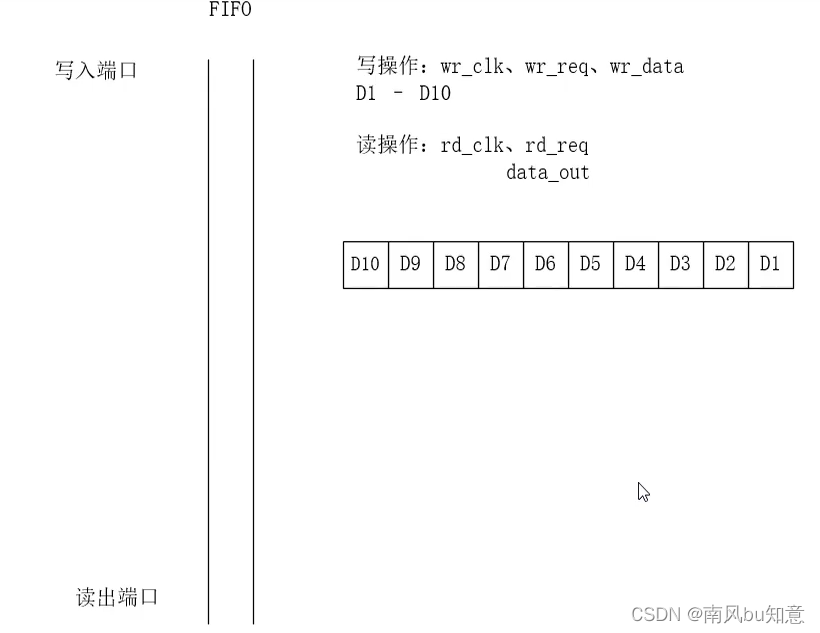

FIFO是采用一种先入先出的实现原理

就如图按照D1到D10的顺序输入那么读取的时候也是按照D1到D10的顺序读取.

三,FIFO应用场景

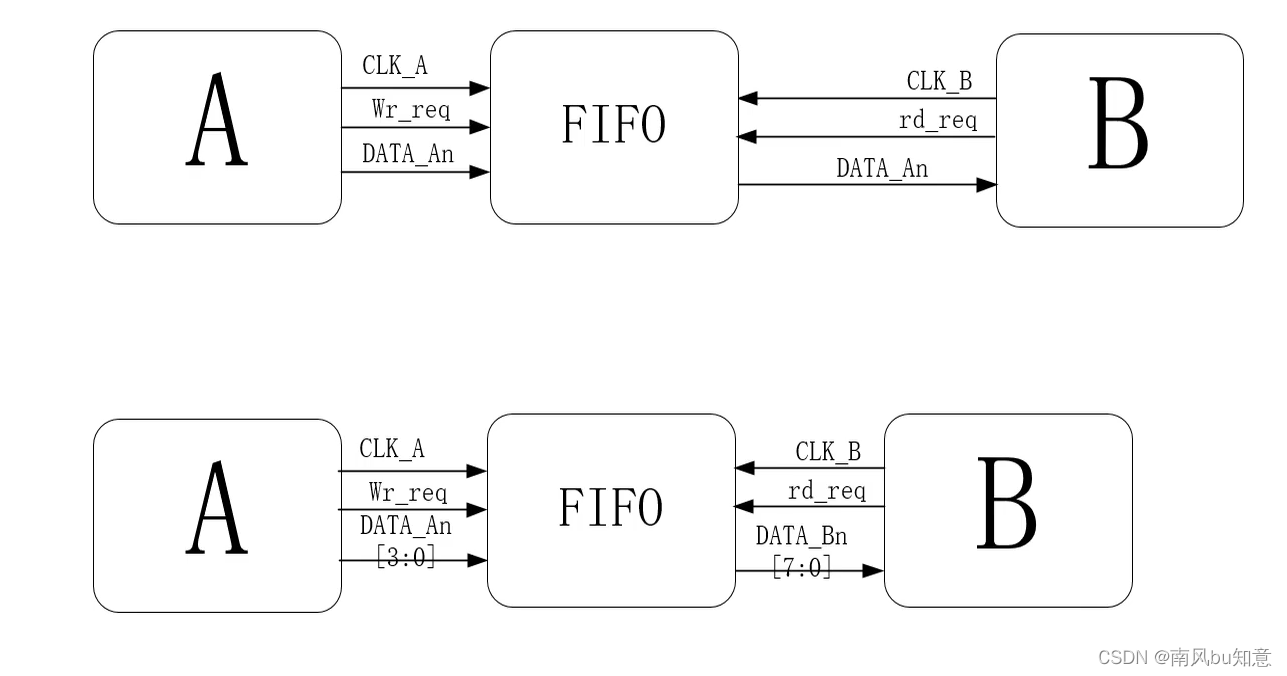

FIFO存储器主要是作为缓存,应用在同步时钟系统和异步时钟系统中,在很多的设计中都会使用;如:多比特数据做跨时钟域处理、前后带宽不同步等都用到了FIFO。

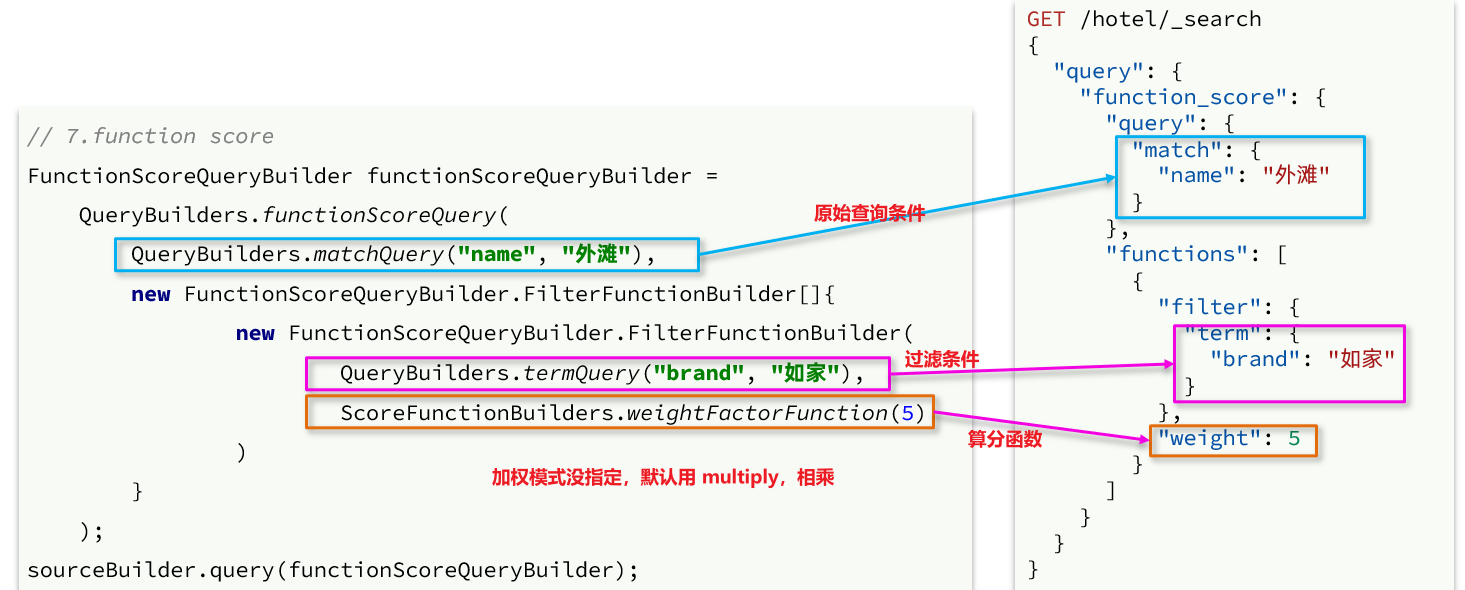

比如下边图1就是多比特数据做跨时钟域处理

图2为带宽不同的数据处理

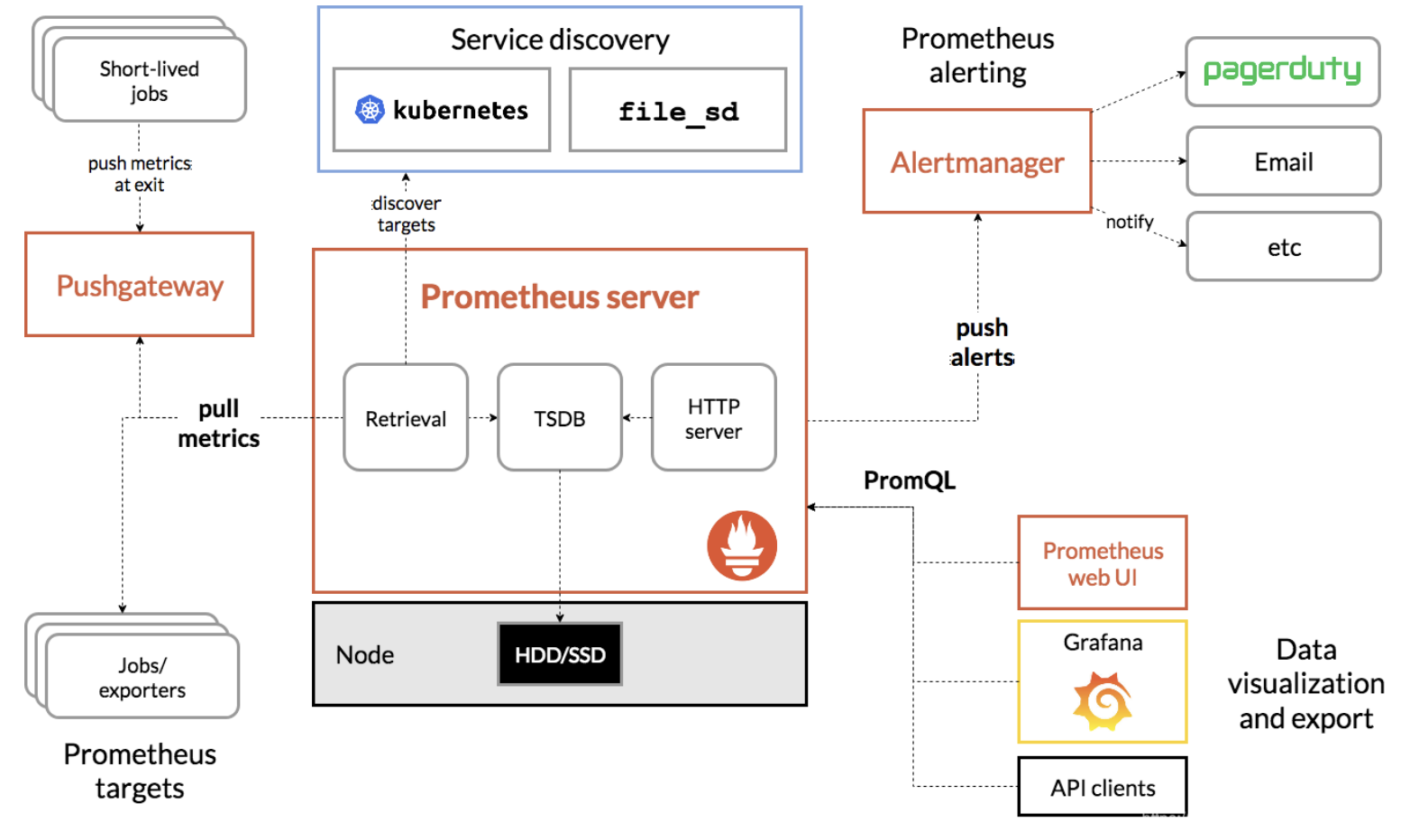

四,同步FIFO的配置与调用

- 首先在右侧搜索并选择FIFO

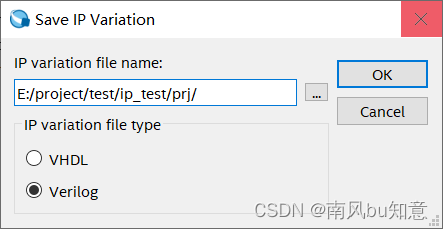

- 在弹出的界面选择保存路径和Verilog

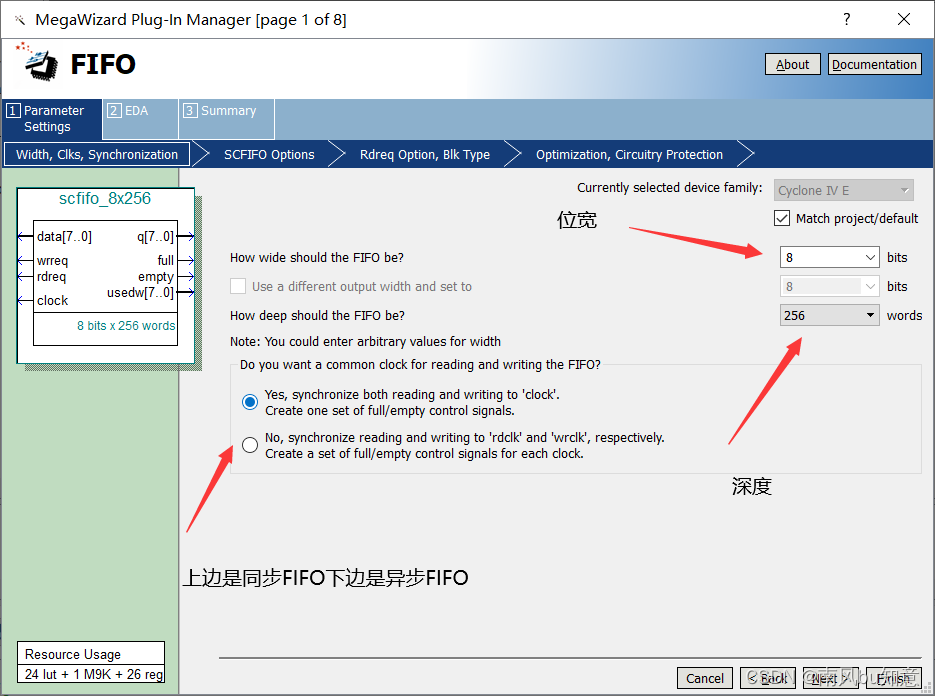

- 选择位宽和深度,并选择异步或同步FIFO

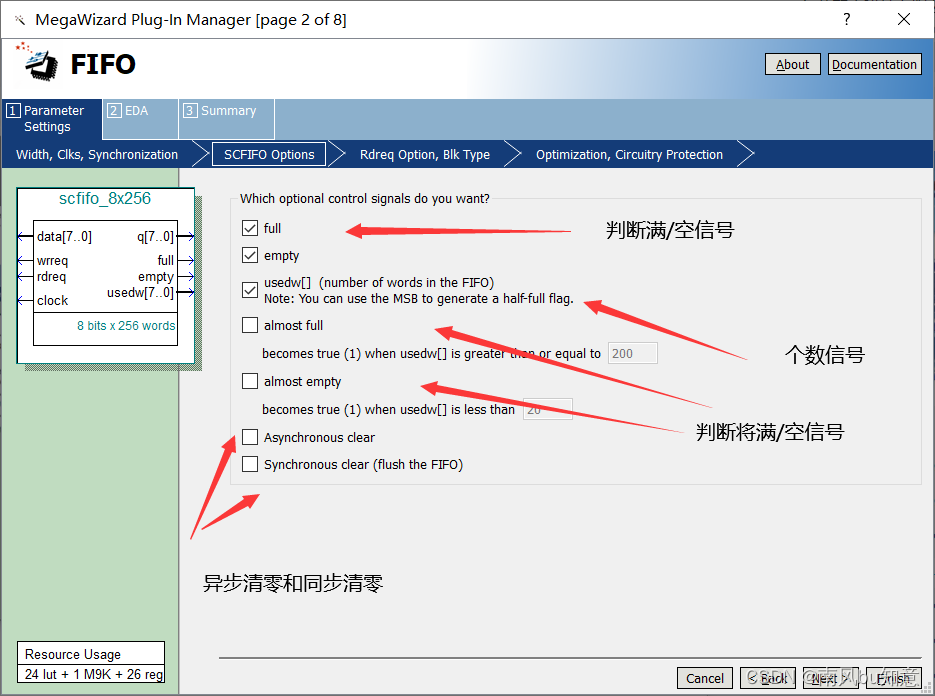

- FIFO中的输入输出管脚选择

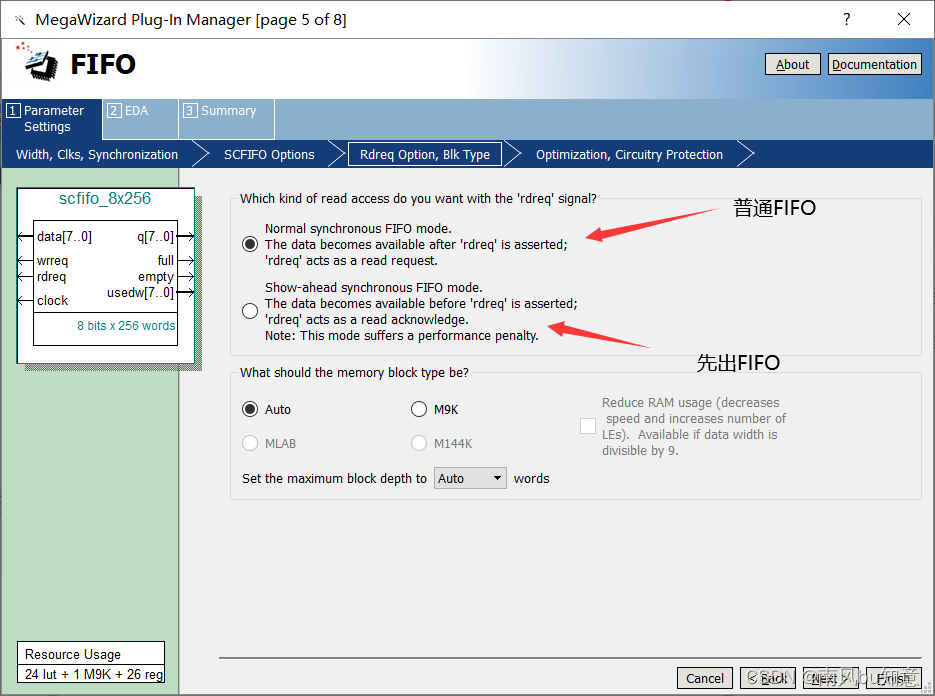

- 普通同步FIFO或先出数据FIFO模式

普通FIFO读取数据会比读取使能满一个周期

先出数据FIFO会和使能同步

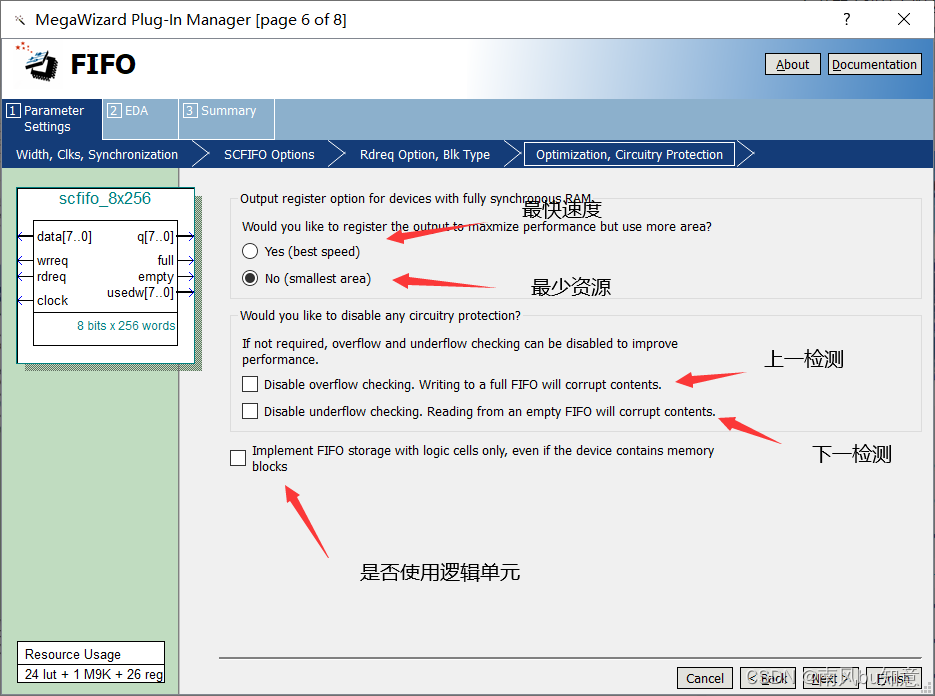

- 性能选择

上一检测:输入满后禁止输入

下一检测:读取空后禁止读取

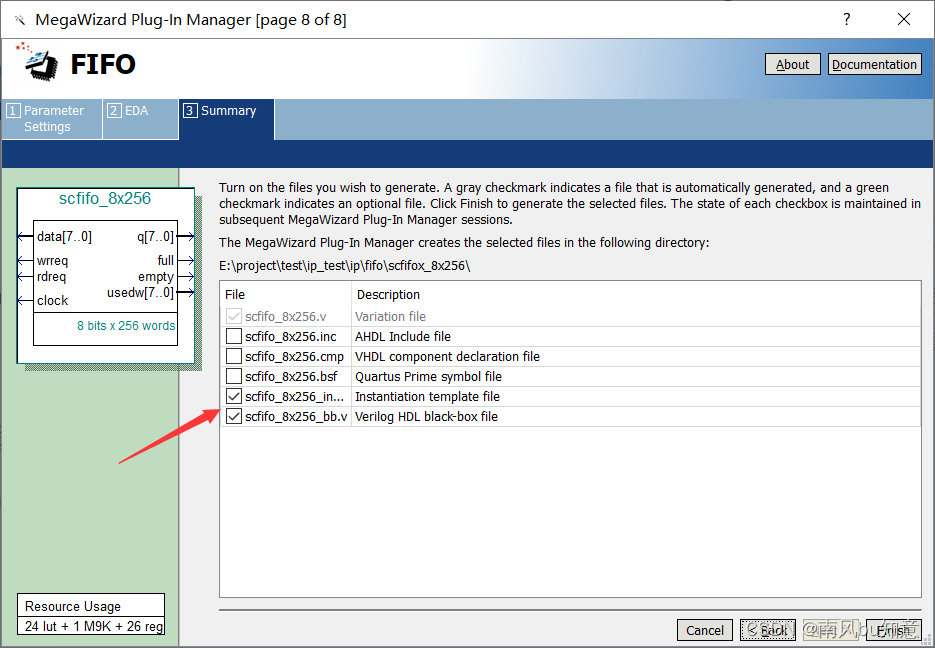

- 生成文件

默认勾选这两个

- 代码调用

/**************************************功能介绍***********************************

Date :

Author : WZY.

Version :

Description: fifo功能测试

*********************************************************************************///---------<模块及端口声名>------------------------------------------------------

module fifo( input wire clk ,input wire rst_n ,input wire [7:0] data ,input wire rd_req ,input wire wr_req ,output wire empty ,output wire full ,output wire [7:0] po_data ,output wire [7:0] usedw //数据个数

);

//---------<参数定义>--------------------------------------------------------- //---------<内部信号定义>-----------------------------------------------------scfifo_8x256 scfifo_8x256_inst (.clock ( clk ),.data ( data ),.rdreq ( rd_req ),.wrreq ( wr_req ),.empty ( empty ),.full ( full),.q ( po_data ),.usedw ( usedw )); endmodule

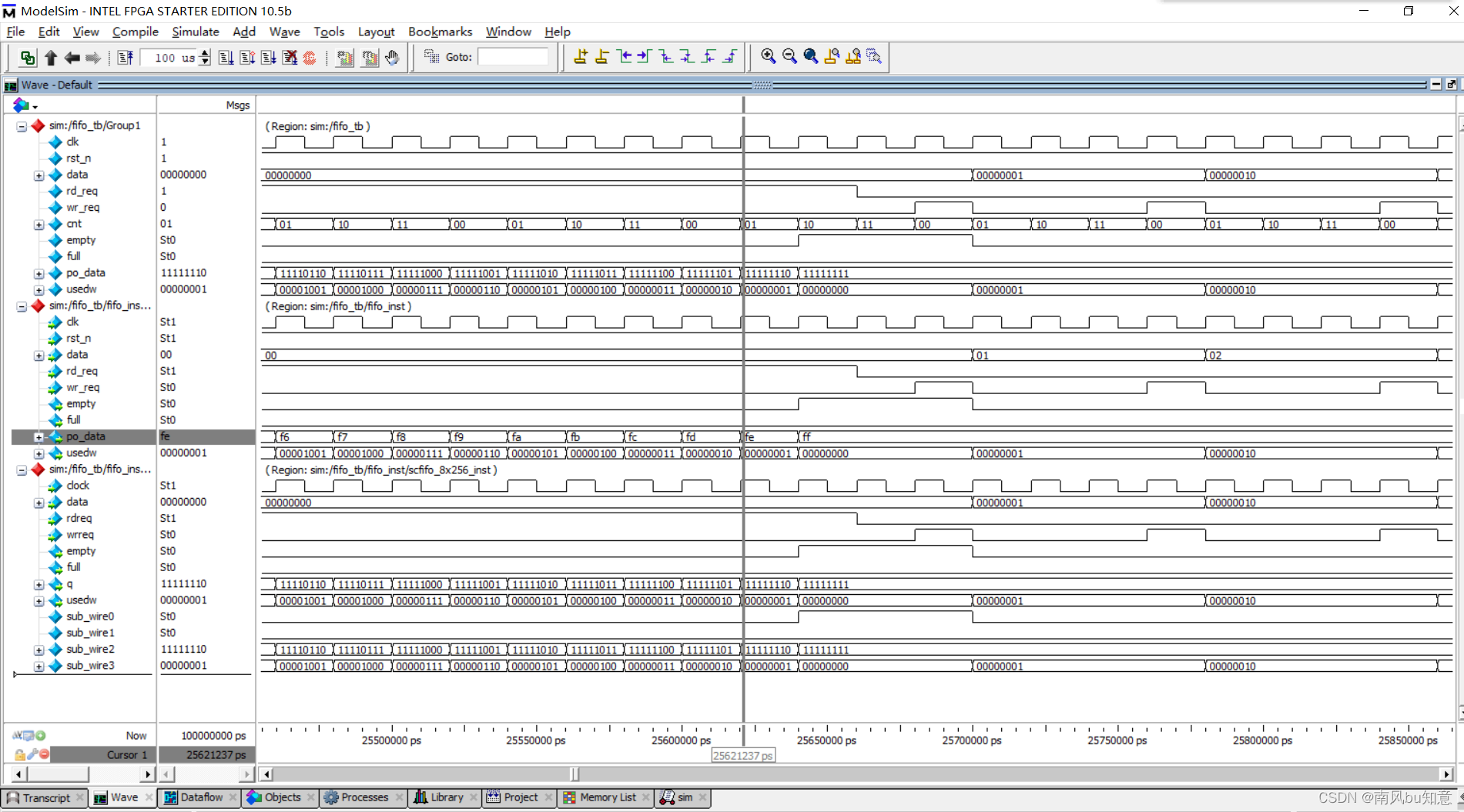

五.仿真观察

仿真代码

`timescale 1ns/1nsmodule fifo_tb ();

//产生激励

reg clk ;

reg rst_n ;

reg [7:0] data ;

reg rd_req ;

reg wr_req ;

//参数定义

parameter CYCLE = 20 ;

reg [1:0] cnt ;wire empty ;

wire full ;

wire [7:0] po_data ;

wire [7:0] usedw ;

//产生时钟

always #(CYCLE/2) clk = ~clk ;

//cnt

always @(posedge clk or negedge rst_n) beginif (!rst_n) begincnt <= 2'd0;endelse if (cnt == 2'd3) begincnt <= 2'd0;endelse begincnt <= cnt + 1'd1;end

end

//写使能

always @(posedge clk or negedge rst_n) beginif (!rst_n) beginwr_req <= 1'b0;endelse if (cnt == 2'd3&&rd_req == 1'b0) beginwr_req <= 1'd1;endelse beginwr_req <= 1'd0;end

end

//data

always @(posedge clk or negedge rst_n) beginif (!rst_n) begindata <= 8'd0;endelse if (data == 8'd255&&wr_req == 1'b1) begindata <= 8'd0;endelse if (wr_req == 1'b1) begindata <= data + 1'b1;end

end

//读使能

always @(posedge clk or negedge rst_n) beginif (!rst_n) beginrd_req <= 1'b0;endelse if (full == 1'b1) beginrd_req <= 1'b1;endelse if (empty == 1'b1) beginrd_req <= 1'b0;end

endfifo fifo_inst( .clk (clk),.rst_n (rst_n),.data (data),.rd_req (rd_req),.wr_req (wr_req), .empty (empty),.full (full),.po_data (po_data),.usedw (usedw)//数据个数

);initial beginclk = 1'b1;rst_n = 1'b0;#20rst_n = 1'b1;endendmodule

测试波形