0x00 回顾:AND/OR/NOT 逻辑的特性

AND:与门可以具有两个或更多的输入,并返回一个输出。当所有输入值都为 1 时,输出值为 1。如果输入值中有任何一个为 0,则输出值为 0。

OR:或门可以具有两个或更多的输入,并返回一个输出。如果输入值中至少有一个为 1,则输出值为 1。如果所有输入值都为 0,则输出值为 0。

NOT:非门具有一个输入和一个输出。当输入值为 1 时,输出值为 0;当输入值为0时,输出值为1。

晶体管级逻辑门 AND/OR/NOT 的结构:

0x01 扇出的概念(Fan-out)

扇出 (fan-out) 是一个定义单个逻辑门能够驱动的数字信号输入最大量的专业术语。

扇出即输出可从输出设备输入信号的电路的数量。它的英文含义是“分散”。扇出的大小表示一个输出被多个其他逻辑门的输入使用。如果删除太大,电路可能会受损或信号无法正确传递,因此需要解决这个问题。可以通过将一个信号分割为两个部分进行处理或创建缓冲区等方法来减小扇出的影响。

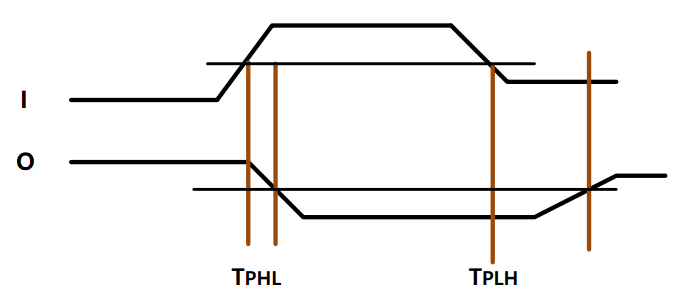

0x02 传播延迟(Propagation Delay)

传播延迟 (Propagation Delay) 是指逻辑电路从接收输入信号到产生输出结果所需的平均时间。它受逻辑门的数量及其延迟时间的影响,表示如下:

其中,(Propagation Delay)是传播延迟时间,

(Propagation delay time from High to Low)是输出响应输入信号从逻辑 1 变为逻辑 0 所需的时间,

(Propagation delay time from Low to High)是输出响应输入信号从逻辑 0 变为逻辑 1 所需的时间。

延迟时间随着通过门数的增加而增加,因此在设计逻辑电路时必须牢记这一点,以提高效率。

0x03 Verilog 中的 task 和 function

Verilog 中的任务 (task) 和函数 (function) 是用来减少代码重复的关键字,就像 C 语言中的函数一样。换句话说,在具有大量相同行为的项目中,任务和函数可以用来简化代码。任务和函数都可以有局部变量、全局变量、寄存器、时间变量、整数、实数等,但不能有导线。 它们也只包含行为语法,没有始终和初始语法。具体区别如下:

① task:

- 可以使用 task 和 endtask 将开始和结束包围起来进行声明。

- 可以包含延迟、时序和事件控制语句。

- 可以有一个或多个输入、输出、input 等参数,也可以没有任何参数。

- 内部可以同时调用任务(task)和函数(function)。

- 如果不使用时间延迟功能,可以进行综合。

- 可以在非零仿真时间下执行。

- 可以通过命令语句调用,但不能在表达式内部使用。

② function:

- 可以使用 "function" 和 "endfunction" 将开始和结束包围起来进行声明。

- 不能包含延迟、时序和事件控制语句。

- 至少有一个以上的输入,并且只有一个返回值。

- 内部只能调用函数(function)。

- 可以进行综合,并用于组合电路建模。

- 总是在仿真时间为 0 时执行。

0x04 FPGA 的工作原理

描述FPGA的工作原理:使用Vivado和Verilog语言验证FPGA工作时,可以使用以下程序。

Verilog 编码(Verilog Coding)

在 Vivado 中编写 Verilog 设计源代码和测试平台代码来控制门的行为。在这种情况下,变量值中的 0 或 1 可以作为 FPGA 中的 "开关 "来实现。(开关打开 = 1,开关关闭 = 0,等等)。

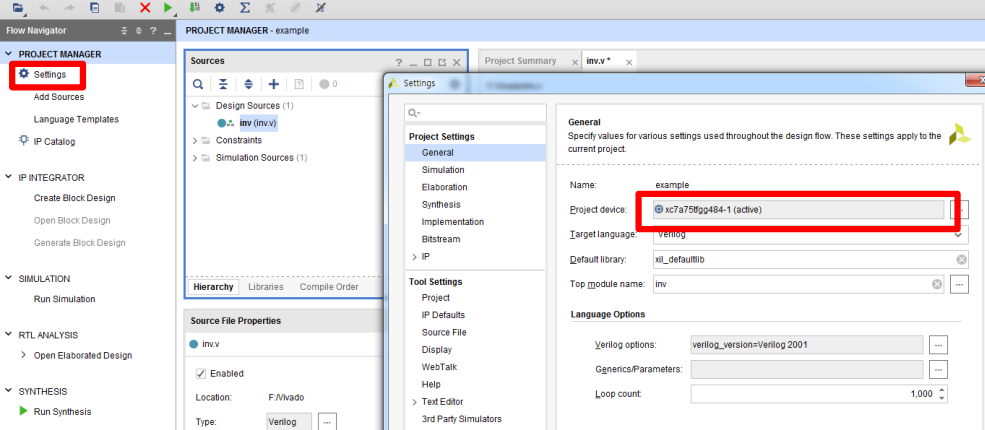

设备分配(Device assignment)

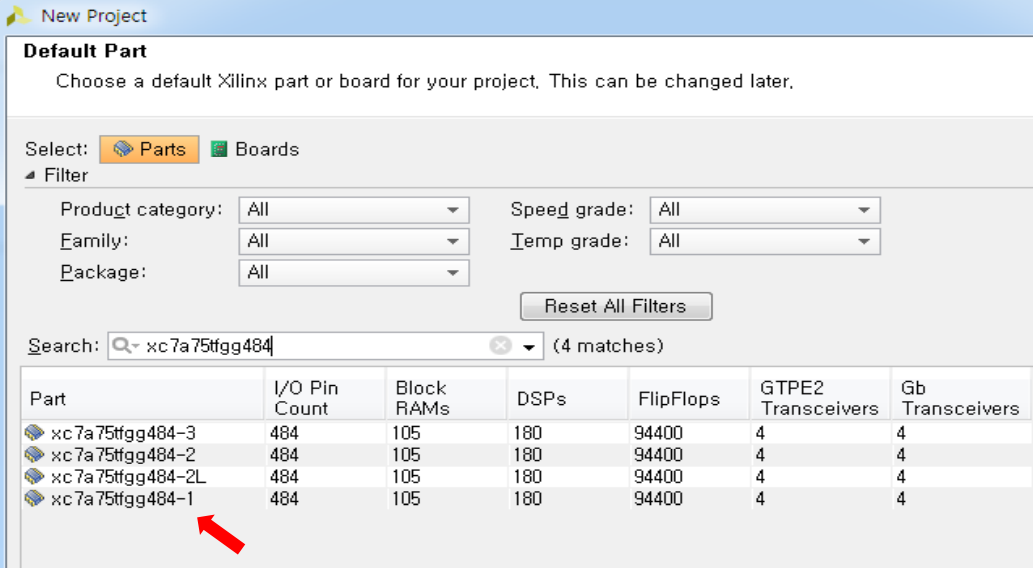

要操作FPGA,需要为项目分配相应的器件。在 Vivado 中,这可以在 Project Manager > Settings > Project device 菜单中完成,设备应为 xc7a75tfgg484-1 (Artix7)。Artix-7 FPGA 是 FPGA 器件,可为逻辑、信号处理、嵌入式存储器、LVDS I/O、存储器接口和收发器提供优化的性能。

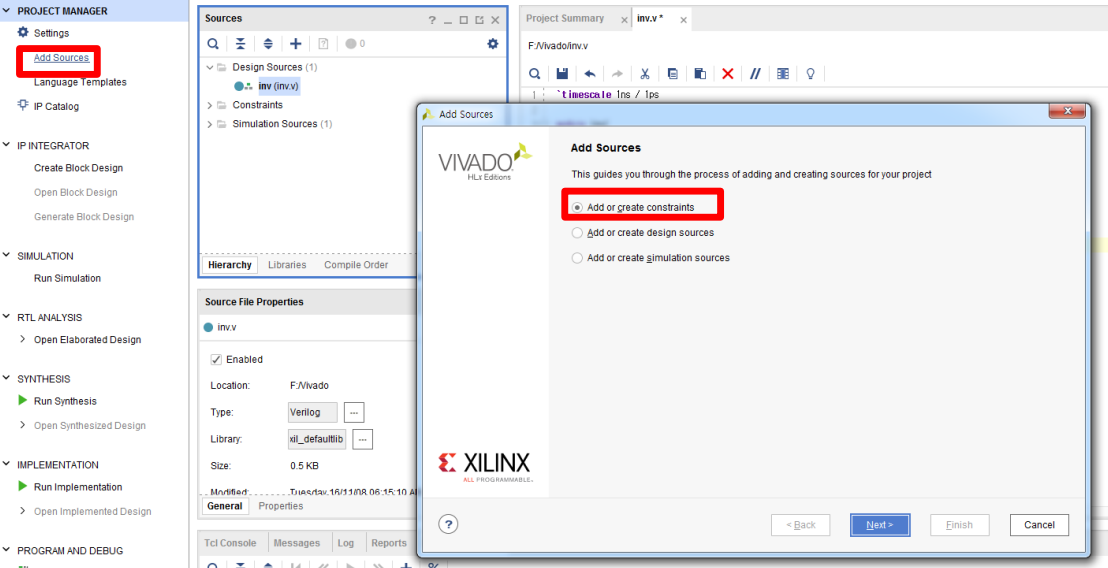

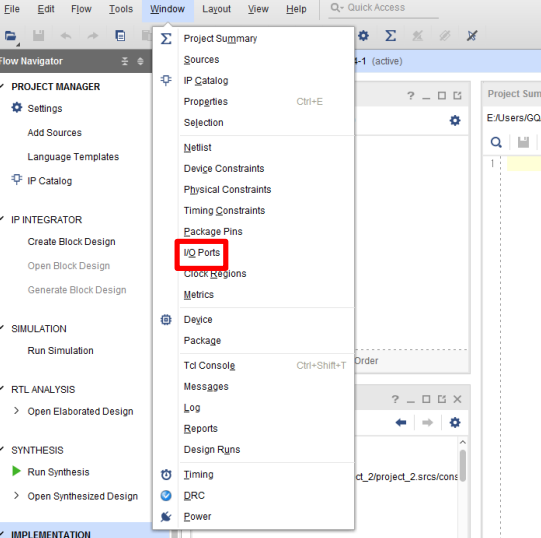

引脚分配(Pin assignment)

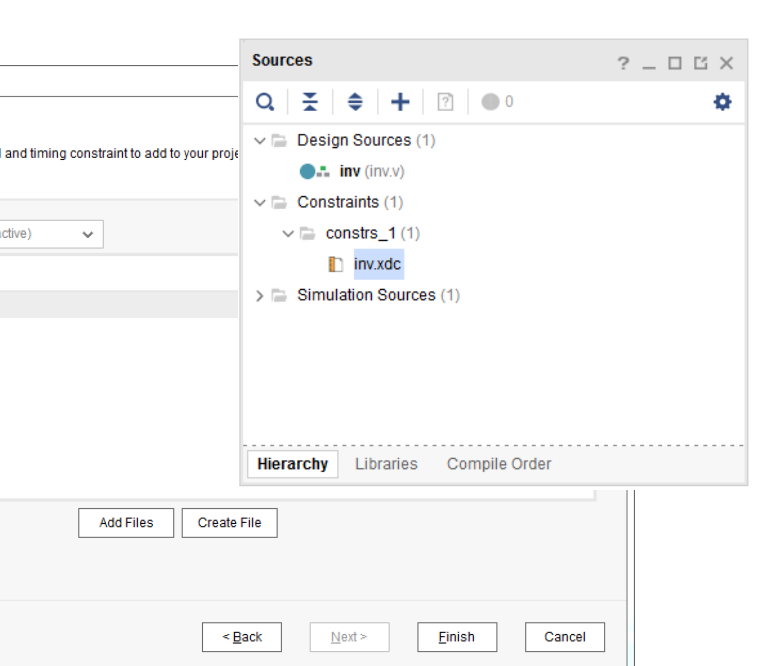

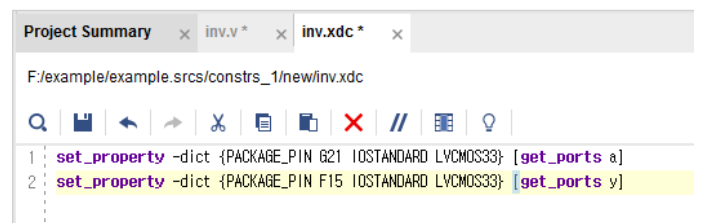

引脚只是 Verilog 代码中的输入和输出变量。您可以通过 Vivado 的 Project Manager > Add Sources > Add或create constraints > Create File 创建一个 .xdc 文件,并从 FPGA 引脚列表和Verilog 源的端口链接您要分配的引脚。举个例子:

set_property -dict {PACKAGE_PIN G21 IOSTANDARD LVCMOS33} [get_ports a] [get_ports a] [get_ports a] [get_ports a [get_ports a]综合/实现(Synthesis/Implement)

在 Vivado 中,可以通过 Synthesis > Run Synthesis、Implementation > Run Implemented > Open Implemented Design 创建综合设计和布线设计。

器件配置(Device Configuration)

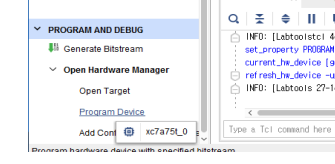

设备配置可以通过 Vivado 中的“编程和调试”>“生成比特流”>“打开硬件管理器”来完成。

FPGA 行为

在 Vivado 中,单击 Program and debug > Open Hardware Manager > Open Target > Auto Connect,然后在 Project[title] > Project[title]_runs > impl_1 文件夹中添加 debug_nets.ltx 文件。

Program and debug > Program Device > Debug probes file > Select the debug_nets.ltx file added above and specify the Program device(xc7a75t_0) to connect to the external FPGA device。

0x05 具体操作过程

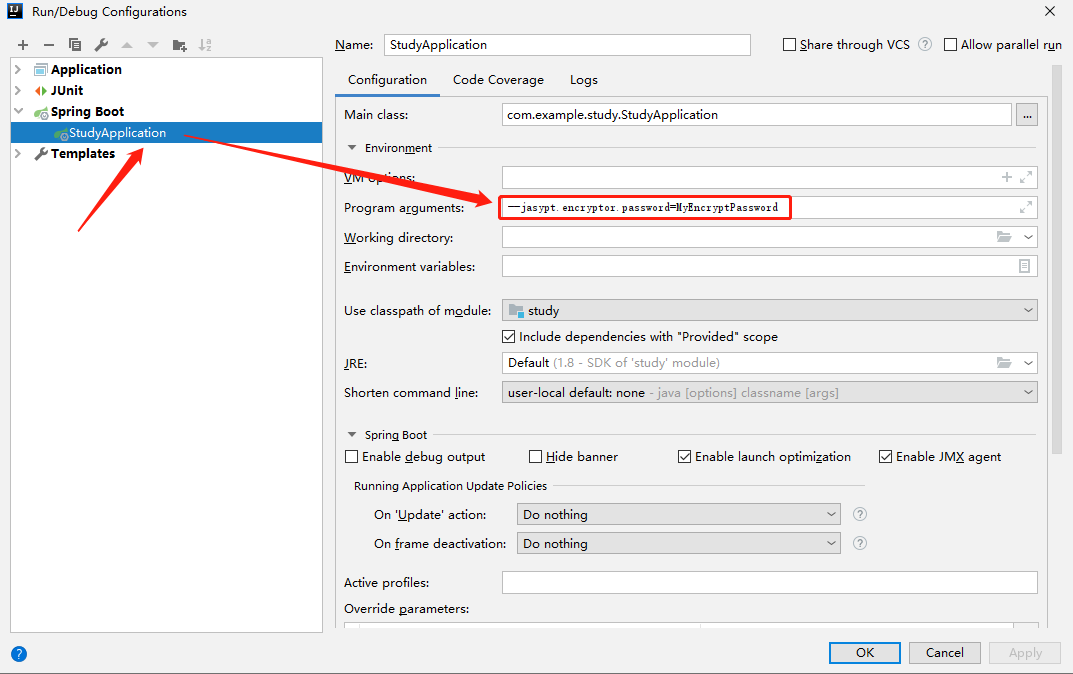

Device assignment:

Device assignment → Device : xc7a75tfgg484

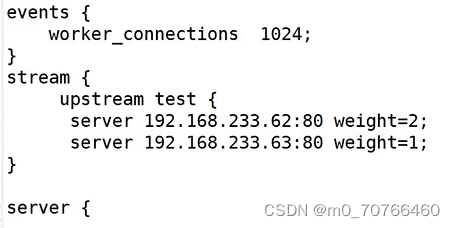

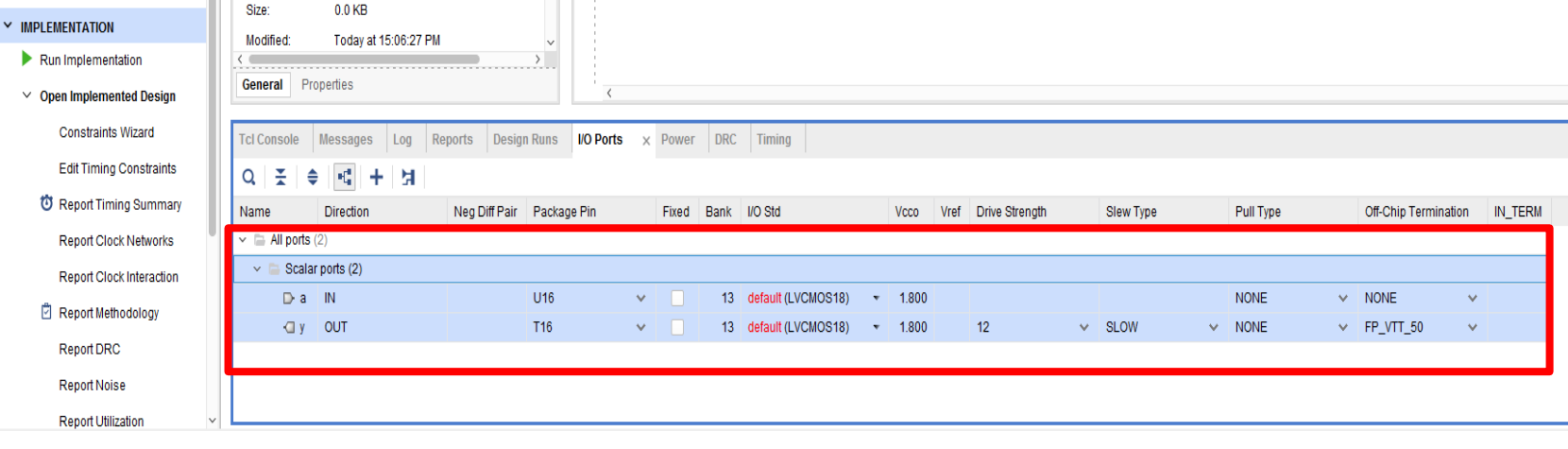

Pin assignment

链接你希望在 FPGA pin list 中分配的 Pin 和 Verilog 源端口:

set_property -dict {PACKAGE_PIN G21 IOSTANDARD LVCMOS33} [get_ports a]

set_property -dict {PACKAGE_PIN F15 IOSTANDARD LVCMOS33} [get_ports y]

Synthesis / Implementation:

Device configuration:

我的板子比较老,是 FPGA Starter Kit Ⅲ:

初始化状态如下所示:

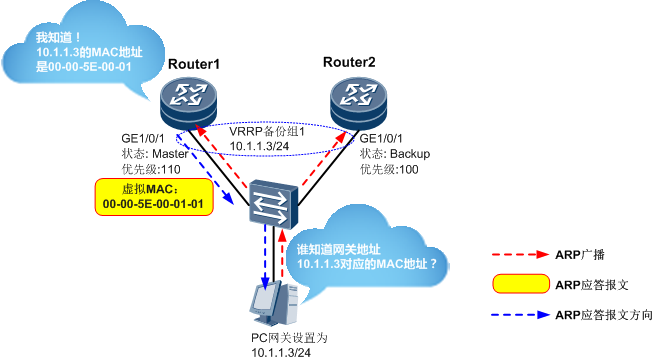

Open Target → 点击 auto connect,自动连接:

选择 Program Device:

🚩 输出结果演示:

📌 [ 笔者 ] 王亦优

📃 [ 更新 ] 2022.9.20

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |