基于FPGA的FIR低通滤波器实现(附工程源码)

文章目录

- 基于FPGA的FIR低通滤波器实现(附工程源码)

- 前言

- 一、matlab设计FIR滤波器,生成正弦波

- 1.设计FIR滤波器

- 1.生成正弦波.coe

- 二、vivado

- 1.fir滤波器IP核

- 2.正弦波生成IP核

- 3.时钟IP核设置

- 4.顶层文件/测试文件代码

- 三.simulation

- 四.源代码

前言

本文为FPGA实现FIR滤波器仿真过程,附源代码。

提示:以下是本篇文章正文内容,下面案例可供参考

一、matlab设计FIR滤波器,生成正弦波

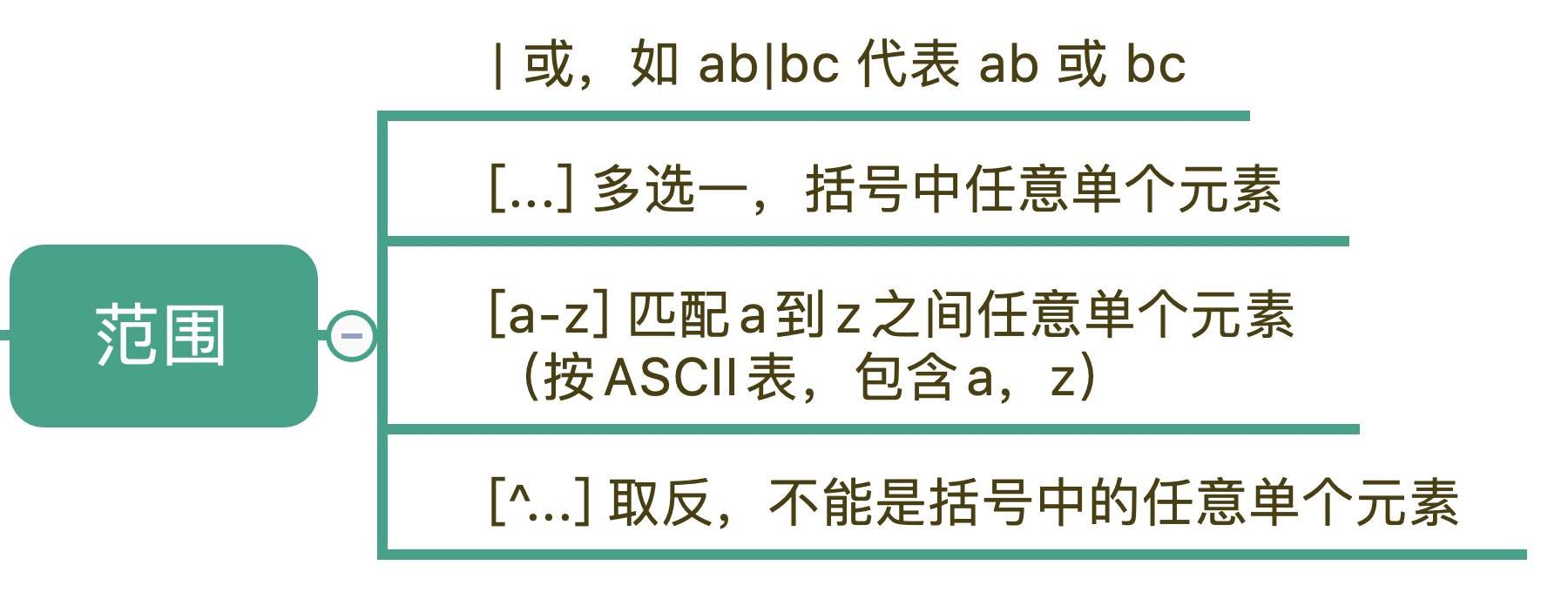

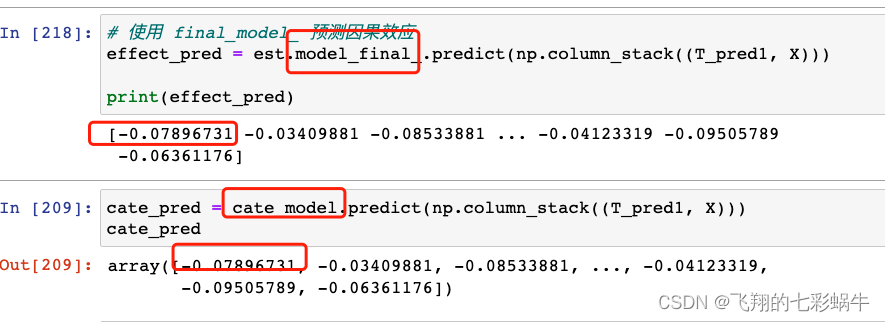

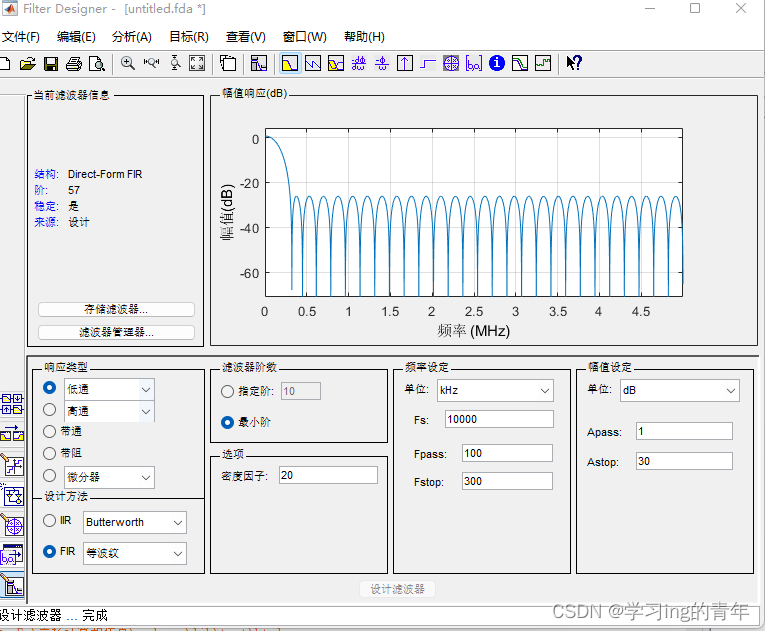

1.设计FIR滤波器

打开MATLAB在命令行窗口输入:

fadtool

回车后在滤波器设计界面设置滤波器参数如下

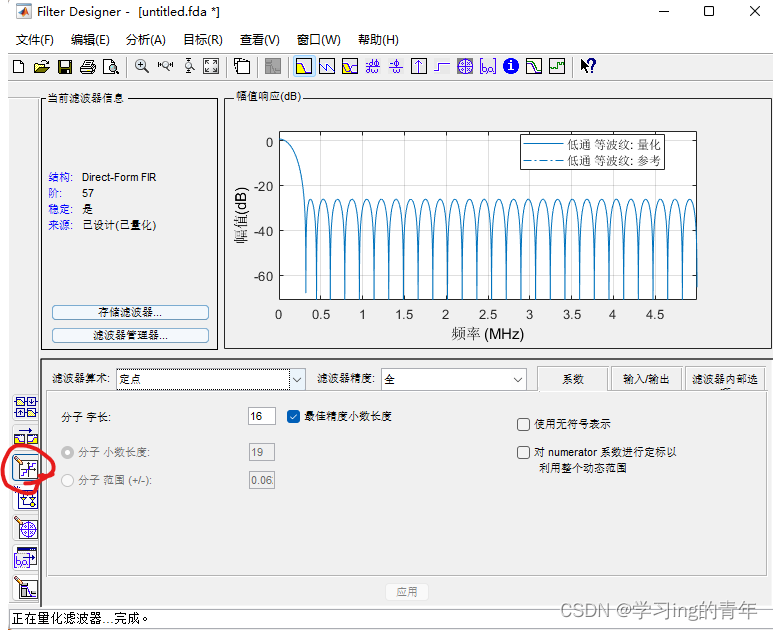

之后点击如图标志,设置定点,在菜单栏"目标(R)"出选择生成对应滤波器系数.COE文件

1.生成正弦波.coe

matlab代码如下

width=8; %rom的位宽

depth=1024; %rom的深度

x=linspace(0,2*pi,depth); %在一个周期内产生1024个采样点

y_sin=sin(x); %生成余弦数据

y_sin=round(y_sin*(2^(width-1)-1))+2^(width-1)-1; %将余弦数据全部转换为整数fid=fopen('C:\Users\lys\Desktop\fir\sin.coe','w'); %创建.coe文件

fprintf(fid,'%d,\n',y_sin); %向.coe文件中写入数据

fclose(fid); %关闭.coe文件

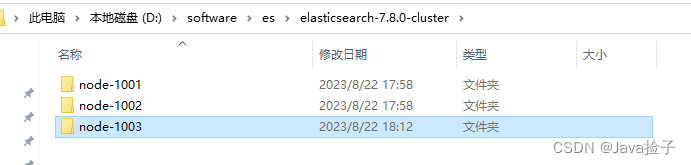

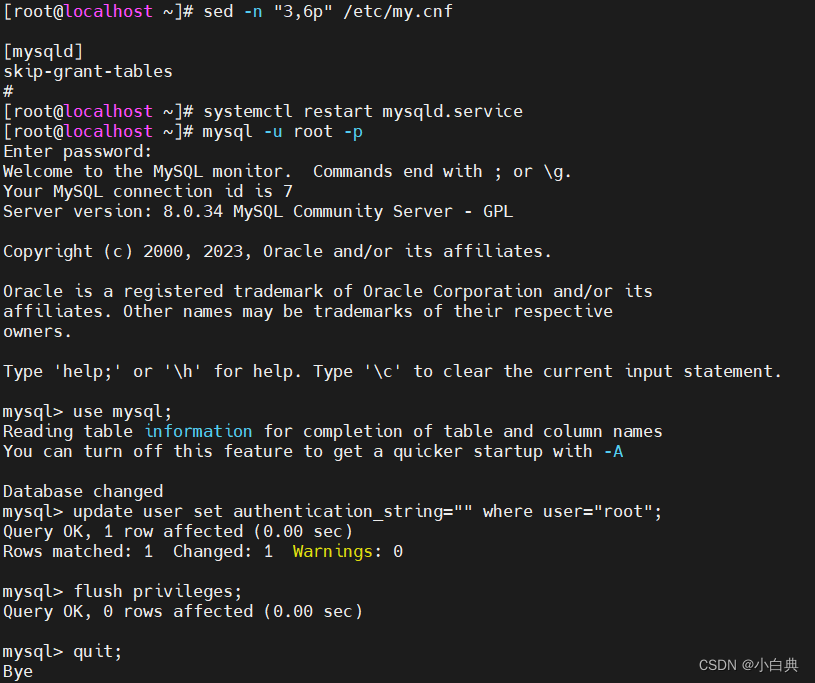

二、vivado

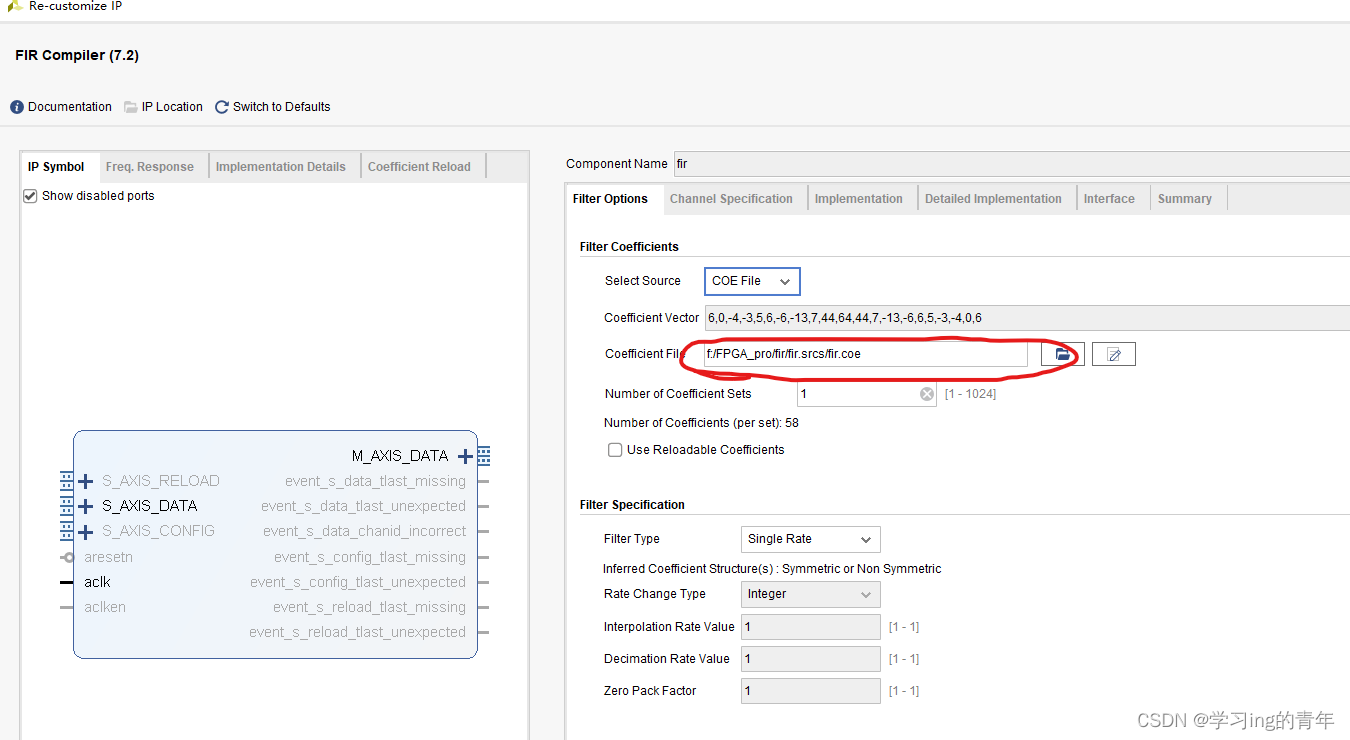

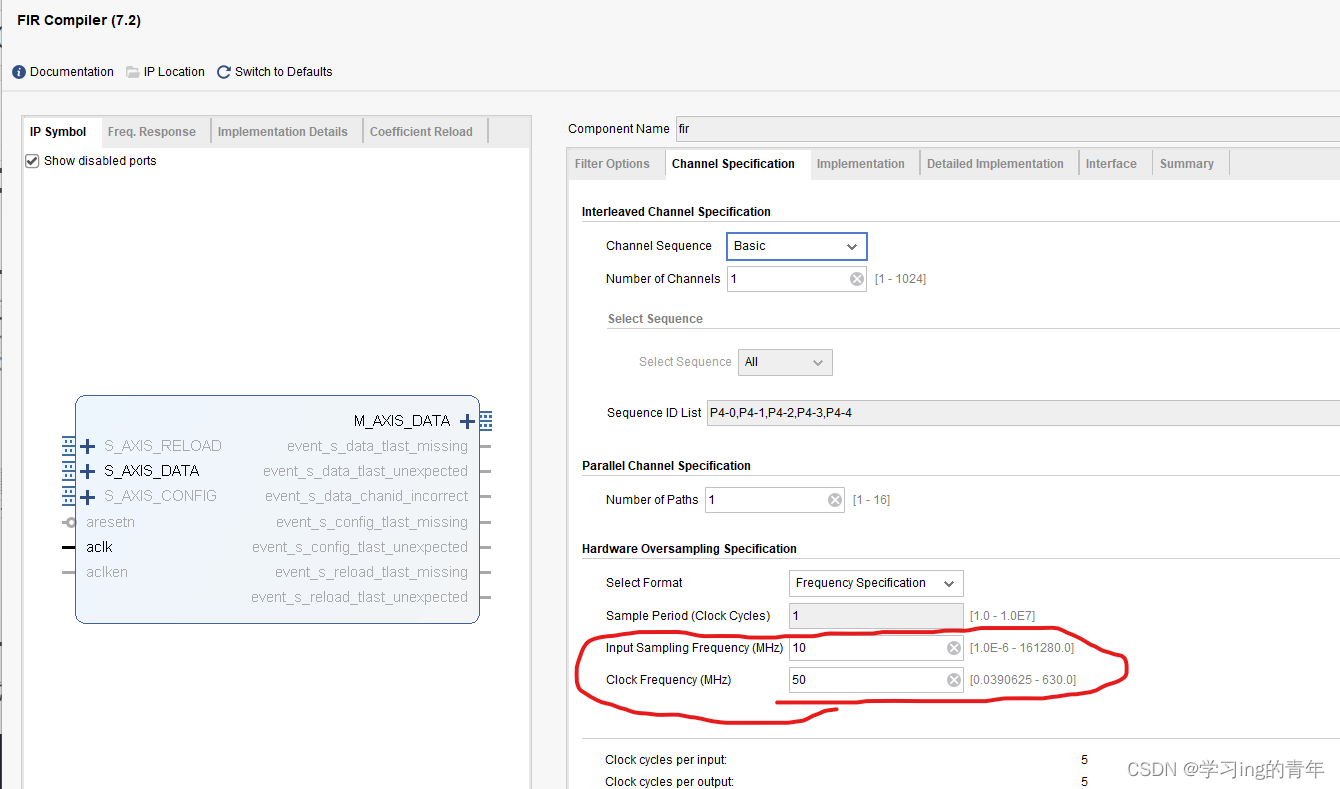

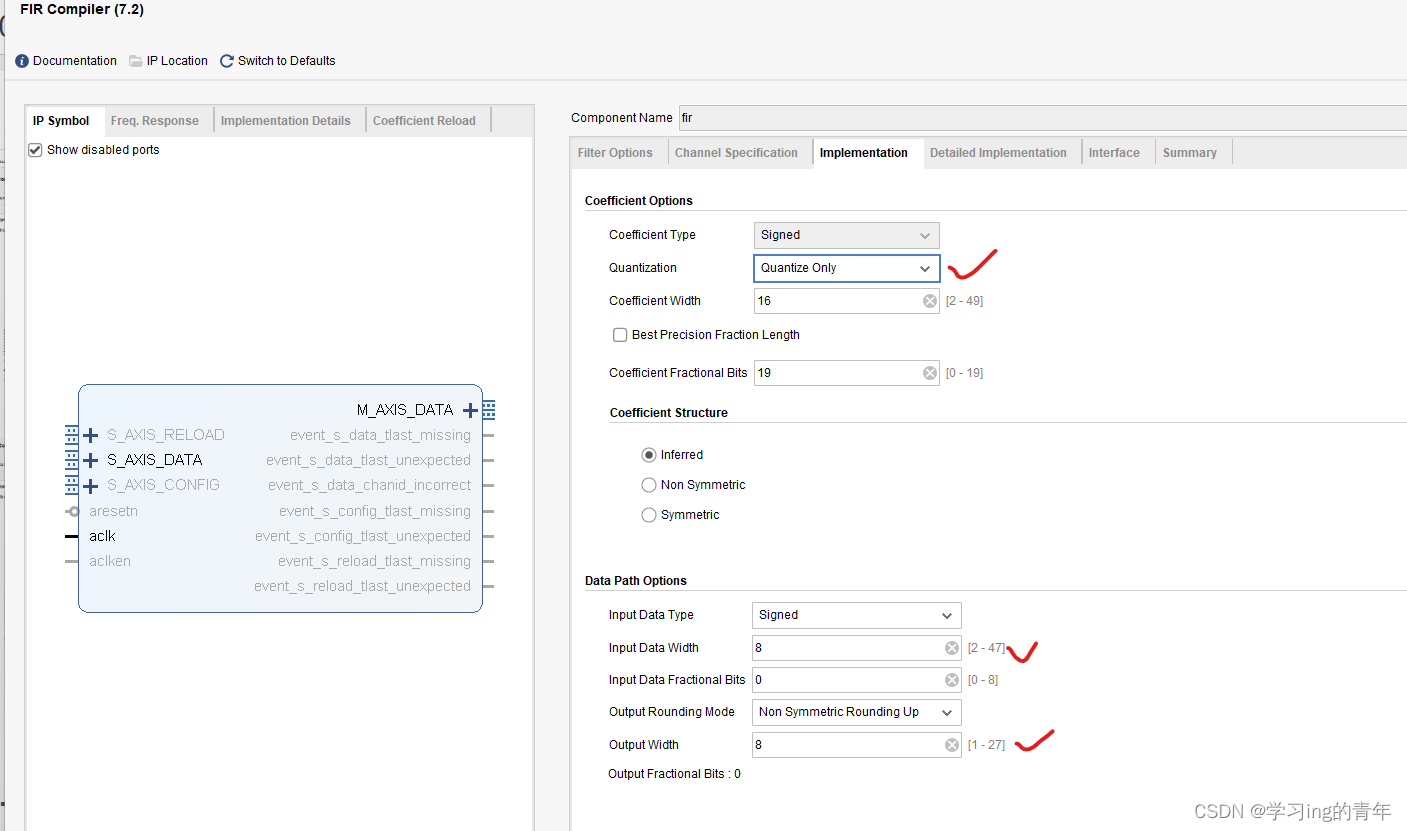

1.fir滤波器IP核

设置参数如下:

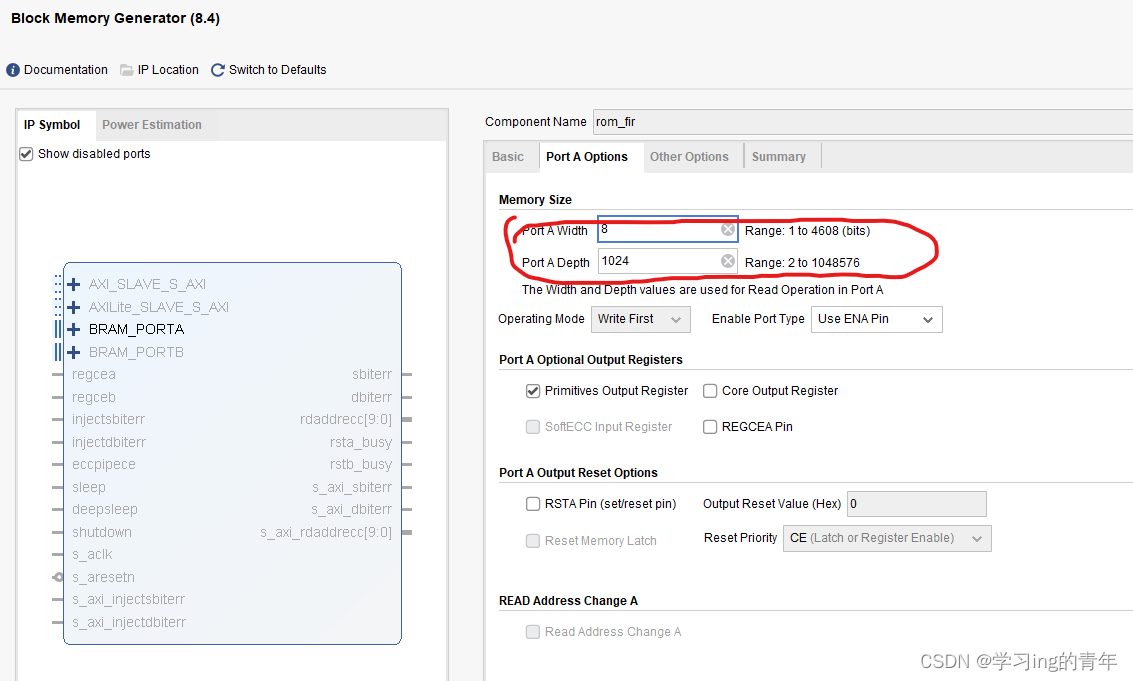

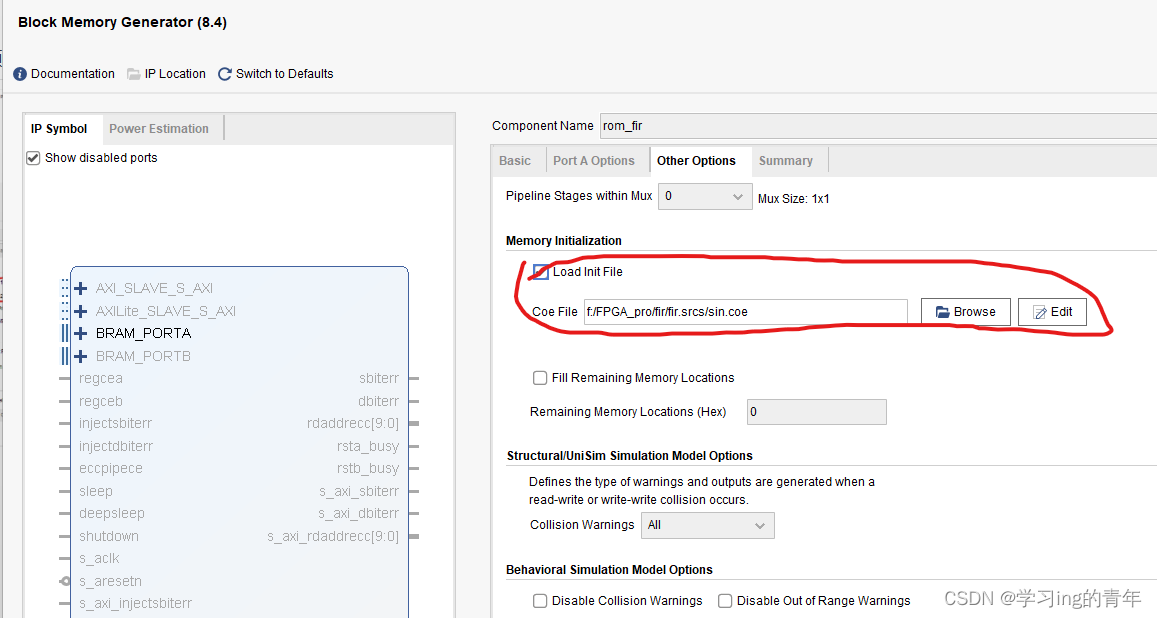

2.正弦波生成IP核

参数设置如下:

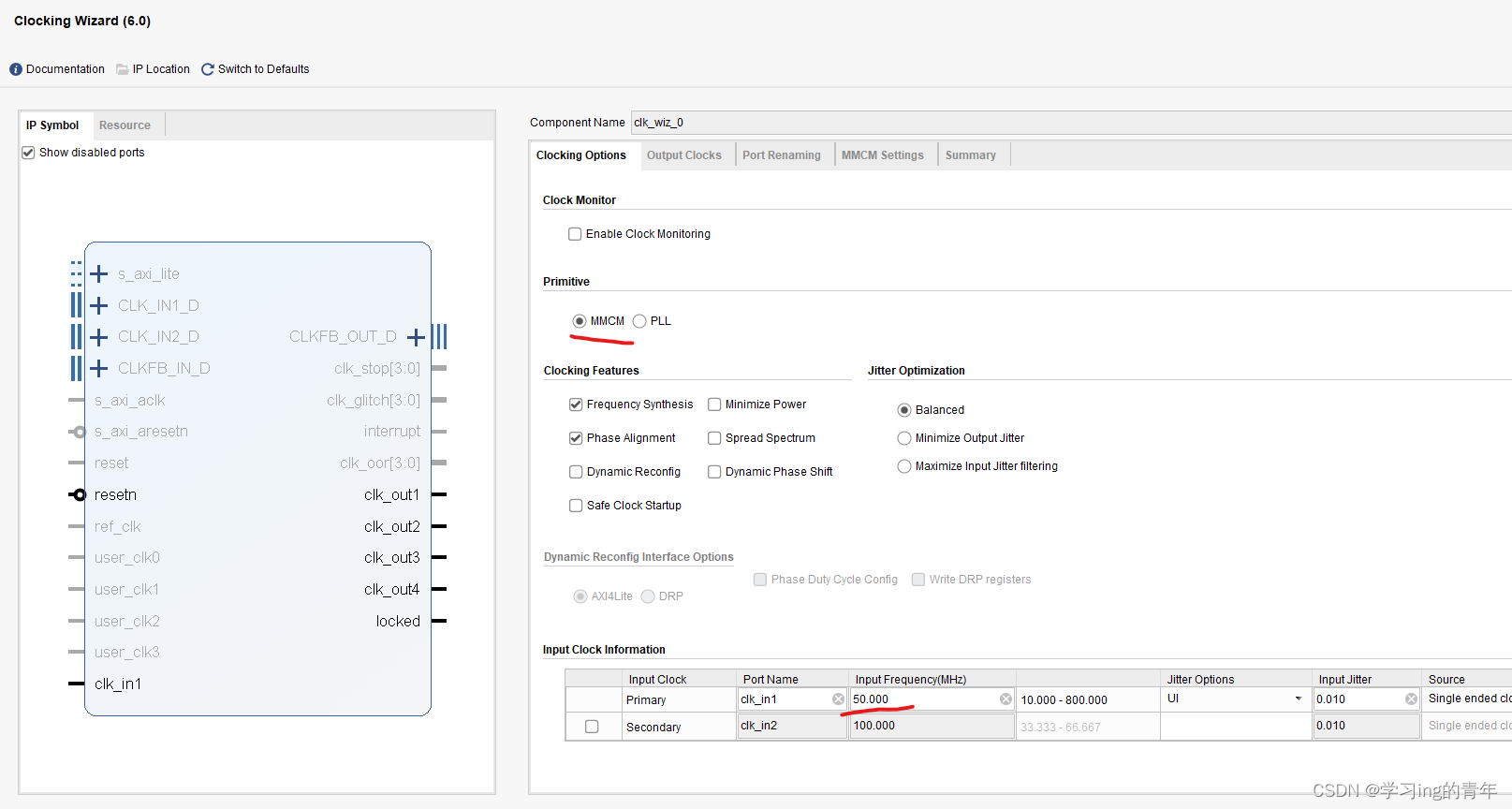

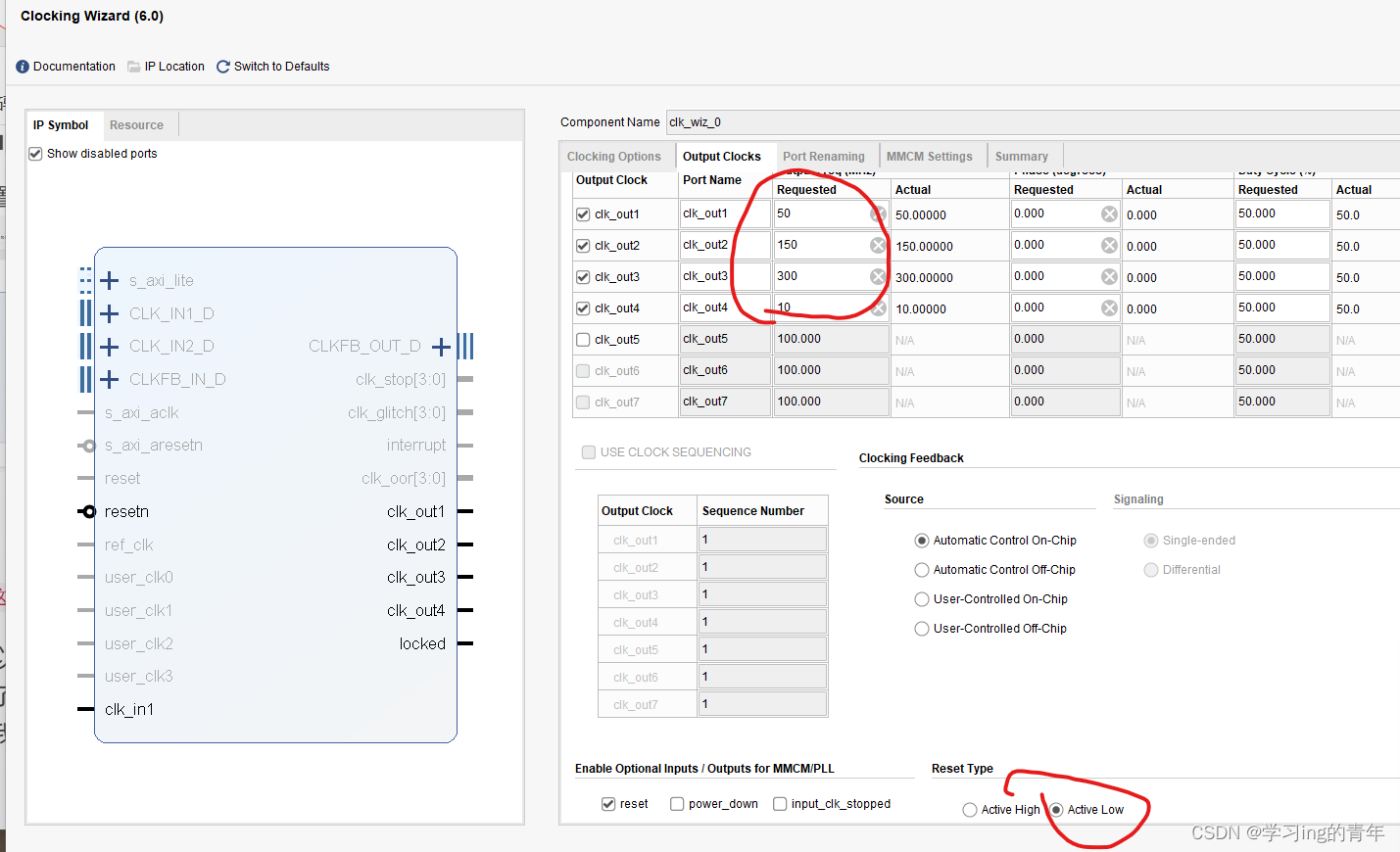

3.时钟IP核设置

参数设置如下:

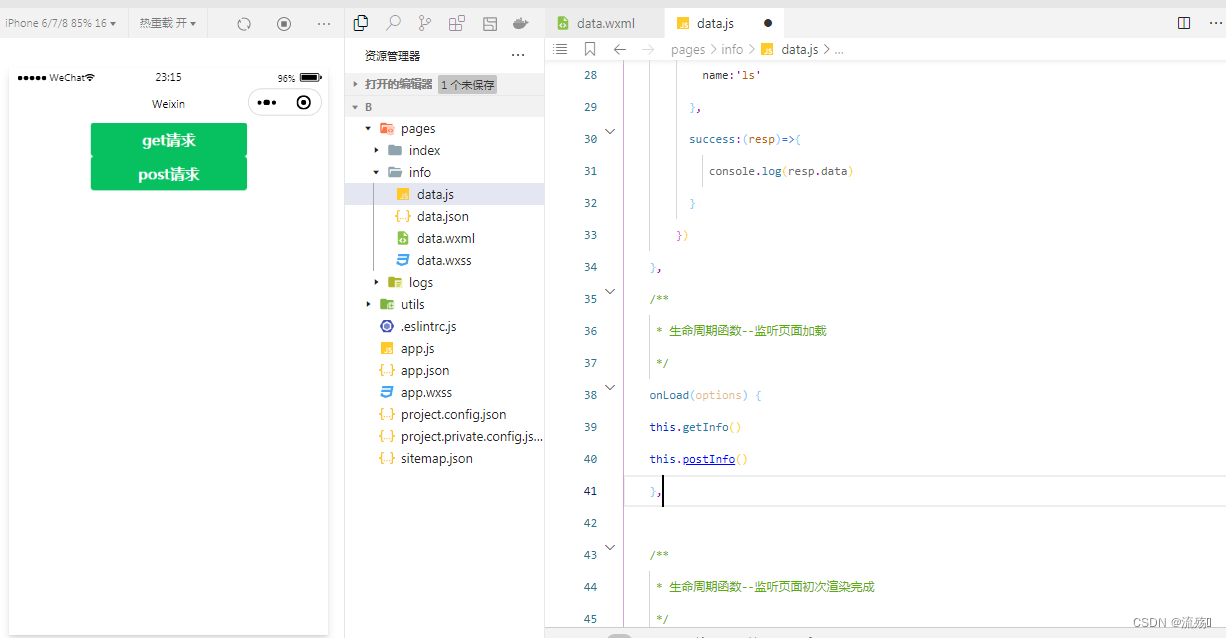

4.顶层文件/测试文件代码

`timescale 1ns / 1psmodule fir_top(input clk,input rst_n,input [1:0]rom_sel,output [7:0]douta,output [7:0]fir_out_data);wire clk_10m;wire clk_1;wire clk_2;wire clk_3;// clk_wiz_0 instance_name(

// .clk_out1(clk_1), // output clk_out1

// .clk_out2(clk_2),

// .clk_out3(clk_3),

// .clk_out4(clk_10m),

// .reset(rst_n), // input resetn

// .locked(), // output locked

// .clk_in1(clk)

// ); // input clk_in1clk_wiz_0 instance_name(// Clock out ports.clk_out1(clk_1), // output clk_out1.clk_out2(clk_2), // output clk_out2.clk_out3(clk_3), // output clk_out3.clk_out4(clk_10m), // output clk_out4// Status and control signals.resetn(rst_n), // input reset.locked(), // output locked// Clock in ports.clk_in1(clk)); // input clk_in1wire clk_rom;assign clk_rom = (rom_sel == 0)?clk_1:((rom_sel == 1)?clk_2:clk_3);reg [9:0]addra;always@(posedge clk_rom or negedge rst_n)beginif(!rst_n)addra <= 'd0;elseaddra <= addra + 1'b1;endrom_fir rom_inst (.clka(clk_rom), // input wire clka.ena(1'b1), // input wire ena.addra(addra), // input wire [9 : 0] addra.douta(douta) // output wire [7 : 0] douta);wire [7:0]fir_in_data;assign fir_in_data = douta - 'd128;fir fir_inst (.aclk(clk), // input wire aclk.s_axis_data_tvalid(clk_10m), // input wire s_axis_data_tvalid.s_axis_data_tready(), // output wire s_axis_data_tready.s_axis_data_tdata(fir_in_data), // input wire [7 : 0] s_axis_data_tdata.m_axis_data_tvalid(), // output wire m_axis_data_tvalid.m_axis_data_tdata(fir_out_data) // output wire [7 : 0] m_axis_data_tdata);endmodule`timescale 1ns / 1psmodule fir_top_tb;reg clk;reg rst_n;reg [1:0]rom_sel;wire [7:0]douta;wire [7:0]fir_out_data;fir_top fir_top_inst(.clk (clk),.rst_n (rst_n),.rom_sel(rom_sel),.douta (douta),.fir_out_data(fir_out_data));initial clk = 0;always#10 clk = ~clk;initial beginrst_n = 0;rom_sel = 0;#200;rst_n = 1'b1;#200000;rom_sel = 1;#200000;rom_sel = 2;#200000;$stop;endendmodule三.simulation

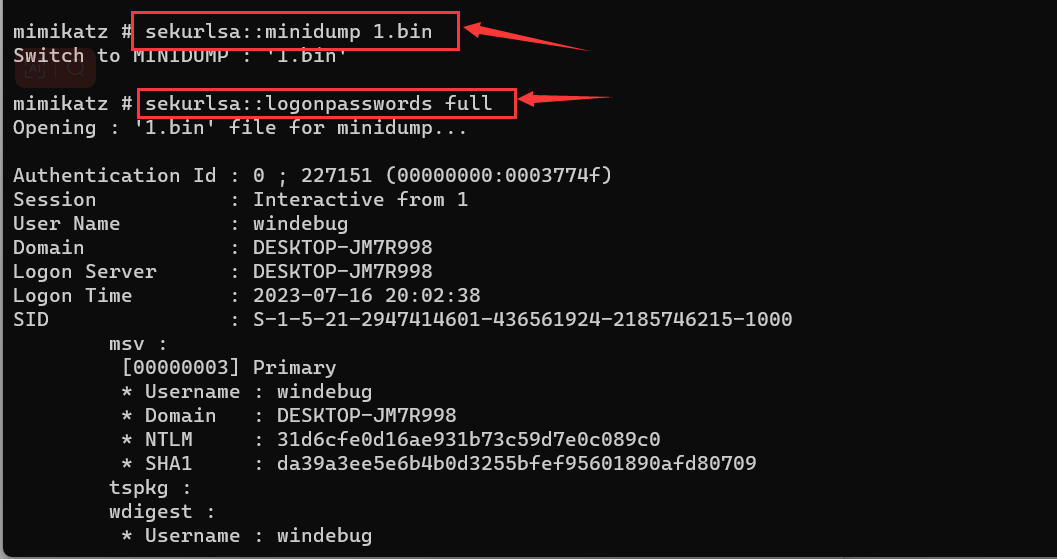

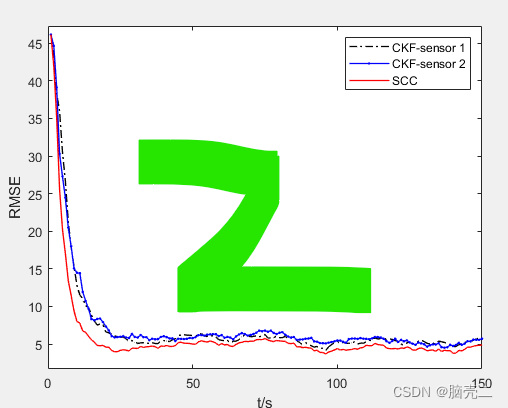

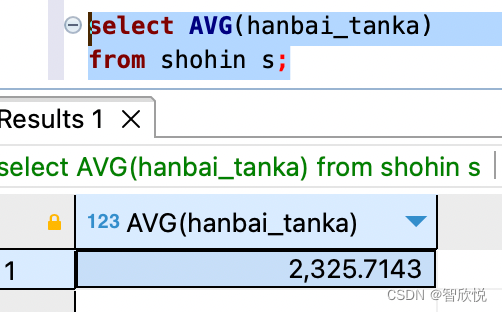

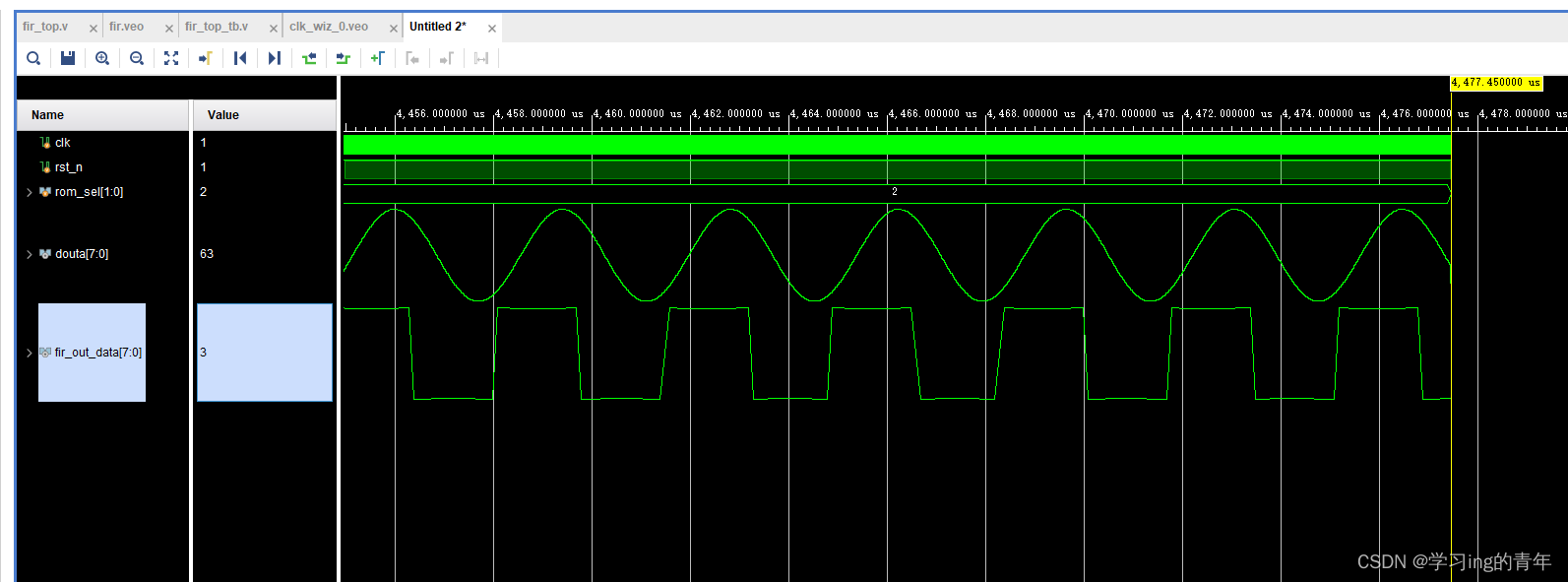

只为测试功能,未考虑滤波器性能,所以效果不佳,结果实现如下

四.源代码

https://download.csdn.net/download/qq_42761380/88243346