中断管理

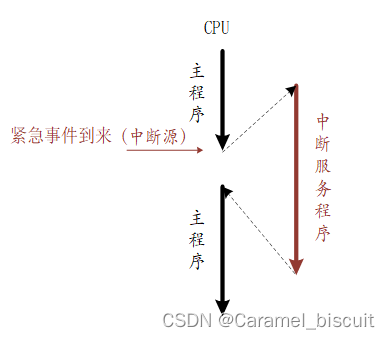

什么是中断?简单的解释就是系统正在处理某一个正常事件,忽然被另一个需要马上处理的紧急事件打断,系统转而处理这个紧急事件,待处理完毕,再恢复运行刚才被打断的事件。生活中,我们经常会遇到这样的场景:

当你正在专心看书的时候,忽然来了一个电话,于是记下书的页码,去接电话,接完电话后接着刚才的页码继续看书,这是一个典型的中断的过程。

电话是老师打过来的,让你赶快交作业,你判断交作业的优先级比看书高,于是电话挂断后先做作业,等交完作业后再接着刚才的页码继续看书,这是一个典型的在中断中进行任务调度的过程。

这些场景在嵌入式系统中也很常见,当CPU正在处理内部数据时,外界发生了紧急情况,要求CPU暂停当前的工作转去处理这个异步事件。处理完毕后,再回到原来被中断的地址,继续原来的工作,这样的过程称为中断。

实现这一功能的系统称为中断系统,申请CPU中断的请求源称为中断源。

中断是一种异常,异常是导致处理器脱离正常运行转向指向特殊代码的任何事件,如果不及时地进行处理,轻则系统出错,重则系统瘫痪。所以正确地处理异常,避免错误的发生是提高软件鲁棒性的重要一环。

中断处理与CPU架构密切相关,所以,本章会先介绍 ARM Cortex-M 的 CPU 架构,然后结合 Cortex-M CPU 架构来介绍 RT-Thread 的中断管理机制,读完本章,大家将深入了解 RT-Thread 的中断处理过程,如何添加中断服务程序(ISR)以及相关的注意事项。

Cortex-M CPU架构基础

ARM Cortex-M 处理器有一个非常不同的架构,Cortex-M是一个家族系列,其中包括Cortex M0/M3/M4/M7多个不同型号,每个型号之间会有些区别,比如说Cortex-M4 比 Cortex-M3 多了浮点计算功能等,但它们的编程模型基本是一致的。

寄存器简介

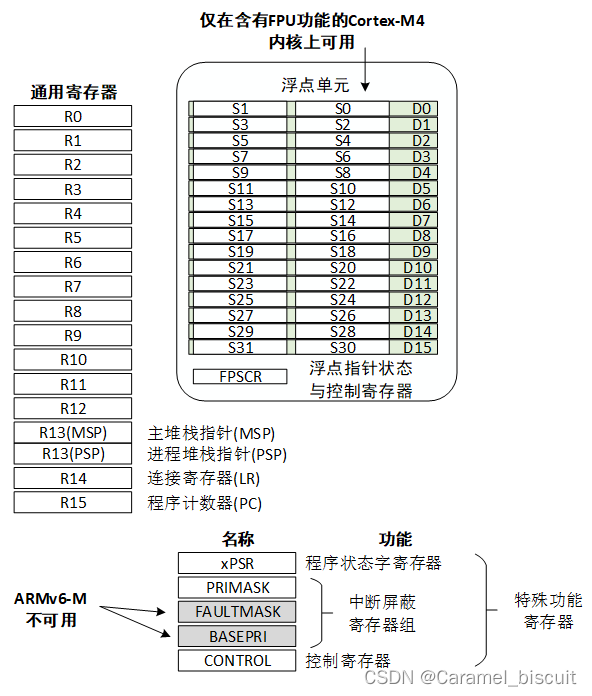

Cortex-M系列CPU的寄存器组里有R0~R15共16个通用寄存器组和若干特殊功能寄存器,如下图所示。

通用寄存器组里的R13作为堆栈指针寄存器(Stack Pointer,SP);R14作为连接寄存器(Link Register,LR),用于在调用子程序时,存放返回地址;R15作为程序计数器(Program Counter,PC),其中堆栈指针寄存器可以是主堆栈指针(MSP),也可以是进程堆栈指针(PSP)。

特殊功能寄存器包括程序状态寄存器组(PSRs)、中断屏蔽寄存器组(PRIMASK,FAULTMASK,BASEPRI)、控制寄存器(CONTROL),可以通过MSR/MRS指令访问特殊功能寄存器。

MRS R0,CONTROL; 读取CONTROL到R0中

MSR CONTROL,R0 写入R0到CONTROL寄存器中

程序状态字寄存器里保存算术与逻辑标志,例如负数标志,零结果标志,溢出标志等等。中断屏蔽寄存器组控制Cortex-M的中断除能。控制寄存器用来定义特权级别和当前使用哪个堆栈指针。

操作模式和特权级别

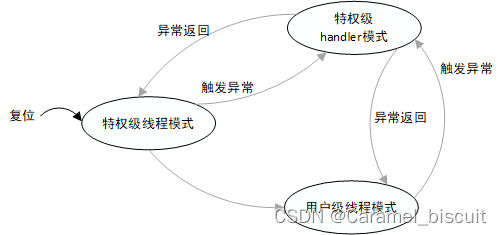

Cortex-M引入了操作模式和特权级别的概念,分别为线程模式和处理模式,如果进入异常或中断处理则进入处理模式,其它情况则为线程模式。

Cortex-M有两个运行级别,分别为特权级和用户级,线程模式可以工作在特权级或者用户级,而处理模式总工作在特权级,可通过CONTROL特殊寄存器控制。

Cortex-M的堆栈寄存器SP对应两个物理寄存器MSP和PSP,MSP为主堆栈,PSP为进程堆栈,处理模式总是使用MSP作为堆栈,线程模式可以选择使用MSP或PSP作为堆栈,同样通过CONTROL特殊寄存器控制。

复位后,Cortex-M默认进入线程模式、特权级、使用MSP堆栈。

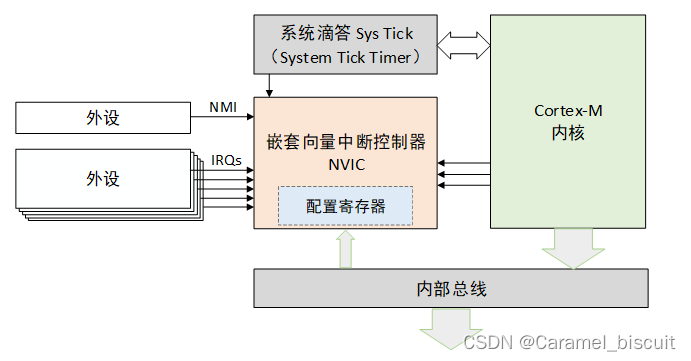

嵌套向量中断控制器

Cortex-M中断控制器名为NVIC(嵌套向量中断控制器),支持中断嵌套功能。

当一个中断触发并且系统进行响应时,处理器硬件会将当前运行位置的上下文寄存器自动压入中断栈中,这部分的寄存器包括PSR、PC、LR、R12、R3~R0寄存器。

当系统正在服务一个中断时,如果有一个更高优先级的中断触发,那么处理器同样会打断当前运行的中断服务程序,然后把这个中断服务程序的上下文寄存器自动保存到中断栈中。

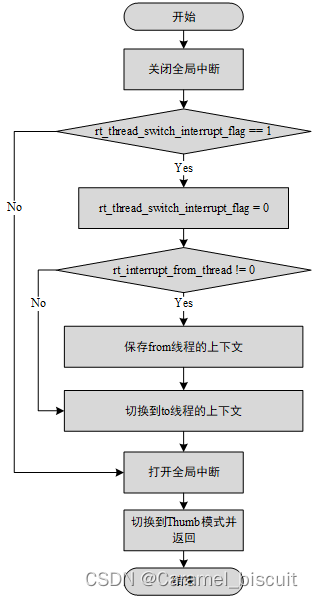

PendSV系统调用

PendSV也称为可悬起的系统调用,它是一种异常,可以像普通的中断一样被挂起,专门用于辅助操作系统进行上下文切换。

PendSV异常会被初始化为最低优先级的异常。

每次需要进行上下文切换时,会手动触发PendSV异常,在PendSV异常处理函数中进行上下文切换。

中断向量表

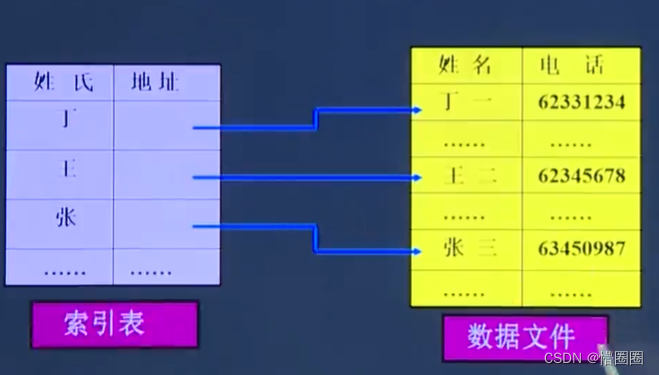

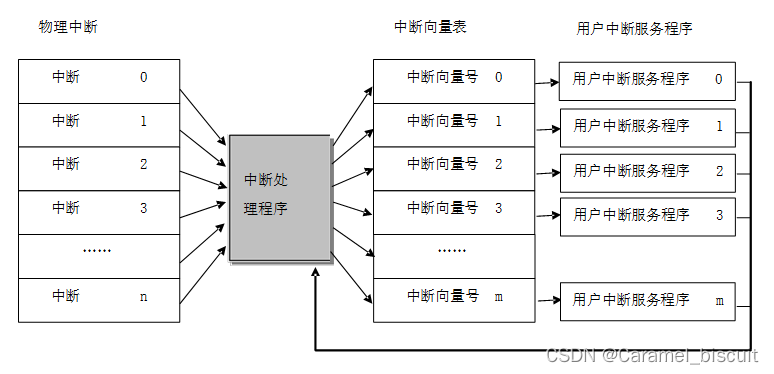

中断向量表是所有中断处理程序的入口。

把一个函数(用户中断服务程序)同一个虚拟中断向量表的中断向量联系在一起。当中断向量对应中断发生的时候,被挂接的用户中断服务程序就会被调用执行。

在Cortex-M内核上,所有中断都采用中断向量表的方式进行处理,即当一个中断触发时,处理器将直接判定是哪个中断源,然后直接跳转到相应的固定位置进行处理,每个中断服务程序必须排列在一起放在统一的地址上(这个地址必须要射到NVIC的中断向量偏移寄存器中)。中断向量表一般由一个数组定义或在起始代码中给出,默认采用起始代码给出:

__Vectors DCD __initial_sp ; Top of StackDCD Reset_Handler ; Reset 处理函数DCD NMI_Handler ; NMI 处理函数DCD HardFault_Handler ; Hard Fault 处理函数DCD MemManage_Handler ; MPU Fault 处理函数DCD BusFault_Handler ; Bus Fault 处理函数DCD UsageFault_Handler ; Usage Fault 处理函数DCD 0 ; 保留DCD 0 ; 保留DCD 0 ; 保留DCD 0 ; 保留DCD SVC_Handler ; SVCall 处理函数DCD DebugMon_Handler ; Debug Monitor 处理函数DCD 0 ; 保留DCD PendSV_Handler ; PendSV 处理函数DCD SysTick_Handler ; SysTick 处理函数… …NMI_Handler PROCEXPORT NMI_Handler [WEAK]B .ENDP

HardFault_Handler PROCEXPORT HardFault_Handler [WEAK]B .ENDP

… …[WEAK]标识,是符号弱化标识,在[WEAK]前面的符号(如NMI_Handler、HardFault_Handler)将被执行弱化处理,如果整个代码在链接时遇到了名称相同的符号(如与NMI_Handler相同名称的函数),那么代码将使用未被弱化定义的符号(与 NMI_Handler 相同名称的函数),而与弱化符号相关的代码将被自动丢弃。

以SysTick中断为例,在系统启动代码上,需要填上SysTick_Handler中断入口函数,然后实现该函数即可对 SysTick 中断进行响应,中断处理函数示例程序如下所示:

void SysTick_Handler(void)

{/* enter interrupt */rt_interrupt_enter();rt_tick_increase();/* leave interrupt */rt_interrupt_leave();

}中断处理过程

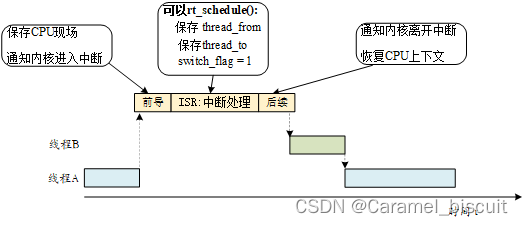

RTT中断管理中,将中断处理程序分为中断前导程序、用户中断服务程序、中断后续程序三部分,如下图:

中断前导程序

- 保存CPU中断现场,这部分跟CPU架构相关,不同CPU架构的实现方式有差异。

对于Cortex-M来说,该工作由硬件自动完成。当一个中断触发并且系统进行响应时,处理器硬件会将当前运行部分的上下文寄存器自动压入中断栈中,这部分的寄存器包括PSR、PC、LR、R12、R3~R0寄存器。 - 通知内核进入中断状态,调用rt_interrupt_enter()函数,作用是把全局变量rt_interrupt_nest加1,用它来记录中断嵌套的层数。

void rt_interrupt_enter(void)

{rt_base_t level;RT_DEBUG_LOG(RT_DEBUG_IRQ, ("irq coming..., irq nest:%d\n",rt_interrupt_nest));level = rt_hw_interrupt_disable();rt_interrupt_nest ++;RT_OBJECT_HOOK_CALL(rt_interrupt_enter_hook,());rt_hw_interrupt_enable(level);

}

RTM_EXPORT(rt_interrupt_enter);

用户中断服务程序

在用户中断服务程序(ISR)中,分为两种情况,第一张情况是不进行线程切换,这种情况下用户中断服务程序和中断后续程序运行完毕后退出中断模式,返回被中断的线程。

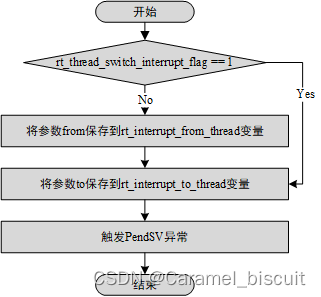

另一种情况是,在中断处理过程中需要进行线程切换,这种情况会调用**rt_hw_context_switch_interrupt()**函数进行上下文切换,该函数跟CPU架构相关,不同CPU架构的实现方式有差异。

在Cortex-M架构中,rt_hw_context_switch_interrupt()的函数实现流程如图。

它将设置需要切换的线程rt_interrupt_to_thread变量,然后触发PendSV异常(PendSV异常是专门用来辅助上下文切换的,且被初始化为最低优先级的异常)。

PendSV异常被触发后,不会立即进行PendSV异常中断处理程序,因为此时还在中断处理中,只有当中断后续程序运行完毕,真正退出中断处理后,才进入PendSV异常中断处理程序。

中断后续程序

- 通知内核离开中断状态,通过调用rt_interrupt_leave()函数,将全局变量rt_interrupt_nest减1.

void rt_interrupt_leave(void)

{rt_base_t level;level = rt_hw_interrupt_disable();rt_interrupt_nest --;rt_hw_interrupt_enable(level);

}

- 恢复中断前的CPU上下文,如果在中断处理过程中未进行线程切换,那么恢复from线程的CPU上下文,如果在中断中进行了线程切换,那么恢复to线程的CPU上下文。

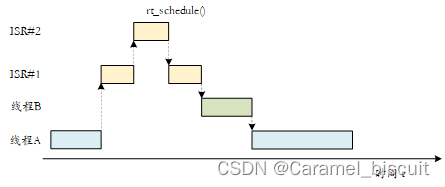

中断嵌套

在允许中断嵌套的情况下,在执行中断服务程序的过程中,如果出现高优先级的中断,当前中断服务程序的执行将被打断,以执行高优先级中断的中断服务程序,当高优先级中断的处理完成后,被打断的中断服务程序又继续得到执行,如果需要进行线程调度,线程的上下文切换在所有中断处理程序都运行结束时才发生。

中断栈

在系统响应中断前,处理器需要把当前线程的上下文保存起来(通常保存在当前线程的线程栈中),再调用中断服务程序进行中断响应、处理。

在中断处理函数中很可能会有自己的局部变量,这些都需要相应的栈空间来保存,所以中断响应仍然需要一个栈空间来作为上下文,运行中断处理函数。

中断栈可以保存在被打断线程的栈中,当从中断退出时,返回相应的线程继续执行。

中断栈也可以与线程栈完全分离,每次进入中断时,在保存完打断线程上下文后,切换到新的中断栈独立运行。

在中断退出时,再做相应的上下文恢复。

使用独立中断栈相对来说更容易实现,并且对于线程栈使用情况也比较容易了解和掌握(否则必须要为中断预留空间,如果系统支持中断嵌套,还需要考虑应该为嵌套中断预留多大的空间)。

RTT采用的方式是提供独立的中断栈,即中断发生时,中断的前期处理程序会将用户的栈指针更换到系统事先留出的中断栈空间中,等中断退出时再恢复用户的栈指针。

**这样中断就不会占用线程的栈空间,**从而提高了内存空间的利用率,且随着线程的增加,这种减少内存占用的效果也越明显。

在Cortex-M处理器内核里有两个堆栈指针,一个是主堆栈指针(MSP),是默认的堆栈指针,在运行第一个线程之前和在中断和异常服务程序里使用;另一个是线程堆栈指针(PSP),在线程里使用。

在中断和异常服务程序退出时,修改LR寄存器的第2位的值为1,线程的SP就由MSP切换到PSP。