1.1PHY接口发展

(1)MII支持10M/100Mbps,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多。参考芯片:DP83848 、DM900A(该芯片内部集成了MAC和PHY接口)。 DP83848芯片只支持10、100兆网络通信速度,采用4/5B编码。

(2)RMII是简化的MII接口,支持10M/100Mbps,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50兆的总线时钟,是MII接口时钟的两倍。

(3)SMII是由思科提出的一种媒体接口,支持10M/100Mbps,接口时钟频率125MHZ。它有比RMII更少的信号线数目,S表示串行的意思。

(4)GMII是千兆网的MII接口,工作时钟125MHz,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式。用8位接口数据。

(5)RGMII接口,表示简化了的GMII接口。工作时钟125MHz,RGMII均采用4位数据接口,并且在上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式,支持传输速率:10M/100M/1000Mb/s ,其对应clk 信号分别为:2.5MHz/25MHz/125MHz。

(6)SGMII,即Serial GMII,串行GMII,收发各一对差分信号线,时钟频率625MHz,在时钟信号的上升沿和下降沿均采样,参考时钟RX_CLK由PHY提供,是可选的,主要用于MAC侧没有时钟的情况,一般情况下,RX_CLK不使用。收发都可以从数据中恢复出时钟。

在TXD发送的串行数据中,每8比特数据会插入TX_EN/TX_ER 两比特控制信息,同样,在RXD接收数据中,每8比特数据会插入RX_DV/RX_ER 两比特控制信息,所以总的数据速率为1.25Gbps=625Mbps*2。

1.2 RGMII

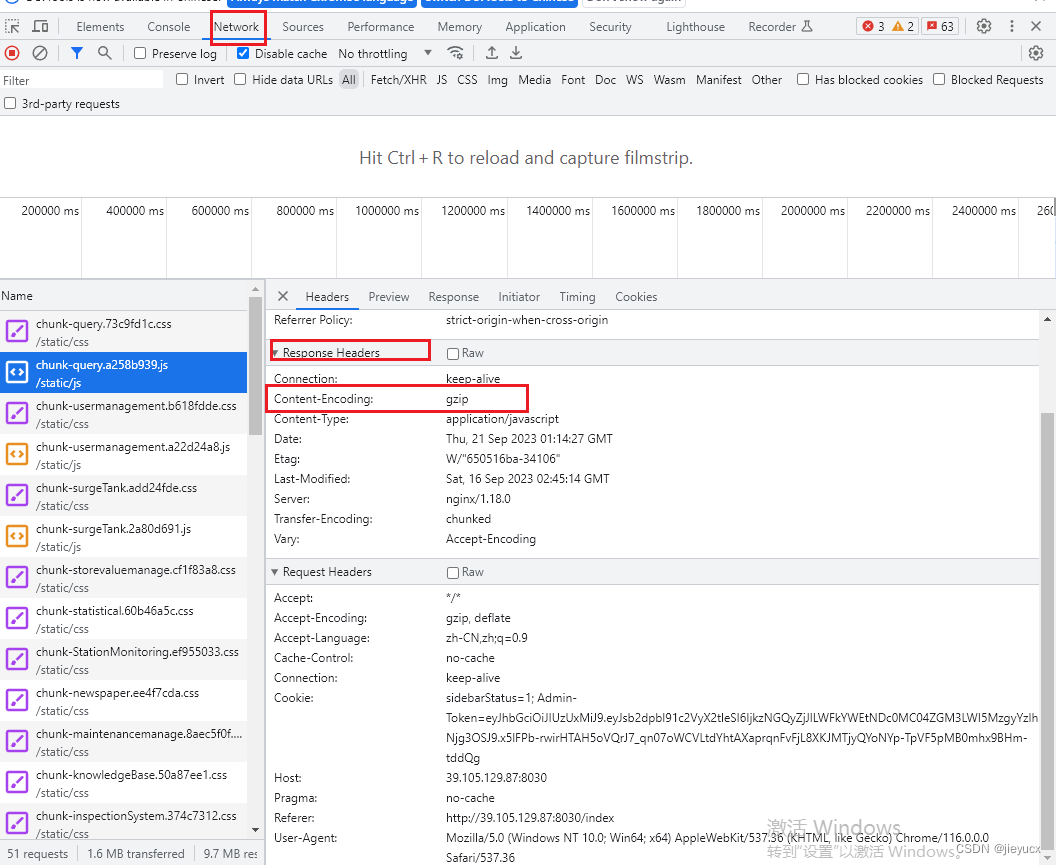

Reduced Gigabit Media Independent Interface (RGMII) (Reduced GMII)是最常见的接口,因为它支持PHY层的10 Mbps,100 Mbps和1000 Mbps连接速度。RGMII使用4-bit宽发送和接收数据通路,每个数据通路都有自己的源同步时钟。所有发送数据和控制信号源同步到TX_CLK,与此同时所有接收数据和控制信号源同步到RX_CLK。

所有速度模式中,TX_CLK始终由MAC提供时钟源,而RX_CLK始终由PHY提供时钟源。在1000 Mbps模式下,TX_CLK和RX_CLK为125 MHz,用Dual Data Rate (DDR)信令。

10 Mbps和100 Mbps模式下,TX_CLK和RX_CLK分别为2.5 MHz和25 MHz,使用上升沿Single Data Rate (SDR)信令。

1.2.1 RGMII I/O管脚时序

本小节从满足1000 Mbps模式下各种要求的角度触发,解决RGMII接口时序相关问题。1000 Mbps模式下,需要最多接口时序裕量,因而这是此处唯一需要考虑的情况。

125 MHz时,周期为8 ns,但由于两个沿都已使用,因而有效沿周期仅为4 ns。TX 和RX总线完全独立但时钟源同步,从而简化了时序。RGMII规范要求CLK在任意方向上从接收器的DATA延迟最短1.0 ns到最长2.6 ns。

换言之,MAC到PHY的TX_CLK必须延迟于输出到PHY输入和从PHY输出到MAC输入的RX_CLK。如在输出管脚处测得的那样,信号在每个方向的+/- -500 ps RGMII偏斜规范内同步传输。每个方向所需的最小延迟为1 ns,但建议将目标延迟定为1.5 ns到2 ns,以确保足够的时序裕量。

参考文章:

RGMII (intel.cn)

千兆网络PHY芯片 RTL8211E的实践应用

国产单端口1000M以太网收发(PHY)芯片介绍

phy芯片的千兆以太网的时钟传输方向

千兆网PHY自学笔记

【Datasheet】PHY KSZ9031千兆网络芯片

以太网学习(二)——PHY芯片

MII/GMII/RGMII知识学习。 - 知乎 (zhihu.com)

ARM处理器与PHY之间的MII,RMII,GMII,RGMII接口有什么区别

千兆网之RGMII & SGMII解析

[转]GMII/RGMII/SGMII/TBI/RTBI接口信号及时序介绍

车载以太网 - AVB vs EAVB vs TSN