Inclusive 和 Exclusive

- 一, 什么是cache的inclusive 和 exclusive

- 二,Inclusive 和 Exclusive cache示例

- 2.1 Inclusive cache

- 2.2 Exclusive cache

- 三, inclusive cache和 exclusive cache的比较

- 3.1 cache coherency

- 3.2 miss rate

- 3.3 cache capacity

- 四,Cortex-A55/Cortex-A53示例详解

- 五,参考文档

一, 什么是cache的inclusive 和 exclusive

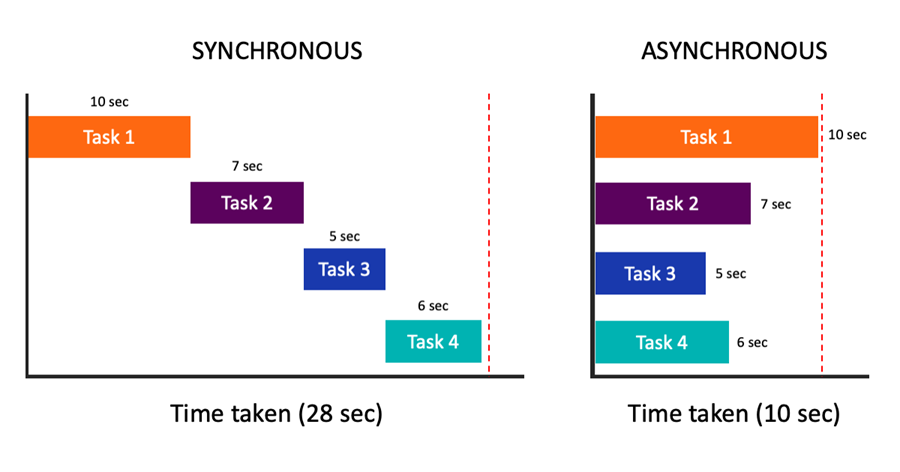

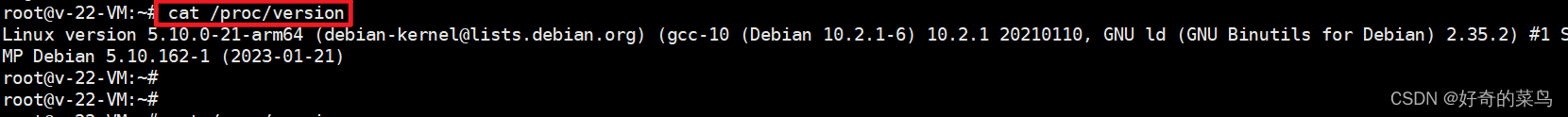

如下图所示,假设系统中有两级cache:L2 cache 和 L1 cache,

- Inclusive cache: L2包含了所有的L1里的所有有效数据。

- Exclusive cache: L1 和L2 的数据互斥,同样的一份数据不能同时存在于L1和L2。

二,Inclusive 和 Exclusive cache示例

2.1 Inclusive cache

假设系统中有两级cache,并且L2 和 L1 是inclusive关系。当CPU对一个地址进行读写时,cache controler会遵守如下规则:

- 如果在 L1 cache中hit,则直接将 L1 cache中的数据读取并返回给CPU。

- 如果在 L1 cache中miss,但在 L2 cache hit,则把 L2 cache中的数据读取并返回给CPU,同时会把该数据对应的cache line填充到L1 cache中。

- 如果规则2中的linefill 操作导致L1中发生cache line eviction,该eviction并不会影响到L2,因为被evict的cache line肯定在L2中有备份。

- 如果在 L1 或 L2 中均miss,则从主存中取出对应cache line 数据并对L1和 L2 都进行linefill。

- 如果L2 发生eviction,L2 cache会向 L1 cache发送invalidation请求,使L1中对应的cache line失效,以达到L1 和 L2的数据同步。

如上图所示,Inclusive cache有如下操作:

- (a) 假设 L1 和 L2 cache的初始状态为空。

- (b) CPU发送一个读 X 请求,在L1 和 L2 都会发生read miss,因此对应cache line从主存被linefill到 L1 和 L2。

- (c ) CPU又发出读 Y 请求,L1 和 L2 也将read miss ,cache line Y 也被linefill到 L1 和 L2 中。

- (d) 如果cache line X 必须从 L1 中被驱逐(evict),那么它只会从 L1 中移除,不会影响到L2。

- (e) 如果cache line Y 必须从 L2 中被驱逐(evict),为了保证inclusive policy,它会向 L1 发送invalidation request, L1 会使cache line Y 失效。

2.2 Exclusive cache

假设系统中有两级cache,并且L2 和 L1 是exclusive关系。当CPU对一个地址进行读写时,cache controler会遵守如下规则:

- 如果在 L1 cache中hit,则直接将 L1 cache中的数据读取并返回给CPU。

- 如果在 L1 cache中miss,但在 L2 cache hit,则把 L2 cache中的数据读取并返回给CPU,同时会把该数据对应的cache line **移动(move)或者说是交换(exchang)**到L1 cache中,可以理解为把 L2的对应cache line移除,填充到L1 中,以保证exclusive。

- 如果规则2中的linefill 操作导致L1中发生cache line eviction,这个被驱逐的cache line会被填充到L2中,这是L2 发生linefill的唯一方式,所以也称 这样的L2 cache 为 victim cache,专门接收 L1 的victim cache line的cache。

- 如果在 L1 或 L2 中均miss,则从主存中取出对应cache line 数据并只对L1进行linefill,而不是L2。

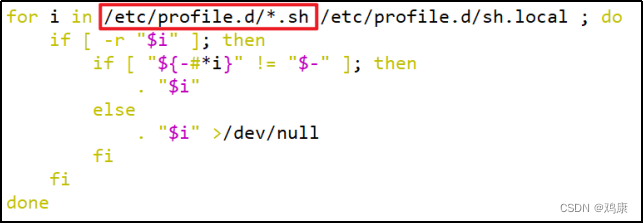

如上图所示,Exclusive cache有如下操作:

- (a) 假设 L1 和 L2 cache的初始状态为空。

- (b) CPU发送一个读 X 请求,在L1 和 L2 都会发生read miss,但是对应cache line只会从主存被linefill到 L1 。

- (c ) CPU又发出读 Y 请求,L1 和 L2 也将read miss ,cache line Y 也被linefill到 L1 。

- (d) 如果cache line X 必须从 L1 中被驱逐(evict),那么它会从 L1 中被evict 到L2。

三, inclusive cache和 exclusive cache的比较

事实上, inclusive cache 和 exclusive cache不存在绝对的性能优劣之分。在具体的约束条件下,系统架构是选择inclusive 还是exclusive ,一定是需要在各种考量因素之间做一个权衡。研究表明,或者说是经验值(a general rule-of-thumb):当L2 cache size 比 L1 cache size大于8 倍及以上时, inclusive 性能更好,反之,exclusive更好。

下面我们将从coherency、miss rate以及capacity的角度来简单分析二者性能上的差异。以下分析基于两层cache,且有多个私有L1以及共享一个L2的情况。

3.1 cache coherency

从维护数据一致性的角度,显然是inclusive cache更简单。因为L1里的数据是L2的一个子集,二者保存着一部分相同的数据。而在exclusive cache下,L1和L2里的内容是互斥的,在有多个私有L1以及共享一个L2的情况下,inclusive cache的coherency维护难度更低。

3.2 miss rate

我们考虑以下场景:

- 对于inclusive cache:L1发生了linfill,将cache line A填充到L1,同时也填充到L2。如果cache line A的填充导致了L2中cache line B被驱逐,而cache line B恰好在另一个L1中,且经常被使用,由于要保证inclusive,另一个L1也不得不将cache line B给invalidate。这就提高了L1的miss rate。

- 对于inclusive cache:如果L1 miss, L2 hit,则需要把L2 hit的line和L1中的一条line 交换。而inclusive cache面对这种情况,只需要直接从L2 拷贝 hit cache line到L1中。交换操作要比拷贝操作复杂,所以此时inclusive cache的总线负载和miss penalty更低。

- 在某个L1中发生miss,cache controler想看看所需的cache line是否存在于其他私有L1中。如果是inclusive cache,就无需遍历其他L1,只需在共享的L2中查找即可。这意味着inclusive cache的miss 延迟更短。

3.3 cache capacity

- 对于exclusive cache,cache的容量是层次结构中所有cache的总容量。而inclusive cache的内存容量由L2 cache决定的,如果L2 cache较小,则在inclusive cache中浪费的cache容量更多。

- 对于inclusive ,越大的cache可以使用越大的cache line,这可能减小二级cache tags的大小。而Exclusive需要L1和L2的cache line大小相同,以便进行替换。如果二级cahce是远远大于一级cache,并且cache data部分远远大于tag,省下的tag部分可以存放数据。

- exclusive方式可以存储更多数据,cache的空间利用率更高。

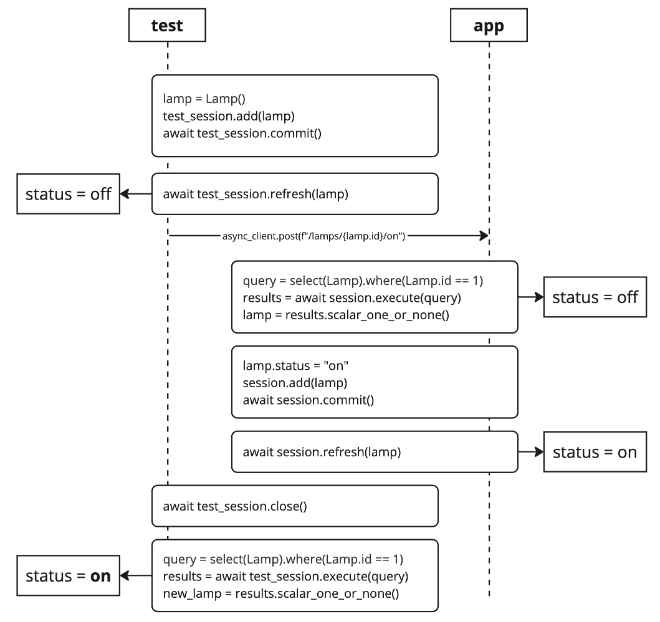

四,Cortex-A55/Cortex-A53示例详解

在ARM Cortex-A55和Cortex-A53中:

- L1 data cache 与 L2 cache,采用的是exclusive

- L1 instruction cache 采用的是inclusive。

如果Cortex-A55实现了L3 cache,L3 cache 的包含策略是动态的,取决于数据使用的行为方式:

如果只有一个core使用该数据,则使用exclusive策略,如果数据在多个core间被分享,则使用inclusive策略。

假设一开始core0对某个数据进行读取,数据将分配到L1或者L2cache 中,而不是在L3 cache。当该数据从L2中被驱逐到L3时,L1和L2将不再保存该数据,如果core再次读取,该数据又会被交换到L1或者L2中,此时的策略还是exclusive。但是如果core1也开始读取该数据,策略将会变成inclusive,core0和core1的L1或者L2中,以及L3都会保存该数据,以便数据在各个core之间共享。

此外,cache的包含策略一般是架构规定好的,软件层无法对其进行配置。

五,参考文档

https://en.wikipedia.org/wiki/Cache_inclusion_policy

https://zhuanlan.zhihu.com/p/159473930

https://blog.csdn.net/zgcjaxj/article/details/114970728

https://people.csail.mit.edu/emer/media/papers/2010.12.micro.tla.pdf

https://arstechnica.com/civis/threads/inclusive-or-exclusive-which-cache-architecture-you-consider-better.668596/

https://forums.anandtech.com/threads/inclusive-or-exclusive-which-cache-architecture-you-consider-better.1091585/