4、UART接收器

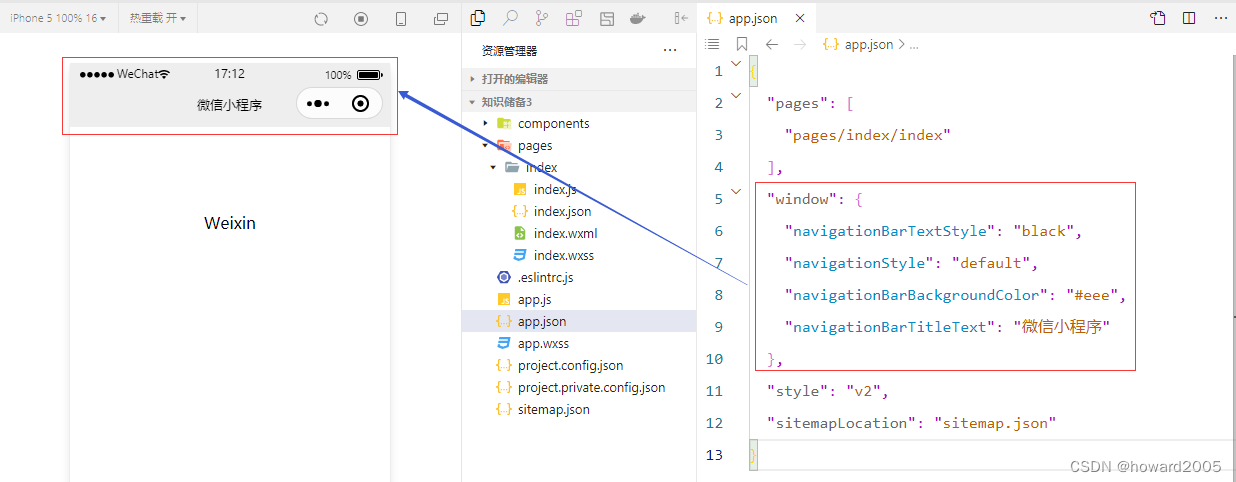

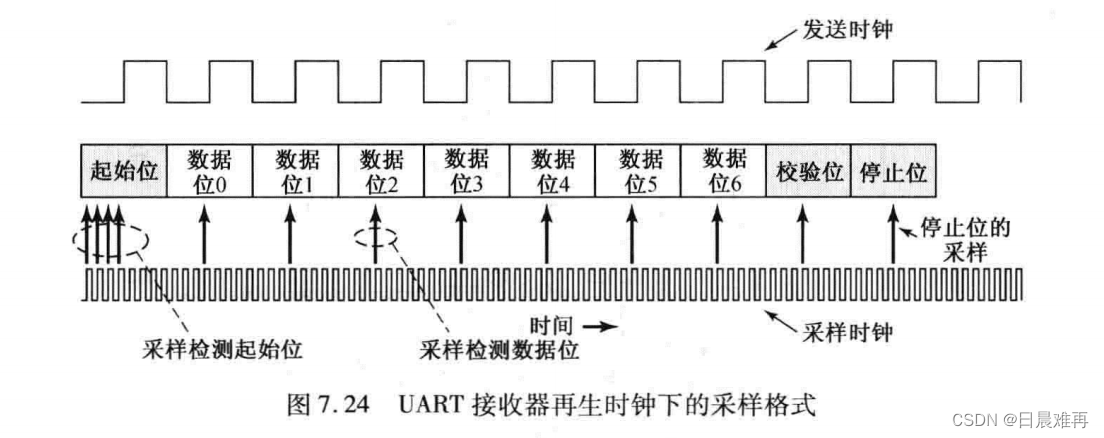

UART接收器负责接收串行比特流,去除起始位和停止位,并以并行格式将数据保存到与主机数据总线相连的寄存器里。接收器无法获得发送时钟,因此尽管数据以标准比特率到达,但数据未必与接收主机内的时钟同步。同步问题可以用同步器等方法解决,数据的采集可以使用一个更高频率的本地时钟进行采样。为保证采样是在比特时间的中间进行,应对Sample_clock时钟周期进行计数,如下图所示。采样方法必须保证:(1)能够检测到起始位到达;(2)能够采样到8个数据位;(3)能够把采样数据送到本地总线。

虽然可以采用更高的采样频率,但本例中Sample_clock的频率定为(已知)发送时钟频率的8倍。这可以保证Sample_clock前沿与起始位之间的少许差异不会影响采样,因为只需在起始位对应的比特时间之内采样完成即可。具体来说,就是当串行输入被采样为低电平后表示起始位到来,而后将再进行三次采样增加可信度,在此后的连续数据位都将在比特时间的中间附近被采样(即控制两次采样间隔时间是比特时间),这是通过数据通路中的计数器来实现的。

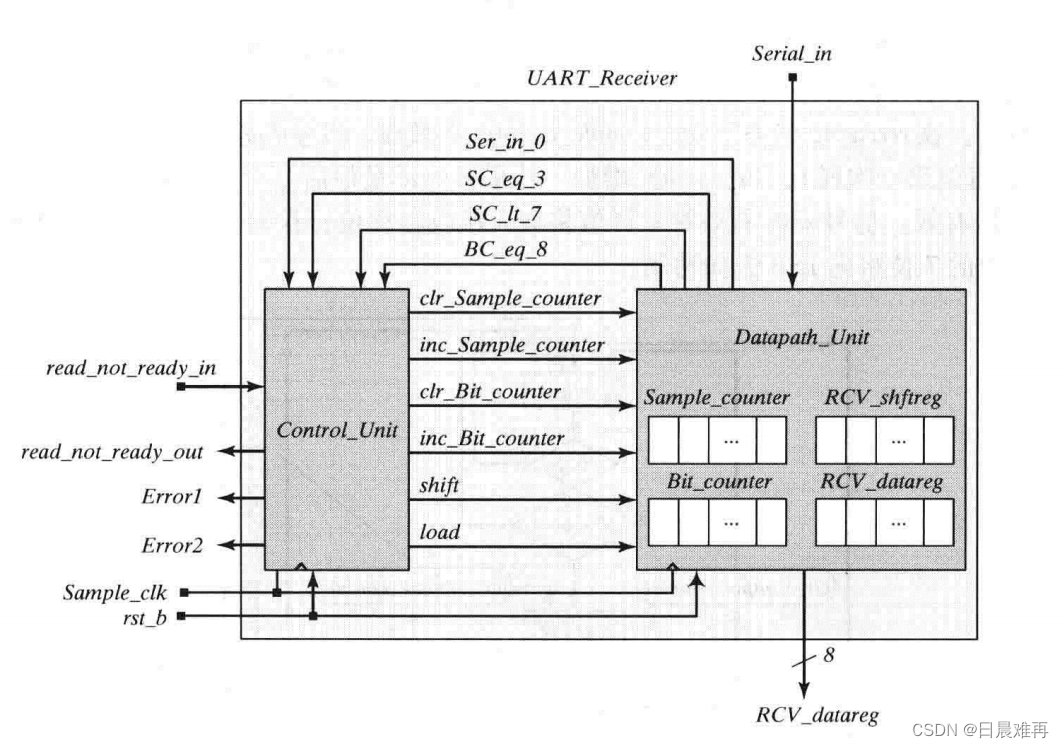

下图给出了接收器的内部框图,包括控制单元和数据通路,可以看到其中控制单元和主机之间的接口信号,已经控制单元和数据通路之间的控制信号与状态信号。

控制单元的输入信号及其作用:

read_not_ready_in:表示主机未准备好接收。

Ser_in_0:当Serial_in = 0时有效,是由数据通路提供的状态信号。

SC_eq_3:当Sample_counter = 3时有效,是由数据通路提供的状态信号。

BC_er_8:当Sample_count < 7时有效,是由数据通路提供的状态信号。

Sample_counter:对两次采样间隔进行计数。

Bit_counter:计数已采样的数据位数。

控制单元的输出信号及其作用:

read_not_ready_out:表示接收机已接收到8位数据。

clr_Sample_counter:控制数据通路的Sample_counter计数器清零。

inc_Sample_counter:控制数据通路的Sample_counter计数值加1。

clr_Bit_counter:控制数据通路的Bit_counters计数器清零。

inc_Bit_counter:控制数据通路的Bit_counters计数值加1。

shift:控制数据通路的RCV_shftreg向LSB方向移位。

load:控制数据通路的RCV_shftreg数据传送到RCV_datareg。

Error1:最后一个数据位采样结束后主机还没有准备好接收数据时有效。

Error2:停止位丢失时有效。

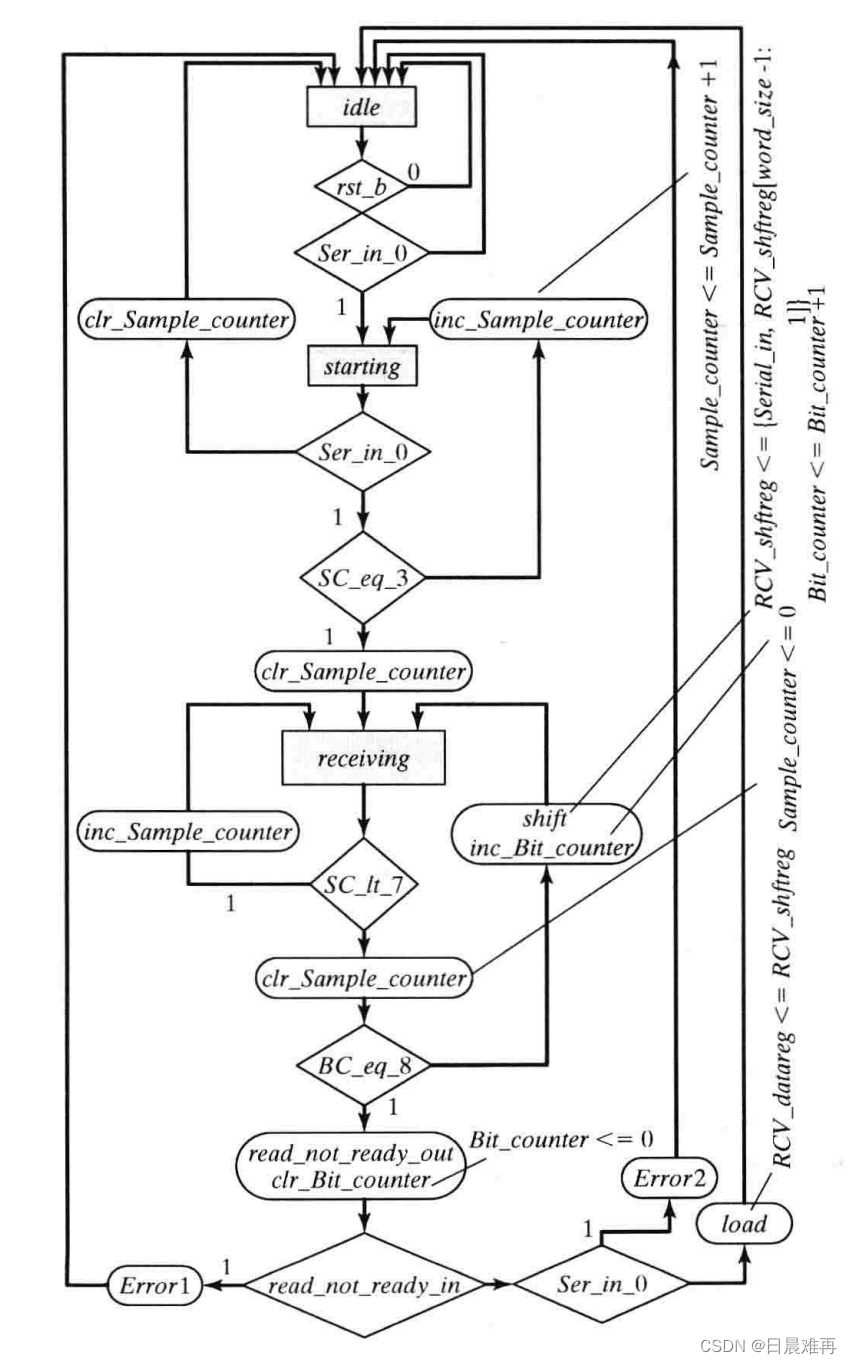

接收器控制器状态机ASMD如下图所示。该状态机包括idle、starting和receiving三个状态。状态之间的转移由Sample_clk来同步。低有效的同步复位输入rst_b使状态机进入idle状态,直到状态信号Ser_in_0变为高电平(串行输入为0)后状态机进入starting状态。在starting状态下,状态机重复采样Serial_in以确认是否是有效起始位。在Sample_clock的下一个有效沿,clr_Sample_counter和inc_Sample_counter需根据采样值确认是增加计数值还是清零:若接下来的连续三次采样值均为0,则认定为有效起始位,状态机转移到receiving状态并将给出clr_Sample_counter信号控制Sample_counter清零。在receiving状态下inc_Sample_counter将控制Sample_counter计数值增加以进行8个时钟周期的计时,对每个有效比特,在其比特时间的中间采样,总共采样7位数据位,1位校验位,Bit_counter增加。若采样的不是校验位,则inc_Bit_counter和shift持续有效。信号shift有效时,串行输入将载入接收器的移位寄存器RCV_shftreg的MSB位,且寄存器最左边的7位将向LSB方向移动。

module UART_RCVR #(parameter word_size = 8, half_word = word_size / 2)(output [word_size - 1 : 0]RCV_datareg,output read_not_ready_out,Error1, Error2,input Serial_in,read_not_ready_in,Sample_clk,rst_b

);wire Ser_in_0, SC_eq_3, SC_lt_7, BC_eq_8,clr_Sample_counter, inc_Sample_counter,clr_Bit_counter, inc_Bit_counter,shift, load;Control_Unit M0(read_not_ready_out, Error1, Error2, clr_Sample_counter,inc_Sample_counter, clr_Bit_counter, inc_Bit_counter,shift, load, read_not_ready_in, Ser_in_0, SC_er_3,SC_lt_7, BC_er_8, Sample_clk, rst_b);Datapath_Unit M1(RCV_datareg, Ser_in_0, SC_eq_3, SC_lt_7, BC_eq_8, Serial_in,clr_Sample_counter, inc_Sample_counter, clr_Bit_counter,inc_Bit_counter, shift, load, Sample_clk, rst_b);endmodulemodule Control_Unit #(parameter word_size = 8, half_word = word_size / 2,Num_state_bits = 2)(output reg read_not_ready_out,Error1, Error2, clr_Sample_counter,inc_Sample_counter, clr_Bit_counter, inc_Bit_counter,shift, loadinput read_not_ready_in, Ser_in_0, SC_er_3,SC_lt_7, BC_er_8, Sample_clk, rst_b

);localparam idle = 2'b00,starting = 2'b01,receiving = 2'b10;reg [word_size - 1 : 0] RCV_shftreg;reg [Num_state_bits - 1 : 0] state, next_state;always@(posedge Sample_clk)if(rst_b == 0)state <=idle;elsestate <= next_state;always@(*)beginread_not_ready_out = 0;clr_Sample_counter = 0;clr_Bit_counter = 0;inc_Sample_counter = 0;inc_Bit_counter = 0;shift = 0;Error1 = 0;Error2 = 0;load = 0;next_state = idle;case(state)idle: if(Ser_in_0 == 1)next_state = starting;elsenext_state = idle;starting: if(Ser_in_0 == 0)beginnext_state = idle;clr_Sample_counter = 1;endelse if(SC_eq_3 == 1)beginnext_state = receiving;clr_Sample_counter = 1;endelse beginnext_state = starting;inc_Sample_counter = 1; endreceiving: if(SC_lt_7 == 1)begininc_Sample_conter = 1;next_state = receiving;endelse beginclr_Sample_counter = 1;if(!BC_eq_8)beginnext_state = receiving; shift = 1;inc_Bit_counter = 1; endelse beginnext_state = idle;read_not_ready_out = 1;clr_Bit_counter = 1;if(read_not_ready_in == 1) Error1 = 1;else if(Ser_in_0 == 1)Error2 = 1;elseLoad = 1;endenddefault: next_state = idle;endcase end

endmodulemodule Datapath_Unit #(parameter word_size = 8, half_word = word_size / 2,Num_counter_bits = 4)(output reg [word_size - 1 : 0] RCV_datareg,output Ser_in_0,SC_eq_3, SC_lt_7, BC_eq_8,input Serial_in, clr_Sample_counter, inc_Sample_counter, clr_Bit_counter,inc_Bit_counter, shift, load, Sample_clk, rst_b

);reg [word_size - 1 : 0] RCV_shftreg;reg [Num_counter_bits - 1 : 0] Sample_counter;reg [Number_counter_bits : 0] Bit_counter;assign Ser_in_0 = (Serial_in == 0);assign BC_eq_8 = (Bit_counter == word_size);assign SC_lt_7 = (Sample_counter < word_size - 1);assign SC_eq_3 = (Sample_counter == half_word - 1);always@(posedge Sample_clk)if(rst_b == 0)beginSample_counter <= 0;Bit_counter <= 0;RCV_datareg <= 0;RCV_shftreg <= 0;endelse beginif(clr_Sample_counter == 1)Sample_counter <= 0;else if(inc_Sample_counter == 1)Sample_counter <= Sample_counter + 1;if(clr_Bit_counter == 1)Bit_counter <= Bit_counter;else if(inc_Bit_counter == 1)Bit_counter <= Bit_counter + 1;if(shift == 1)RCV_shftreg <= {Serial_in, RCV_shftreg[word_size - 1 : 1]};else if(load == 1)RCV_datareg <= RCV_shftreg;end

endmodule以上内容来源于《Verilog HDL高级数字设计》,有删改