名称:基于FPGA的数字钟具有校时闹钟报时功能

软件:Quartus

语言:VHDL

要求:

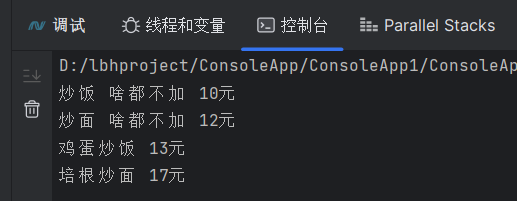

1、计时功能:这是数字钟设计的基本功能,每秒钟更新一次,并且能在显示屏上显示当前的时间。

2、闹钟功能:如果当前的时间与闹钟设置的时间相同,则扬声器发出闹音。

3、校时设置:用户可以通过功能键重新进行时间设置.精确校时时还可以对秒进行清零

4、整点报功能:如果当前时间为整点,则扬声器发出特定频率的整点报音。

5、闹铃设置:用户可以通过功能键完成任意时间的闹铃设置。

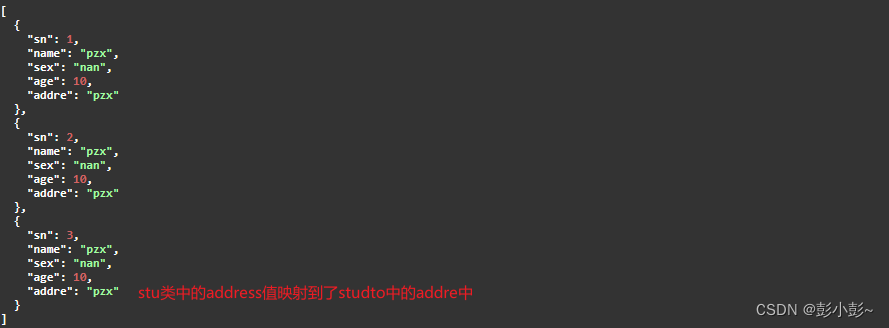

6、显示功能:正常计时状态6位数码管分别显示时、分、秒;校时状态显示时、分、闹钟设置状态显示当前闹钟的时分设置值。

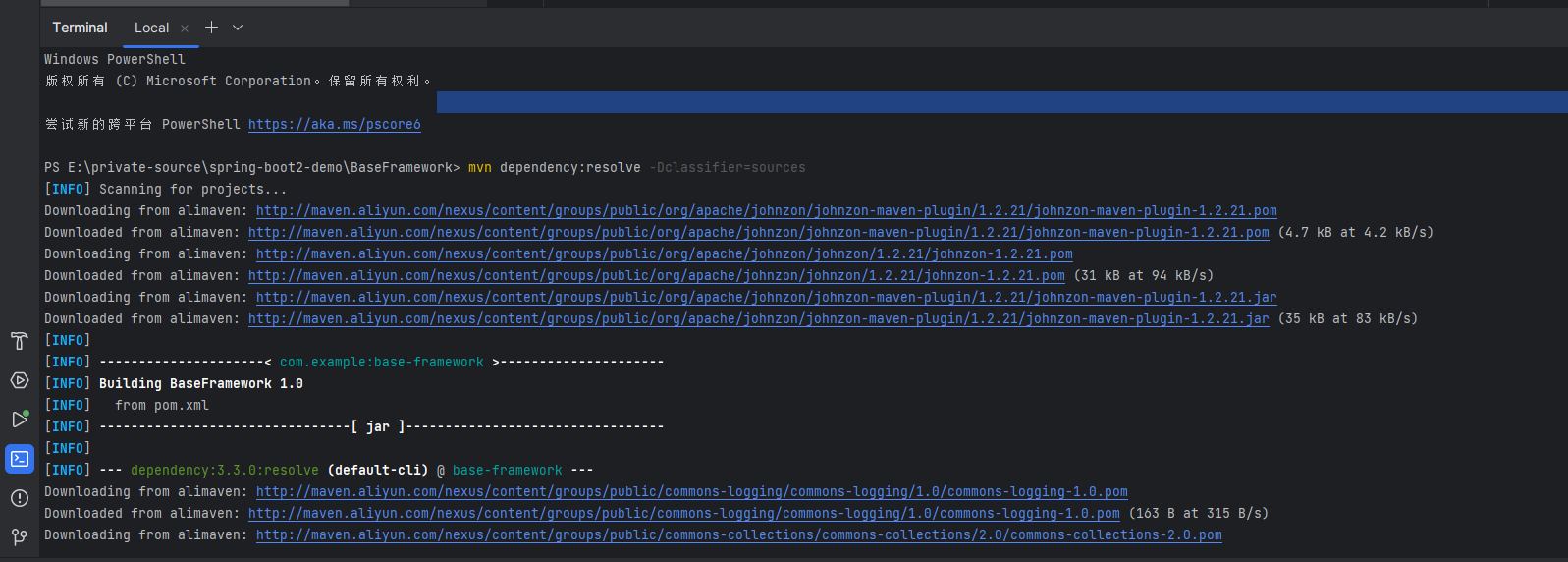

本课题要达到的目标是:在Quartus II软件上用VHDL语言编写相关的应用程序,利用FPGA完成数字时钟,使其功能基本得到实现。

部分代码展示

LIBRARY ieee;USE ieee.std_logic_1164.all; ENTITY Digital_clock ISPORT (clk_50M : IN STD_LOGIC;key_0 : IN STD_LOGIC;--模式设置按键--4'd0:计时,4'd1:闹钟,4'd3:温度key_1 : IN STD_LOGIC;--设置修改key_2 : IN STD_LOGIC;--修改确认key_3 : IN STD_LOGIC;--修改时分秒,闹钟关闭one_wire : INOUT STD_LOGIC; -- 传感器One-Wire总线bell_out : OUT STD_LOGIC;led_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--led显示当前模式bit_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管位选seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选); END Digital_clock; ARCHITECTURE behave OF Digital_clock IS --模块声明--响铃模块COMPONENT Bell ISPORT (clk_50M : IN STD_LOGIC;clear_alarm : IN STD_LOGIC;alarm_hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);alarm_minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);alarm_second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);bell_out : OUT STD_LOGIC);END COMPONENT;--闹钟模块COMPONENT alarm_clock ISPORT (clk_50M : IN STD_LOGIC;state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0);set_time_key : IN STD_LOGIC;confirm_key : IN STD_LOGIC;change_time_key : IN STD_LOGIC;alarm_hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);alarm_minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);alarm_second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT;--显示模块COMPONENT display ISPORT (clk : IN STD_LOGIC;state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0); temperature : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--温度alarm_hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);alarm_minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);alarm_second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);bit_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT;--设置模式COMPONENT set_mode ISPORT (clk_50M : IN STD_LOGIC;set_mode_key : IN STD_LOGIC;led_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);state_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;--分频模块COMPONENT fenping ISPORT (clk_50M : IN STD_LOGIC;clk_1Hz : OUT STD_LOGIC);END COMPONENT;--按键消抖COMPONENT key_jitter ISPORT (clkin : IN STD_LOGIC;key_in : IN STD_LOGIC;key_negedge : OUT STD_LOGIC);END COMPONENT;--计时模块COMPONENT jishi ISPORT (clk_50M : IN STD_LOGIC;clk_1Hz : IN STD_LOGIC;state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0);set_time_key : IN STD_LOGIC;confirm_key : IN STD_LOGIC;change_time_key : IN STD_LOGIC;hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT; COMPONENT ds18B20 is port( clk : in std_logic; --为50MHz dq : inout std_logic; LED : out std_logic; LED2 : out std_logic; LED3 : out std_logic; rst: in std_logic; temp_h:out std_logic_vector(7 downto 0); temp_l:out std_logic_vector(7 downto 0) ); end COMPONENT; SIGNAL state_mode : STD_LOGIC_VECTOR(3 DOWNTO 0);--当前模式,4'd0:计时,4'd1:闹钟,4'd2:跑表SIGNAL hour_time : STD_LOGIC_VECTOR(7 DOWNTO 0);--时SIGNAL minute_time : STD_LOGIC_VECTOR(7 DOWNTO 0);--分SIGNAL second_time : STD_LOGIC_VECTOR(7 DOWNTO 0);--秒SIGNAL alarm_hour_time : STD_LOGIC_VECTOR(7 DOWNTO 0);--闹钟时SIGNAL alarm_minute_time : STD_LOGIC_VECTOR(7 DOWNTO 0);--闹钟分SIGNAL alarm_second_time : STD_LOGIC_VECTOR(7 DOWNTO 0);--闹钟秒SIGNAL key_0_negedge : STD_LOGIC;--按键下降沿SIGNAL key_1_negedge : STD_LOGIC;--按键下降沿SIGNAL key_2_negedge : STD_LOGIC;--按键下降沿SIGNAL key_3_negedge : STD_LOGIC;--按键下降沿SIGNAL clk_1Hz : STD_LOGIC;--1Hz

本代码已在开发板验证,开发板资料见:

FPGA的数字钟校时闹钟报时VHDL_Verilog/VHDL资源下载

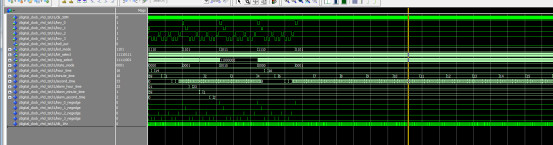

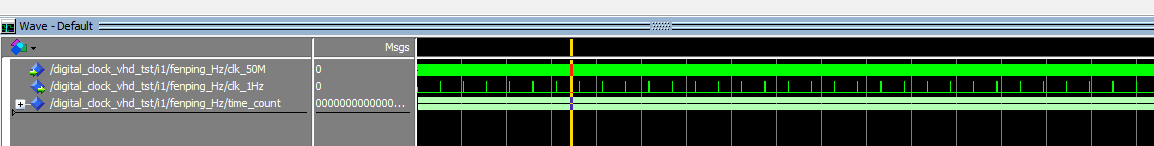

仿真图(文档点击可下载):

仿真图.doc

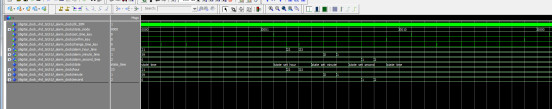

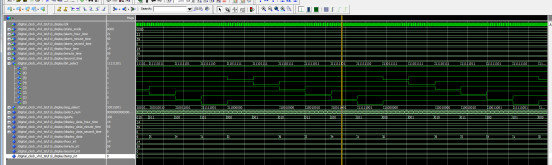

1. 分频模块

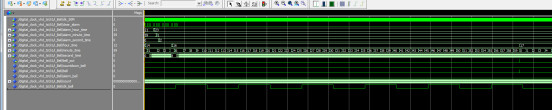

2. 设置闹钟模块

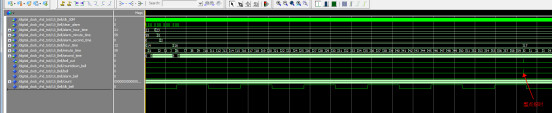

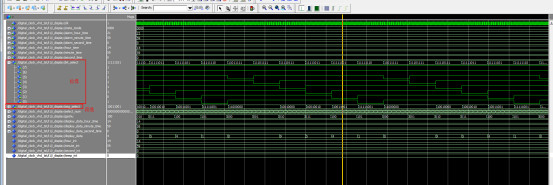

3. 响铃模块包括闹钟和整点报时

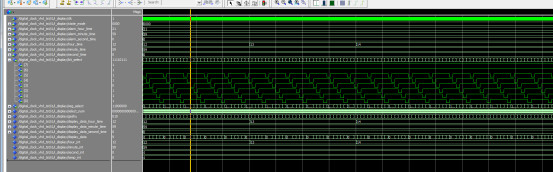

4. display显示模块

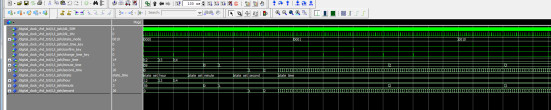

5. 计时模块

6. 模式设置模块

7. 按键模块

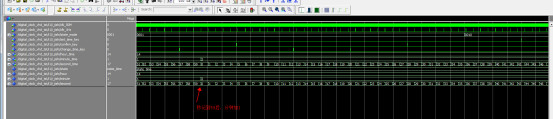

8. 整体仿真