名称:四位十进制频率计VHDL,DE1开发板验证

软件:Quartus

语言:VHDL

要求:

数字频率计设计要求

1、四位十进制数字显示的数学式频率计,其频率测量范围为10~9999khz,测量单位为kHz。

2、要求量程能够转换。即测几十到几百千(kHz)时,有小数点显示,前者显示小数点后2位,后者显示小数点后1位。

3、当输入的信号小于10kHz时,输出显示全0;当输入的信号大于9999kHz

时,输出显示全H。

代码下载:数字频率计名称:四位十进制频率计VHDL,DE1开发板验证(代码在文末付费下载)软件:Quartus语言:VHDL要求:数字频率计设计要求1、四位十进制数字显示的数学式频率计,其频率测量范围为10~999%khz,测量单位为kHz。2、要求量程能够转换。即测几十到几百千(kHz)时,有小数点显示,前者显示小数点后2位,后者显示小数点后1位。3、当输入的信号小于10kHz时,输出显示全0;当输入的信号大于99![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=185

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=185

FPGA代码资源网:hdlcode.com

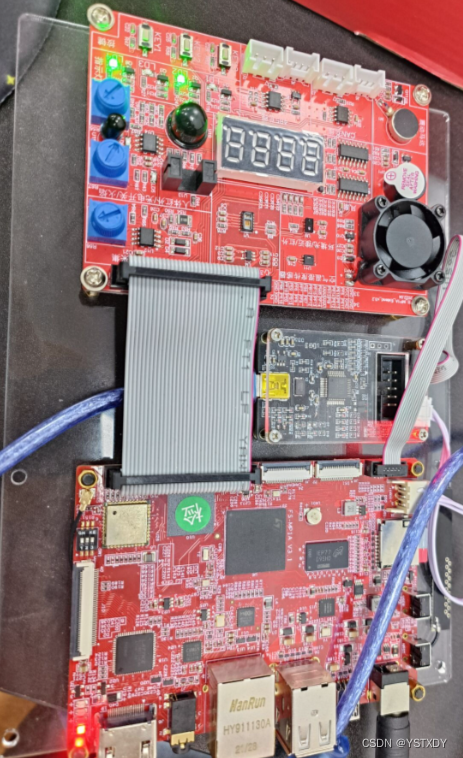

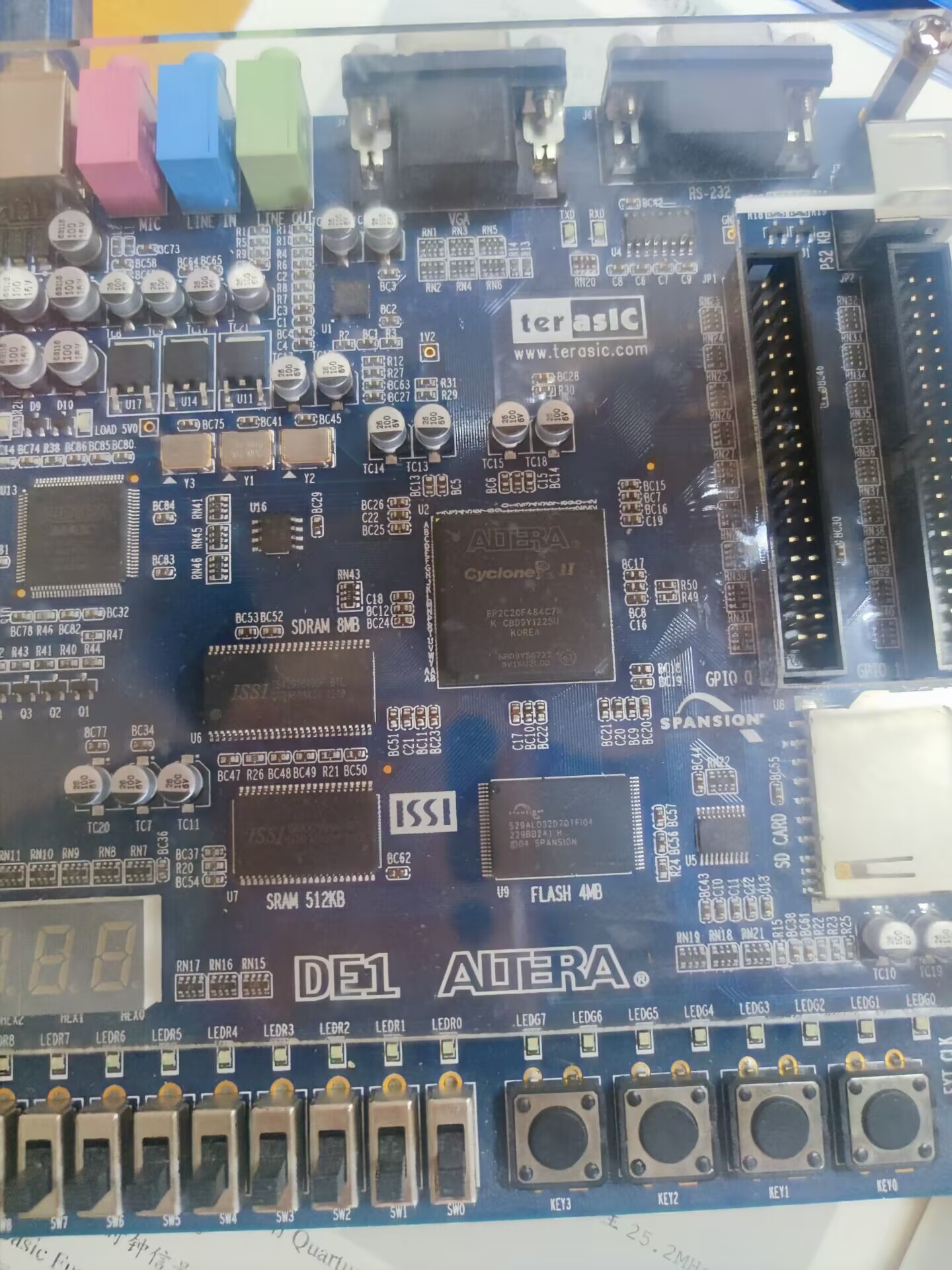

本代码已在DE1开发板验证,开发板照片如下:

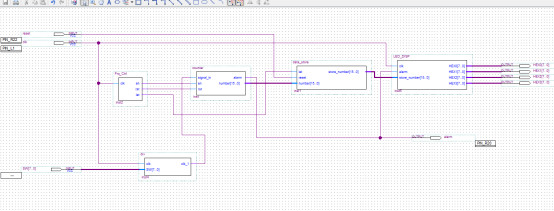

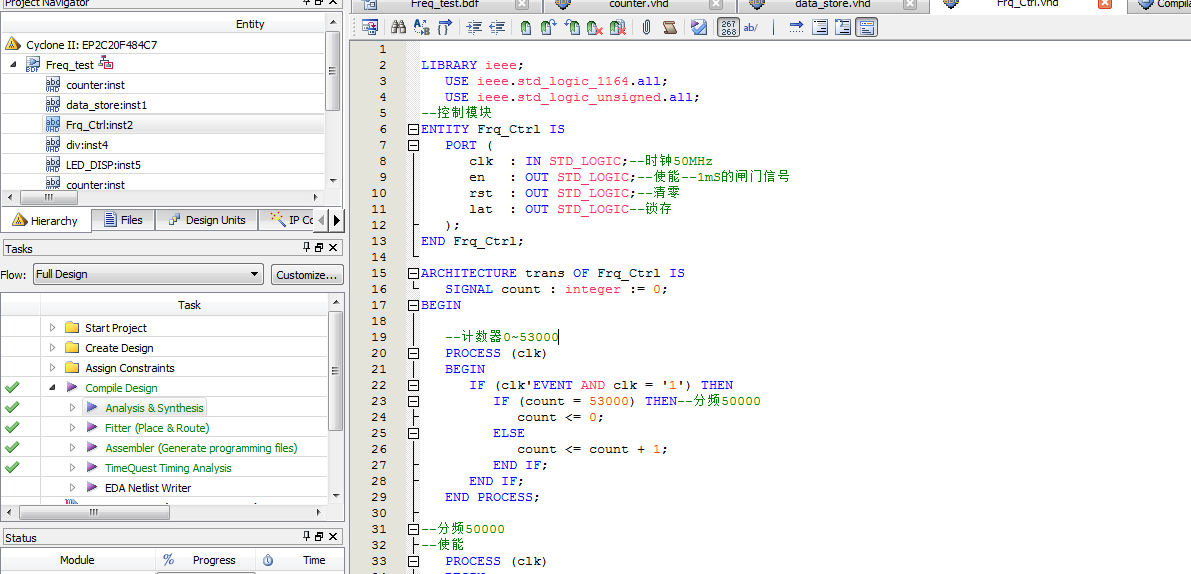

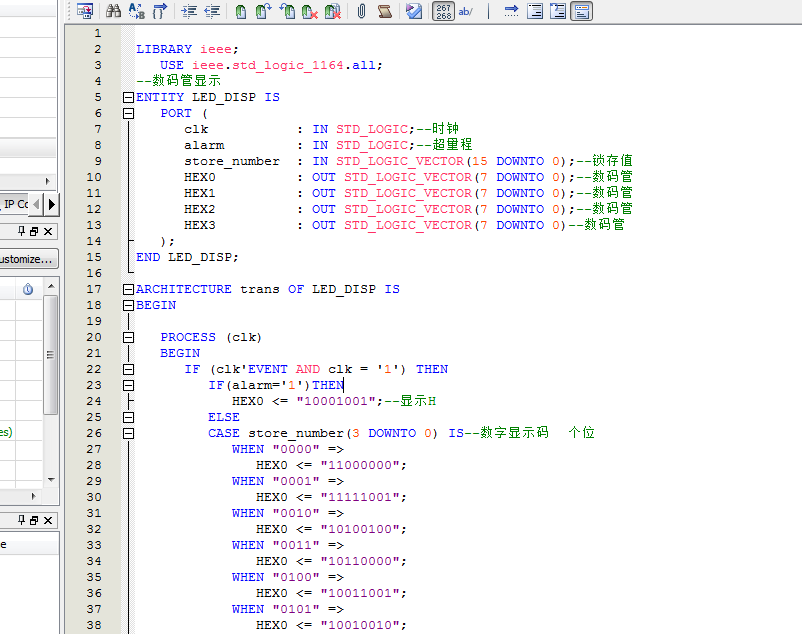

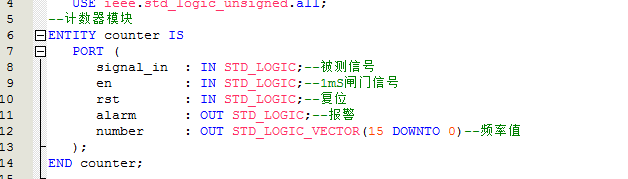

部分代码展示

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all; --计数器模块 ENTITY counter ISPORT (signal_in : IN STD_LOGIC;--被测信号en : IN STD_LOGIC;--1mS闸门信号rst : IN STD_LOGIC;--复位alarm : OUT STD_LOGIC;--报警number : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)--频率值); END counter; ARCHITECTURE trans OF counter ISSIGNAL num_0 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000";SIGNAL num_1 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000";SIGNAL num_2 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000";SIGNAL num_3 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; BEGINnumber <= (num_3 & num_2 & num_1 & num_0);--单位Hz--计数,计数1s内的信号周期数,计数值就是频率值PROCESS (signal_in, rst)BEGINIF (rst = '1') THENnum_0 <= "0000";num_1 <= "0000";num_2 <= "0000";num_3 <= "0000";alarm <= '0';ELSIF (signal_in'EVENT AND signal_in = '1') THENIF (en = '1') THEN--计数,低位都是9,则高位加1,低位清零,例如加到999,则变为1000IF (num_3 = "1001" AND num_2 = "1001" AND num_1 = "1001" AND num_0 = "1001") THENnum_0 <= "0000";num_1 <= "0000";num_2 <= "0000";num_3 <= "0000";alarm <= '1';--报警ELSIF (num_2 = "1001" AND num_1 = "1001" AND num_0 = "1001") THENnum_0 <= "0000";num_1 <= "0000";num_2 <= "0000";num_3 <= num_3 + "0001";--低位为9,则高位加1,低位清零alarm <= '0';ELSIF (num_1 = "1001" AND num_0 = "1001") THENnum_0 <= "0000";num_1 <= "0000";num_2 <= num_2 + "0001";--低位为9,则高位加1,低位清零num_3 <= num_3;alarm <= '0';ELSIF (num_0 = "1001") THENnum_0 <= "0000";num_1 <= num_1 + "0001";--低位为9,则高位加1,低位清零num_2 <= num_2;num_3 <= num_3;alarm <= '0';ELSEnum_0 <= num_0 + "0001";--低位加1num_1 <= num_1;num_2 <= num_2;num_3 <= num_3;alarm <= '0';END IF;END IF;END IF;END PROCESS;END trans;

设计文档(文档点击可下载):

1. 工程文件

2. 程序文件

3. 程序编译

4. 管脚分配

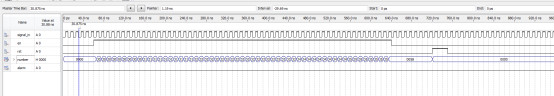

5. 仿真图

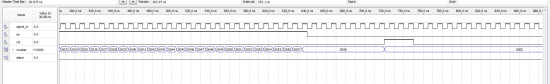

整体仿真图

计数器模块

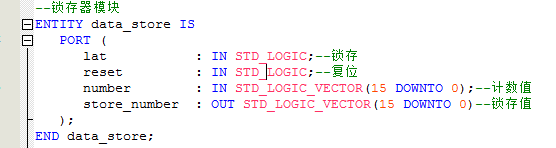

锁存器模块

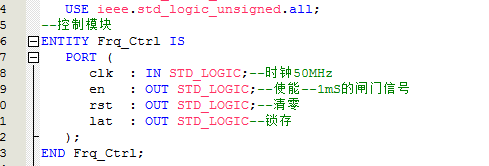

控制模块

产生闸门信号,清零信号,锁存信号

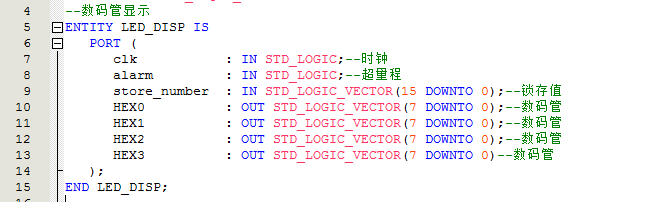

数码管显示模块

设计文档.doc

![[C++基础]-多态](https://img-blog.csdnimg.cn/8daed871137246219ff7dfe3c58fb5a3.png)