Zynq上的存储器接口

所有 Zynq-7000 AP芯片上的存储器接口单元包括一个动态存储器控制器和几个 静态存储器接口模块。动态存储器控制器可以用于 DDR3、DDR3L、DDR2 和 LPDDR2。 静态存储器控制器支持一个 NAND 闪存接口、一个 Quad-SPI 闪存接口、一个并行数 据总线和并行 NOR 闪存接口 [9]。

动态存储器接口

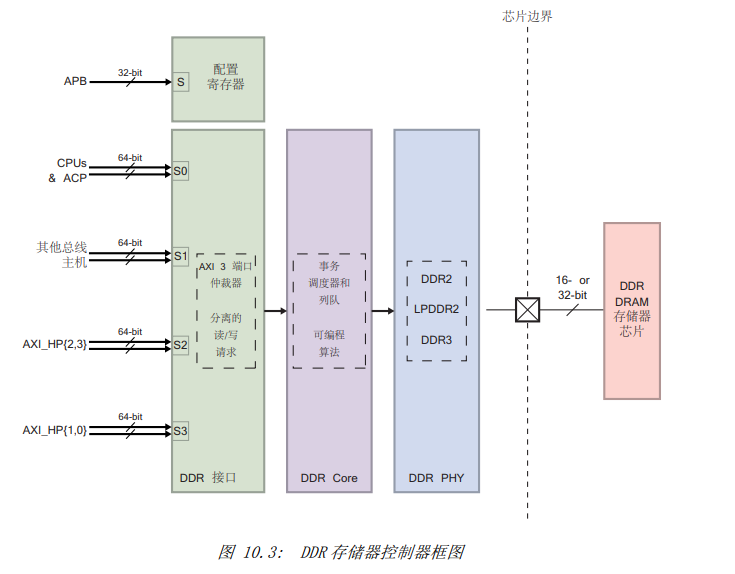

这个多协议双数据速率 (Double Data Rate,DDR)存储器控制器包括三个主要的模块:

一个核心存储器控制器和调度器 (DDRC) 、一个 AXI 存储器端口接口 (DDRI)和一个数字 PHY 以及控制器 (DDRP)[3]。

DDR 存储器控制器可以被配置为 16 位或 32 位模式,能在配置为 8、16 或 32 位 的单个块的 DRAM 存储器中访问 1GB 地址空间。也支持 EEC 存储器,但是只能以 32 位模式访问。

用 DDR3 的时候支持最大 1333Mb/s 的速度 [9]。

对 PS 和 PL 的共享存储器的共享访问是通过多端口 DDRI 来支持的,它具有四个 AXI 从机端口来满足这个要求 [9]:

• PL 通过两个专用的 64 位端口 (AXI_HP)来访问。

• 一个 64 位端口通过 L2 cache 控制器专用于 ARM CPU。这个端口可以被配置为 低延迟。

• 所有其他 AXI 主机通过中央互联共享剩下的端口。

每个 AXI 接口配备有专用的事务 FIFO。

DDRP PHY 处理从控制器来的读 / 写请求,并在 DDR 存储器的时序约束下,把请 求翻译为信号。PHY 用控制器来的信号创建内部信号,通过数字 PHY 传递到 DDR 引 脚上。最后通过 PCB 上的走线把 DDR 引脚接到实际的 DDR 芯片上。

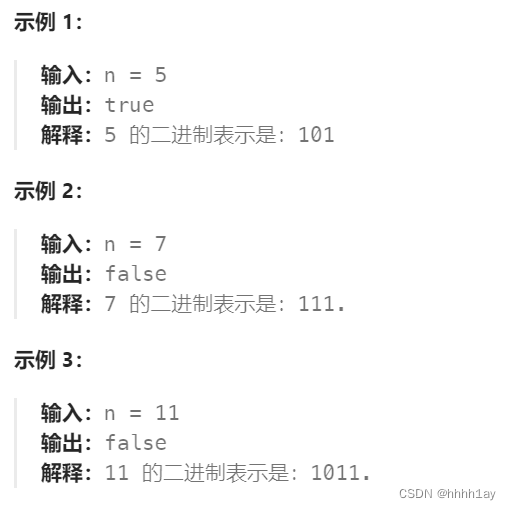

DDR3需要注意的时间参数

tRP :

预充电需要时间;

tRFC:(tRRC)

一次自刷新需要的时间

tRAS

激活行到预充电需要的时间

tRCD:

激活到读或写命令的延迟(激活行到列操作的时间),也是激活命令到读写操作的等待时间

CL读取潜伏

列选通潜伏期(读取指令到数据端口复现的时间)

CWL写入潜伏

写入指令到输入数据到数据端口DQ的时间

传输速率

如1066MT/S、1600MT/S等,该参数决定了DDR的最高数据传输速率。

不常用的:

tRC

Row Cycle Time,表示“SDRAM行周期时间”,它是包括行单元激活到预充电在内的整个过程所需要的最小的时钟周期数。tRC=tRAS+tRP。如果tRC的时间过长,会因在完成整个时钟周期后激活新的地址而等待无谓的延时,而降低性能。然而如果该值设置过小,在被激活的行单元被充分充电之前,新的周期就可以被初始化,也会导致数据丢失和损坏。

【精品博文】DDR扫盲——DDR3基础知识 (sohu.com)

MEMORY系列之“DDR参数”-电子工程专辑 (eet-china.com)

DDR与差分时钟

DDR基础原理介绍:差分时钟,同相,反相,两者差分交叉处也即差分值为0时读写信号,一个时钟周期可以上升沿下降沿都传输数据。相当两个时钟了。所以spi简单一个时钟信号不可能一个周期内同时锁定上升沿下降沿_什么是差分时钟-CSDN博客

DDR工作原理 - 我心狂野 - 博客园 (cnblogs.com) ←基本照搬这位爷。

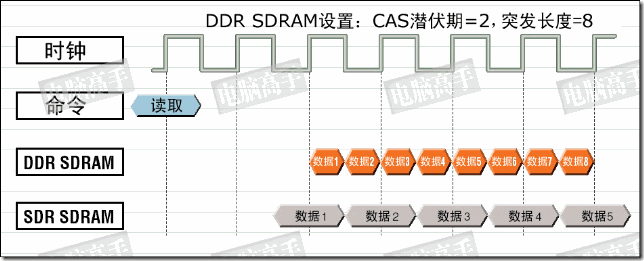

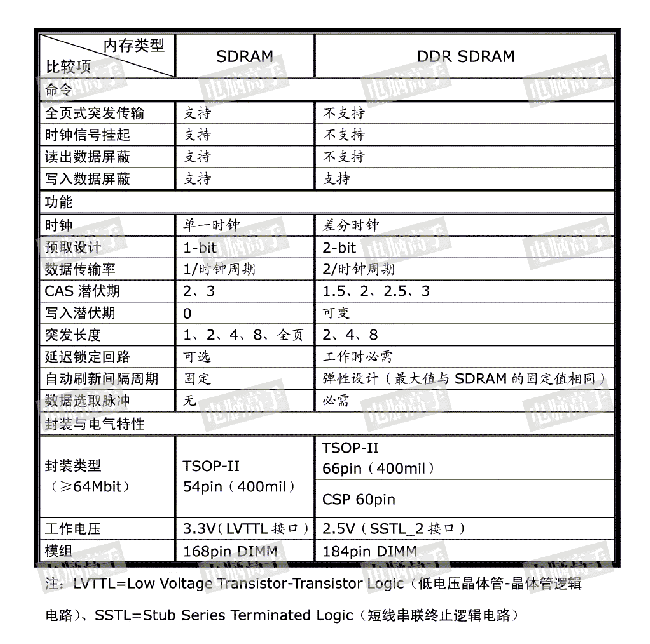

DDR的全称为Double Data Rate SDRAM,双倍速率的SDRAM,SDRAM在一个CLK周期传输一次数据,DDR在一个CLK周期传输两次数据,分别在上升沿和下降沿各传输一次数据,该概念称为预取,在描述DDR速度的时候一般使用MT/S单位,每秒多少兆次数据传输。

CK,CK#:

时钟信号线,DDR3的时钟线是差分时钟线,控制信号和地址信号都会在CK的上升沿和CK#的下降沿交叉处采集;但是数据在一个周期的上升沿和下降沿(一个时钟周期的同相反相交叉处有两个)都传输。

DDR的频率

核心频率就是内存的工作频率;DDR1内存的核心频率是和时钟频率相同的,到了DDR2和DDR3时才有了时钟频率的概念,就是将核心频率通过倍频技术得到的一个频率。数据传输频率就是传输数据的频率。DDR1预读取是2位,DDR2预读取是4位,DDR3预读取是8位。

DDR1在传输数据的时候在时钟脉冲的上升沿和下降沿都传输一次,所以数据传输频率就是核心频率的2倍。DDR2内存将核心频率倍频2倍所以时钟频率就是核心频率的2倍了,同样还是上升边和下降边各传输一次数据,所以数据传输频率就是核心频率的4倍。

DDR3内存的时钟频率是核心频率的4倍,所以数据传输频率就是核心频率的8倍了。

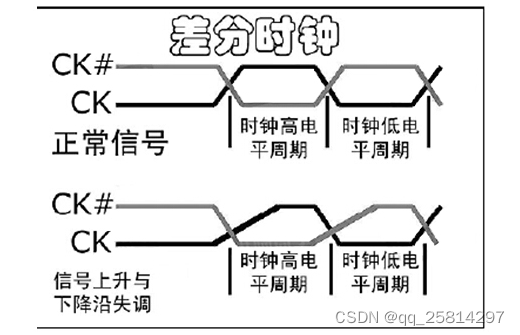

CLK#与正常CLK时钟相位相反,形成差分时钟信号。

而数据的传输在CLK与CLK#的交叉点进行,可见在CLK的上升与下降沿(此时正好是CLK#的上升沿)都有数据被触发,从而实现DDR。在此,我们可以说通过差分信号达到了DDR的目的,甚至讲CLK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说。之所以能实现DDR,还要从其内部的改进说起。

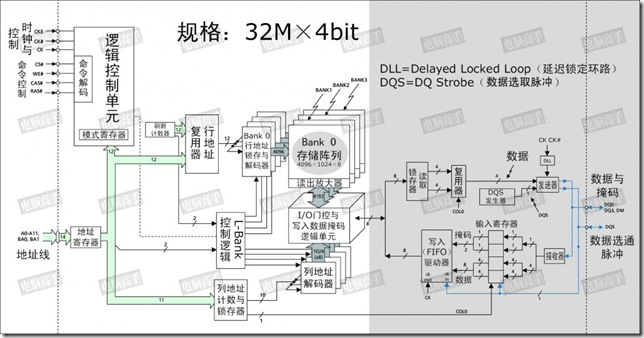

DDR内存芯片的内部结构图

这是一颗128Mbit的内存芯片,从图中可以看出来,白色区域内与SDRAM的结构基本相同,但请注意灰色区域,这是与SDRAM的不同之处。首先就是内部的L-Bank规格。SDRAM中L-Bank 存储单元的容量与芯片位宽相同,但在DDR SDRAM中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不能再套用讲解SDRAM时 “芯片位宽=存储单元容量” 的公式了。也因此,真正的行、列地址数量也与同规格SDRAM不一样了。

以本芯片为例,在读取时,L-Bank在内部时钟信号的触发下一次传送8bit(此芯片为4bit位宽)的数据给读取锁存器,再分成两路4bit数据传给复用器,由后者将它们合并为一路4bit数据流,然后由发送器在DQS的控制下在外部时钟上升与下降沿分两次传输4bit的数据给北桥。这样,如果时钟频率为100MHz,那么在I/O端口处,由于是上下沿触发,那么就是传输频率就是200MHz。

这种内部存储单元容量(也可以称为芯片内部总线位宽)=2×芯片位宽(也可称为芯片I/O总线位宽)的设计,就是所谓的两位预取(2-bit Prefetch),有的公司则贴切的称之为2-n Prefetch(n代表芯片位宽)。

SDRAM和DDR的一些差别

DDR SDRAM与SDRAM一样,在开机时也要进行MRS,不过由于操作功能的增多,DDR SDRAM在MRS之前还多了一EMRS阶段(Extended Mode Register Set,扩展模式寄存器设置),这个扩展模式寄存器控制着DLL的有效/禁止、输出驱动强度、QFC 有效/无效等。

差分时钟技术

差分时钟是DDR的一个重要且必要的设计,但大家对CLK#(CKN)的作用认识很少,很多人理解为第二个触发时钟,其实它的真实作用是起到触发时钟校准的作用。

由于数据是在CLK的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等原因,CLK上下沿间距可能发生变化,此时与其反相的CLK#(CKN)就起到纠正的作用(CLK上升快下降慢,CLK#则是上升慢下降快),如下图一所示。

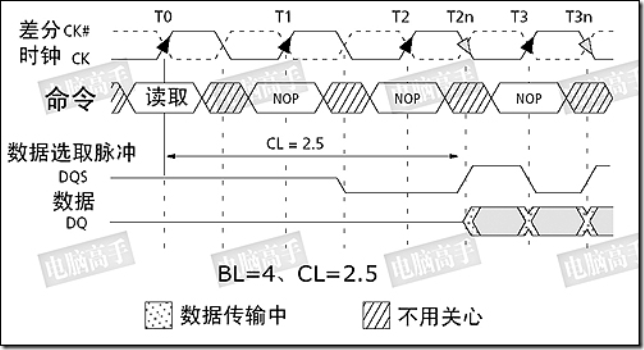

CLK#与正常CLK时钟相位相反,形成差分时钟信号。而数据的传输在CLK与CLK#的交叉点进行,可见在CLK的上升与下降沿(此时正好是CLK#的上升沿)都有数据被触发,从而实现DDR。

数据选取脉冲(DQS)

差分时钟、DQS与DQM - DDRx的关键技术介绍(上) - 知乎 (zhihu.com)

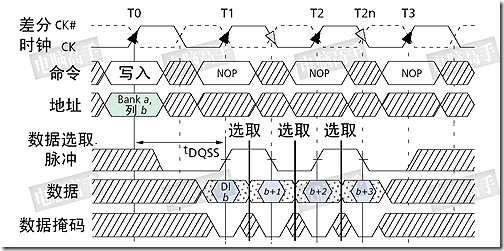

总结DQS:它是双向信号;读内存时,由内存产生,DQS的沿和数据的沿对齐;写入内存时,由外部产生,DQS的中间对应数据的沿,即此时DQS的沿对应数据最稳定的中间时刻。

DQS是DDR SDRAM中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。每一颗8bit DRAM芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由主控芯片发来的DQS信号,读取时,则由DRAM芯片生成DQS向主控发送。完全可以说,它就是数据的同步信号。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。

而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,数据真正出现在数据I/O总线上相对于DQS触发的时间间隔被称为tAC。

实际上,DQS生成时,芯片内部的预取已经完毕了,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。

由于是并行传输,DDR内存对tAC也有一定的要求,对于DDR266,tAC的允许范围是±0.75ns,对于DDR333,则是±0.7ns,其中CL里包含了一段DQS的导入期。

前文已经说了DQS是为了保证接收方的选择数据, DQS在读取时与数据同步传输,那么接收时也是以DQS的上下沿为准吗?

不,如果以DQS的上下沿区分数据周期的危险很大。

由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各I/O端口的出现时间可能有快有慢,会与DQS有一定的间隔,这也就是为什么要有一个tAC规定的原因。

而在接收方,一切必须保证同步接收,不能有tAC之类的偏差。

这样在写入时,芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应延后一定的时间,在DQS的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。

这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在DQS上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。

在写入时,以DQS的高/低电平期中部为数据周期分割点,而不是上/下沿,

但数据的接收触发仍为DQS的上/下沿。

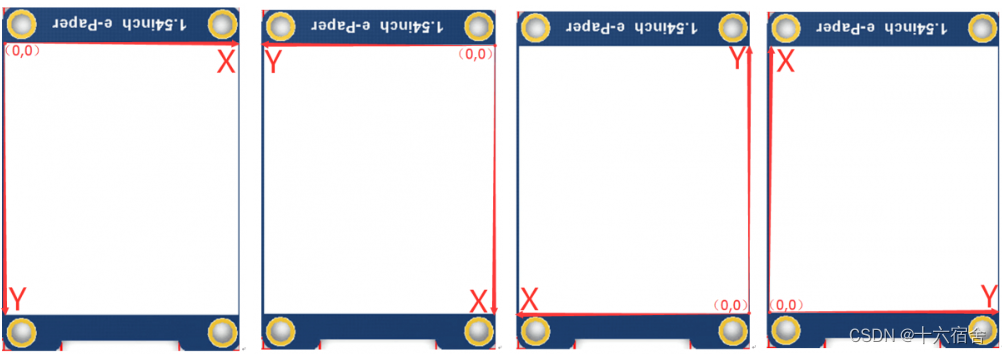

数据掩码技术(DQM)

不是DDR所特有的,但对于DDR来说也是比较重要的技术。

为了屏蔽不需要的数据,人们采用了数据掩码(Data I/O Mask,简称DQM)技术。通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

DQM由主控芯片控制,为了精确屏蔽一个P-Bank位宽中的每个字节,每个64bit位宽的数据中有8个DQM信号线,每个信号针对一个字节。这样,对于4bit位宽芯片,两个芯片共用一个DQM 信号线,对于8bit位宽芯片,一个芯片占用一个DQM信号,而对于16bit位宽芯片,则需要两个DQM引脚。SDRAM 官方规定,在读取时DQM发出两个时钟周期后生效,而在写入时,DQM与写入命令一样是立即生效,如下图三和四分别显示读取和写入时突发周期的第二笔数据被取消。