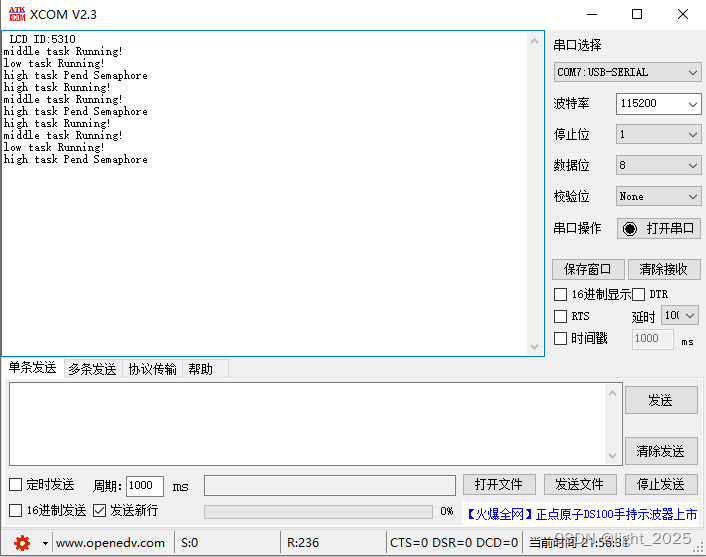

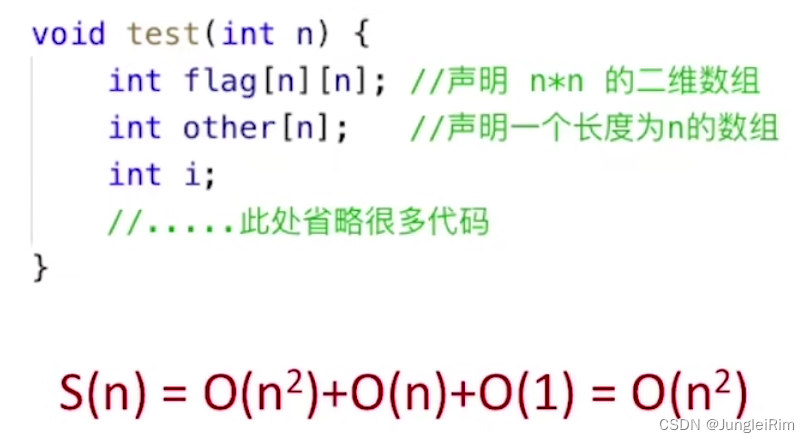

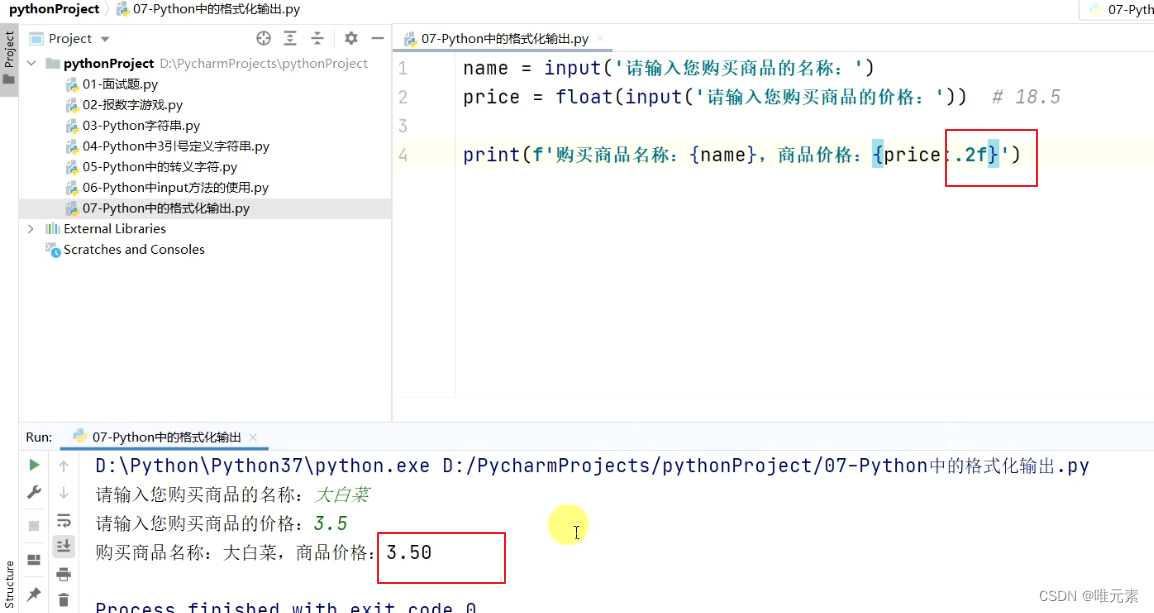

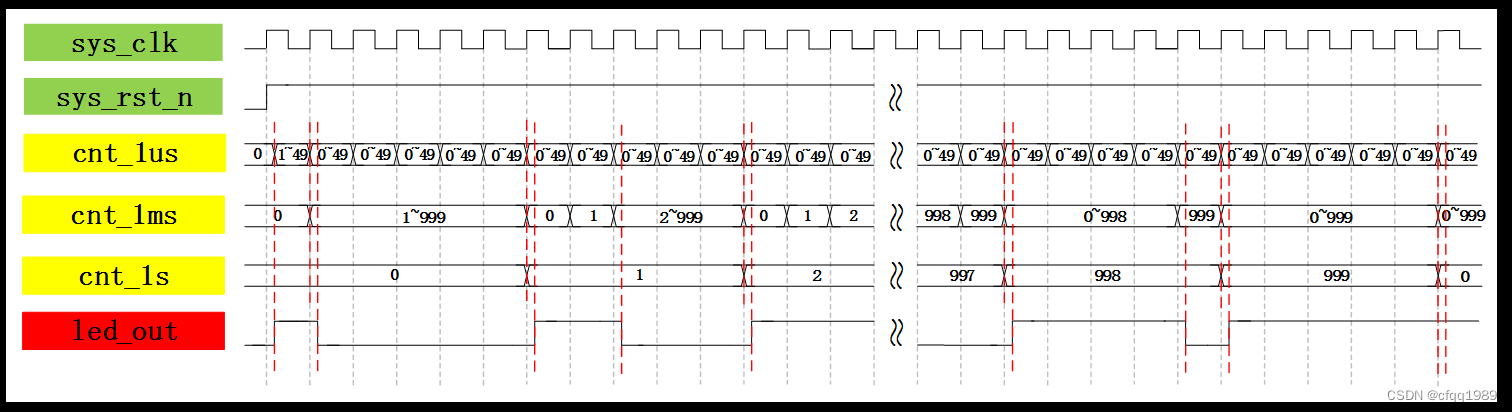

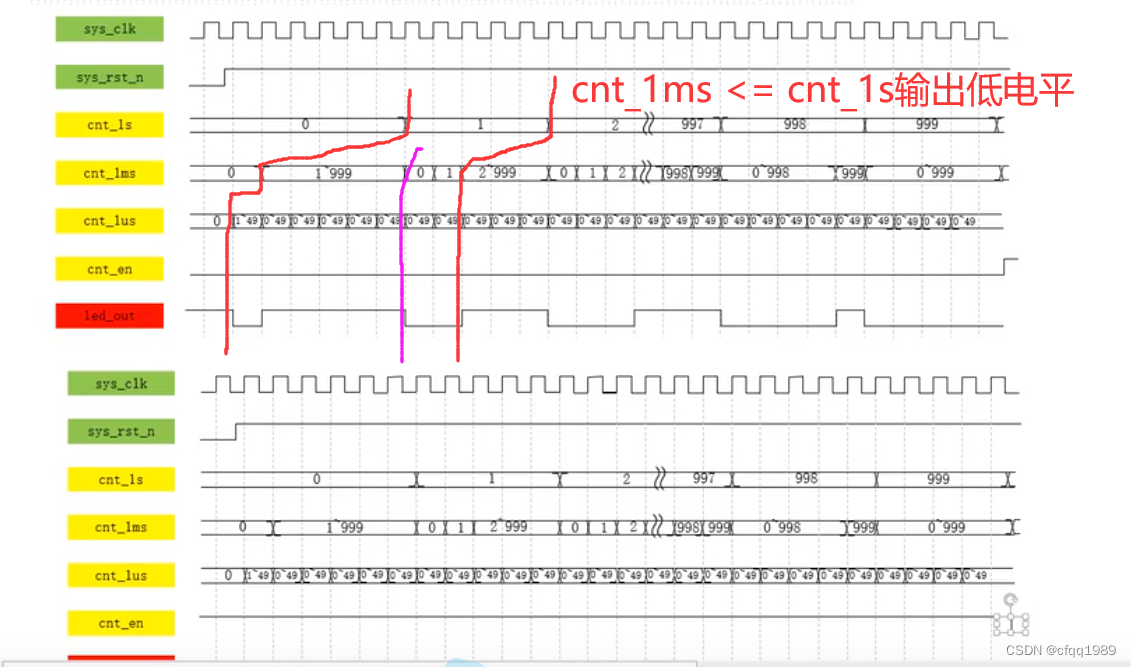

晶振50Mhz

1us 等于 计0~49

1ms等于 0~999us

1s等于 0~999ms

//led_outalways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次led_out <= 1'd0;end// cnt_en低电平 灯亮条件【1ms和1s比较值】else if((cnt_en == 1'b0 ) && (cnt_1ms <= cnt_1s) ||(cnt_en == 1'b1 ) && (cnt_1ms >= cnt_1s ))// s满,led_out <= 1'b1;else led_out <= 1'b0;assign led1_d15 = led_out;

//======================================================

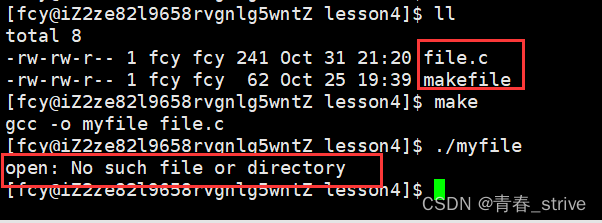

module sleep_led // 模块名字,参数,方法体

#(parameter CNT_1US_MAX = 6'd49 ,parameter CNT_1MS_MAX = 10'd999 ,parameter CNT_1S_MAX = 10'd999 )

(input FPGA_CLK_50M_b5,input reset_e8,input key1_k18,input key2_n17,input key3_n18,input key4_h17,

//output led1_d15,output led2_c15,output led3_a12,output led4_b12,output beep_h13 //【注】最后一个参数不加逗号

);

//【】以下是变量//reg [5:0] cnt_1us;// 50Mhz晶振, 0~49reg [9:0] cnt_1ms;reg [9:0] cnt_1s;reg [0:0] cnt_en;reg [0:0] led_out;//【】以下是方法体,FPGA的特性是程序都是并联运行。//assign {led1_d15,led2_c15,led3_a12,led4_b12} = {~key1_k18,~key2_n17,~key3_n18,~key4_h17}; //key1_k18 +key2_n17 + key3_n18 +key4_h17 ;//usalways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次cnt_1us <= 6'b0;// cnt_en <= 1'b0;endelse if(cnt_1us == CNT_1US_MAX)// 0~49cnt_1us <= 6'b0;else cnt_1us <= cnt_1us + 6'b1 ;//msalways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次cnt_1ms <= 10'd0;endelse if((cnt_1ms == CNT_1MS_MAX ) && (cnt_1us == CNT_1US_MAX))// ms满,cnt_1ms <= 10'd0;else if(cnt_1us == CNT_1US_MAX)cnt_1ms <= cnt_1ms + 10'd1 ;// ms加1//salways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次cnt_1s <= 10'd0;endelse if((cnt_1s == CNT_1S_MAX ) && (cnt_1ms == CNT_1MS_MAX) &&(cnt_1us == CNT_1US_MAX))// s满,cnt_1s <= 10'd0;else if((cnt_1ms == CNT_1MS_MAX)&&(cnt_1us == CNT_1US_MAX))cnt_1s <= cnt_1s + 10'd1 ;// s加1//======呼吸灯条件===================//cnt_enalways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次cnt_en <= 1'd0;endelse if((cnt_1s == CNT_1S_MAX ) && (cnt_1ms == CNT_1MS_MAX) &&(cnt_1us == CNT_1US_MAX))// s满,cnt_en <= ~cnt_en;else cnt_en <= cnt_en;//led_outalways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次led_out <= 1'd0;end// cnt_en低电平 灯亮条件【1ms和1s比较值】else if((cnt_en == 1'b0 ) && (cnt_1ms <= cnt_1s) ||(cnt_en == 1'b1 ) && (cnt_1ms >= cnt_1s ))// s满,led_out <= 1'b1;else led_out <= 1'b0;assign led1_d15 = led_out;endmodule//